Extensible 2.5-dimensional multi-core processor architecture

A multi-core processor and processor technology, applied to the architecture with multiple processing units, a variety of digital computer combinations, general-purpose stored program computers, etc., can solve the problem of increased chip physical design workload, increased tape-out costs, and design cycle Elongation and other issues, to achieve the effect of shortening the design cycle, improving speed and bandwidth, and improving reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

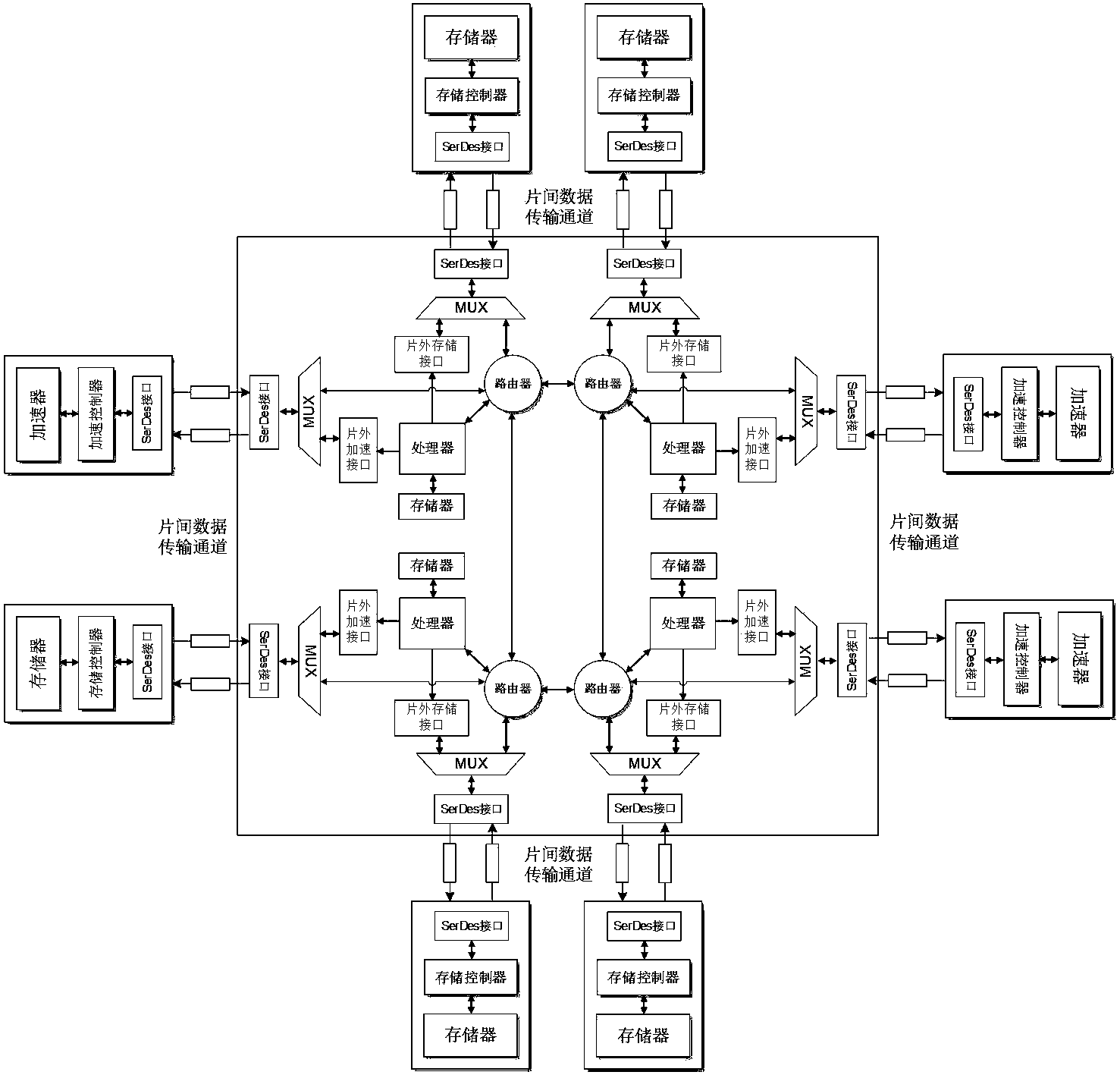

[0018] The present invention proposes a novel and expandable 2.5D multi-core processor architecture, which supports the three expansions of memory, accelerator and multi-core chip, and the respective implementation modes are described in detail below.

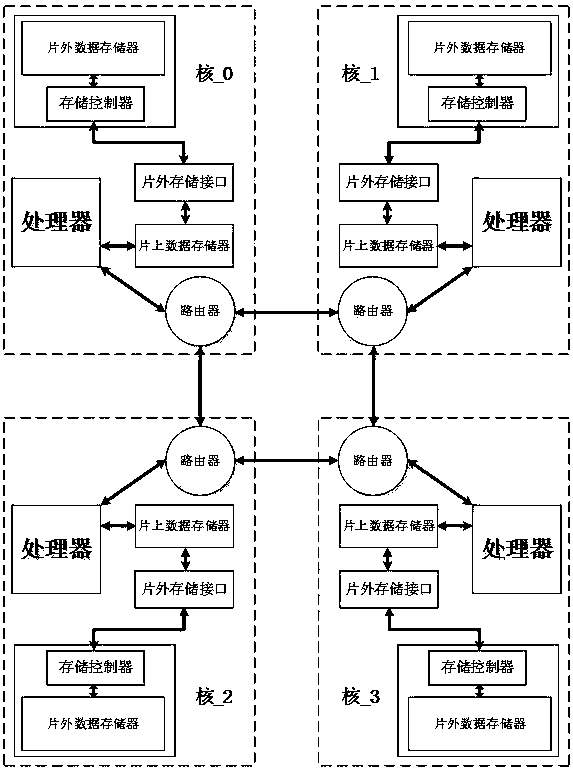

[0019] 2.5D storage expansion: First, as Figure 6 As shown, the software controls the multi-core expansion configurator to generate signals. On the one hand, the output of the vertical MUX is strobed with the off-chip storage interface. On the other hand, the address is generated according to the XY coordinates corresponding to the position in the two-dimensional grid topology where the router is located. , loaded into the router. Then, when the processor is working, when the off-chip storage interface module detects that the address of the pipeline load / store (loal / store) instruction falls into the address space of the local off-chip memory or receives the DMA configuration signal sent by the processor , the corresponding in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com