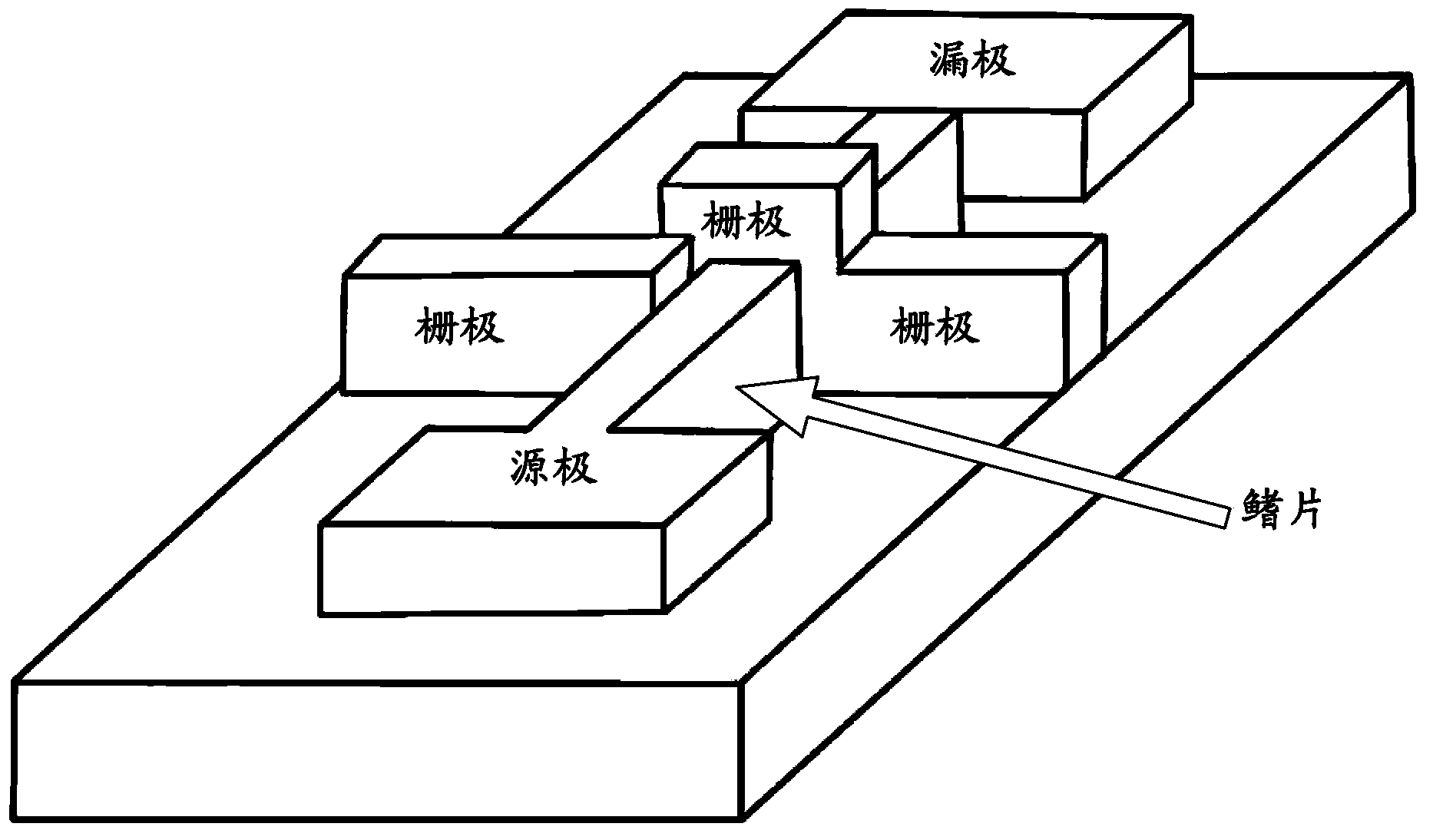

Semiconductor device and manufacturing method thereof

A semiconductor and transistor technology, applied in the field of semiconductor devices and their manufacturing, can solve problems such as deteriorating the performance of 3D transistors, and achieve the effects of improving performance and increasing space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

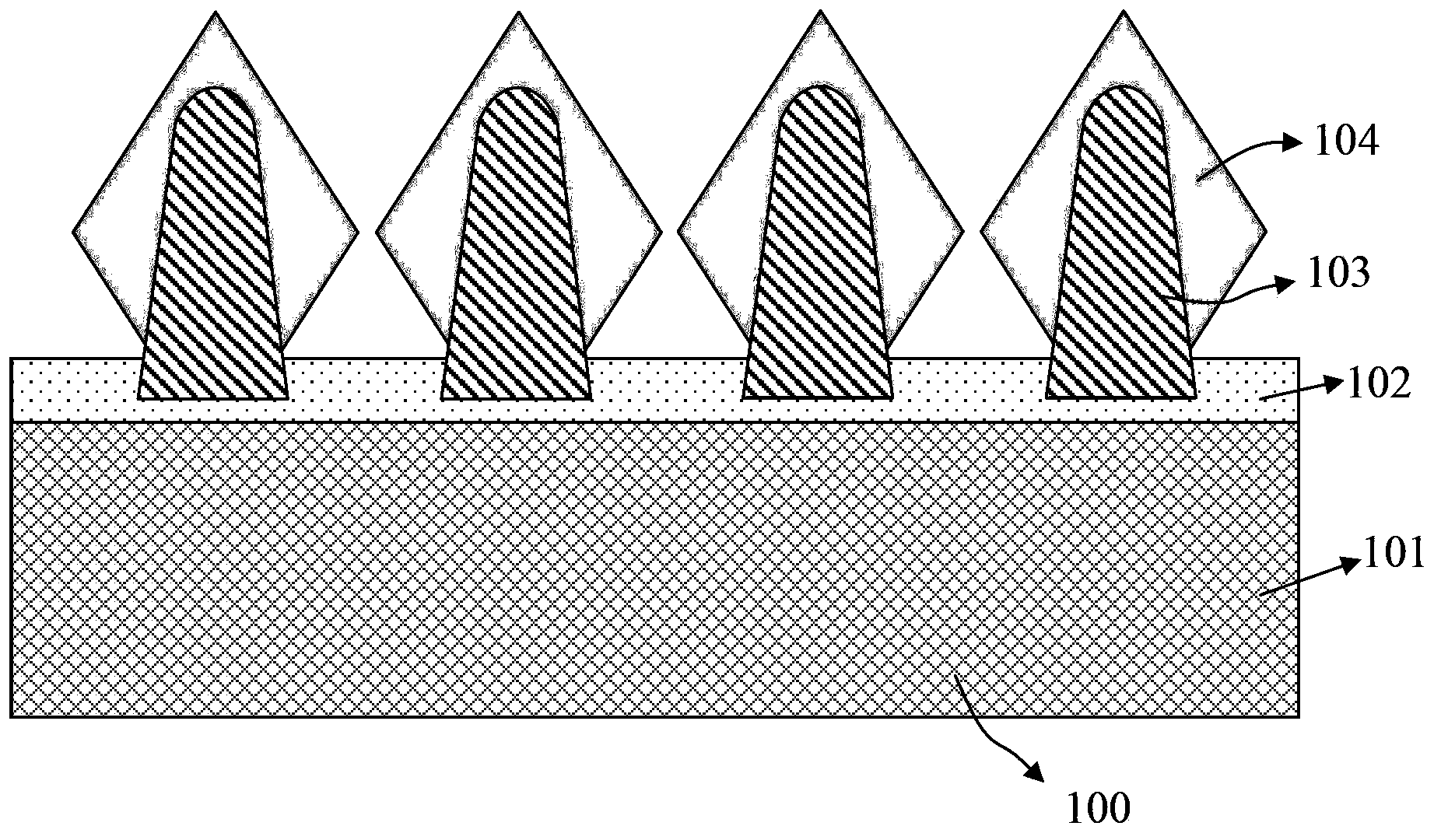

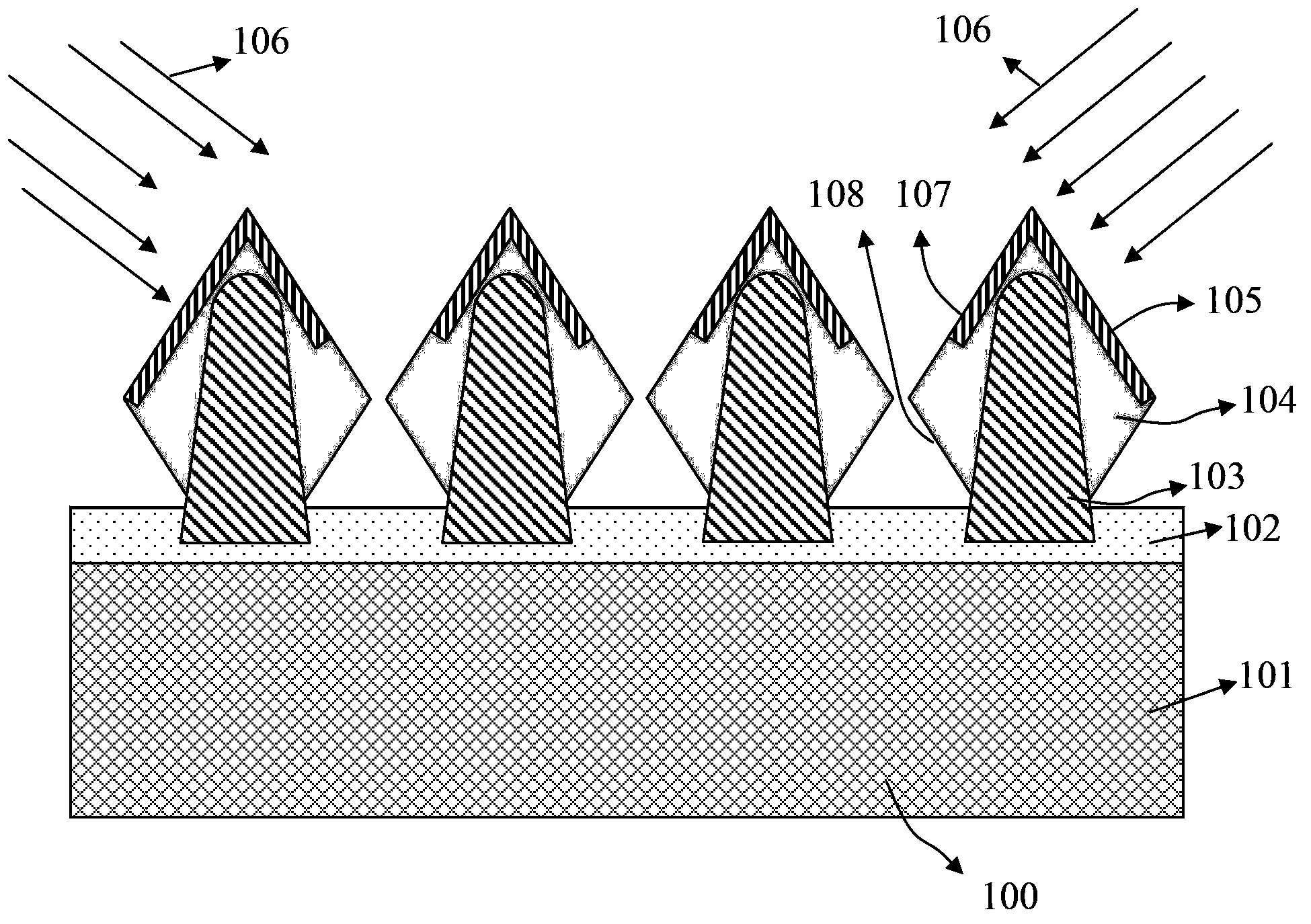

[0032] Various exemplary embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

[0033] It should be noted that the relative arrangements of components and steps, numerical expressions and numerical values set forth in these embodiments do not limit the scope of the present invention unless specifically stated otherwise. In addition, like numbers and letters denote like items in the following figures, so that once an item is defined in one figure, it does not require further discussion in subsequent figures.

[0034] The following description of the exemplary embodiments is illustrative only and in no way serves as any limitation of the invention and its application or use. Techniques known in the art may be applied to parts not particularly shown or described. In all examples shown and discussed herein, any specific values should be construed as illustrative only, and not as limiting. Therefore, other example...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com