Large-dynamic and high-precision programmable time delay device based on FPGA (field programmable gate array)

A high-precision, high-dynamic technology, applied in the electronic field, can solve the problems of small dynamic range, high precision, unfavorable system integration, etc., and achieve the effect of high integration, solving technical bottlenecks, and huge application space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The present invention is described in detail below in conjunction with accompanying drawing

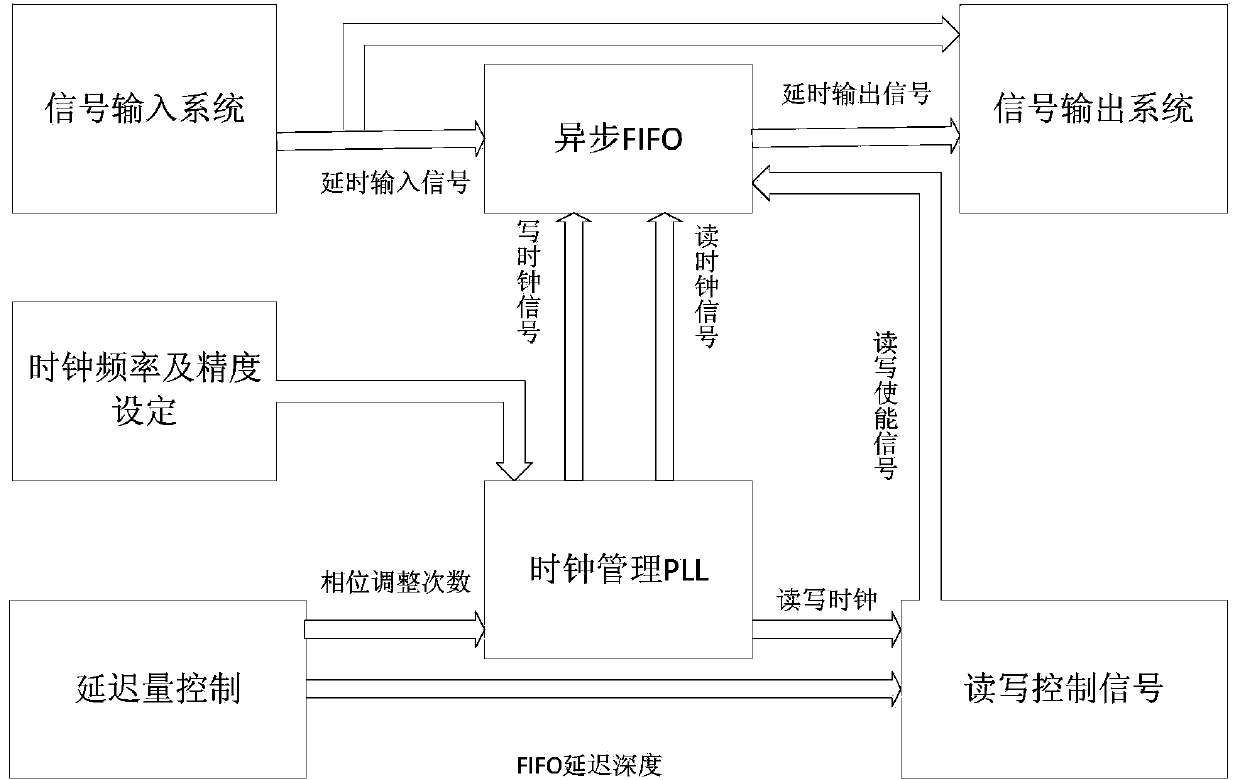

[0014] Such as figure 1 As shown, a large dynamic and high-precision programmable delay device based on FPGA is characterized in that the target signal is accurately delayed according to the delay function of the asynchronous FIFO with a phase difference between the read and write clocks, including clock frequency and precision settings. fixed module, delay control module, clock management PLL, read-write control signal module and asynchronous FIFO module; wherein, the output terminal of the clock frequency and precision setting module is connected to the input terminal of the clock management PLL; the output terminal of the delay control module is connected to The input terminal of the clock management PLL and the input terminal of the read-write control signal; the output terminal of the read-write control signal is connected to the input terminal of the asynchronous FIFO; th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More