Grid electrode forming method

A gate, two-gate technology, used in electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as instability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

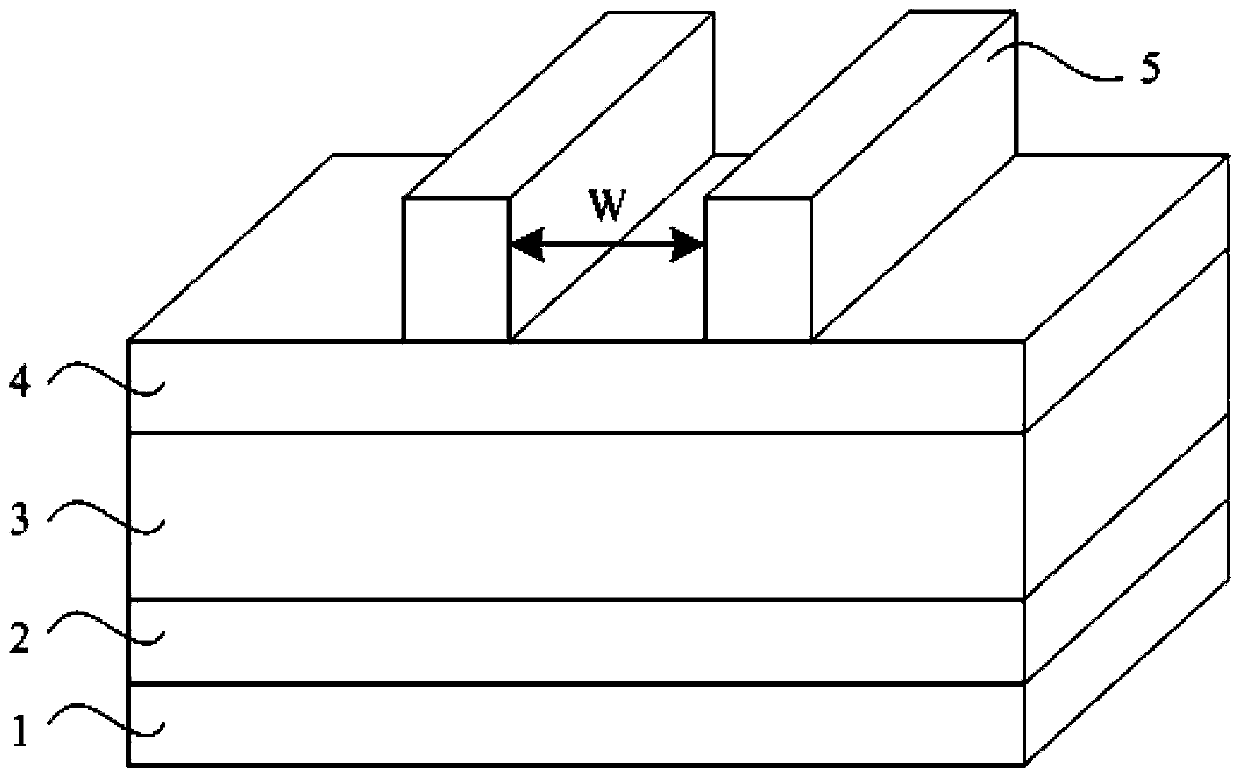

[0043] refer to Figure 7A , providing a substrate 110 ; forming a polysilicon layer 130 on the substrate 110 .

[0044] In a specific embodiment, an etch stop layer 120 is further formed between the substrate 110 and the polysilicon layer 130, and a first hard mask layer 141 and a first bottom layer are formed on the polysilicon layer 130. The anti-reflection layer 151 , the first bottom anti-reflection layer 151 is formed on the first hard mask layer 141 .

[0045] In a specific embodiment, the material of the substrate 110 is single crystal silicon, polycrystalline silicon, amorphous silicon or silicon-on-insulator.

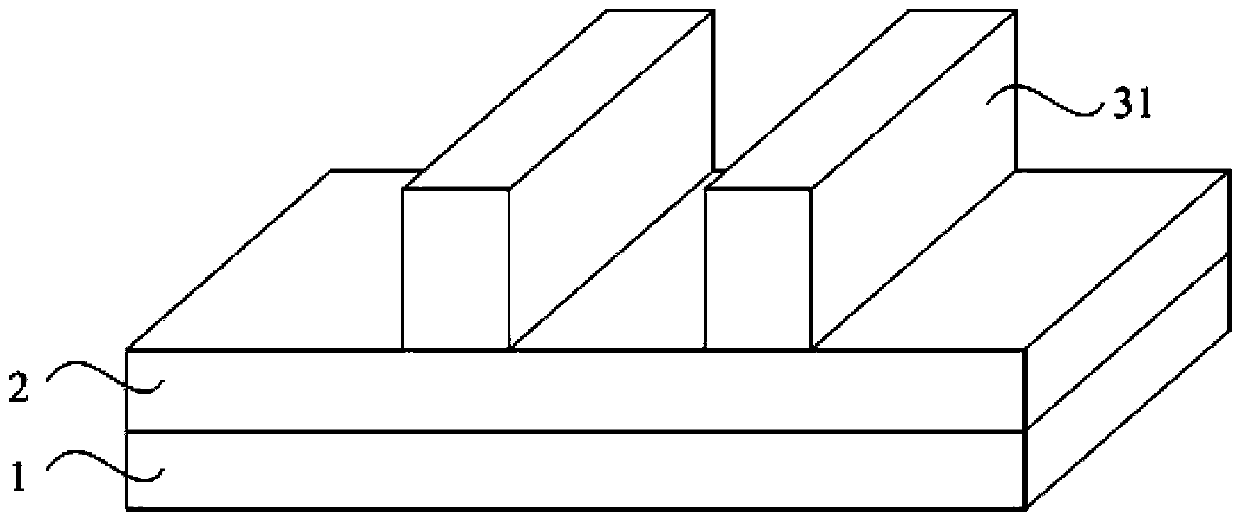

[0046] Figure 7B for Figure 7A Schematic diagram of the plane cut along the tangent AA', refer to Figure 7A , Figure 7B with Figure 8 and performing first etching on the polysilicon layer in the gate width direction. Gate length direction refers to the direction from source to drain, refer to Figure 7A , the gate length direction is the direction...

no. 2 example

[0088] The difference between the second embodiment and the first embodiment is:

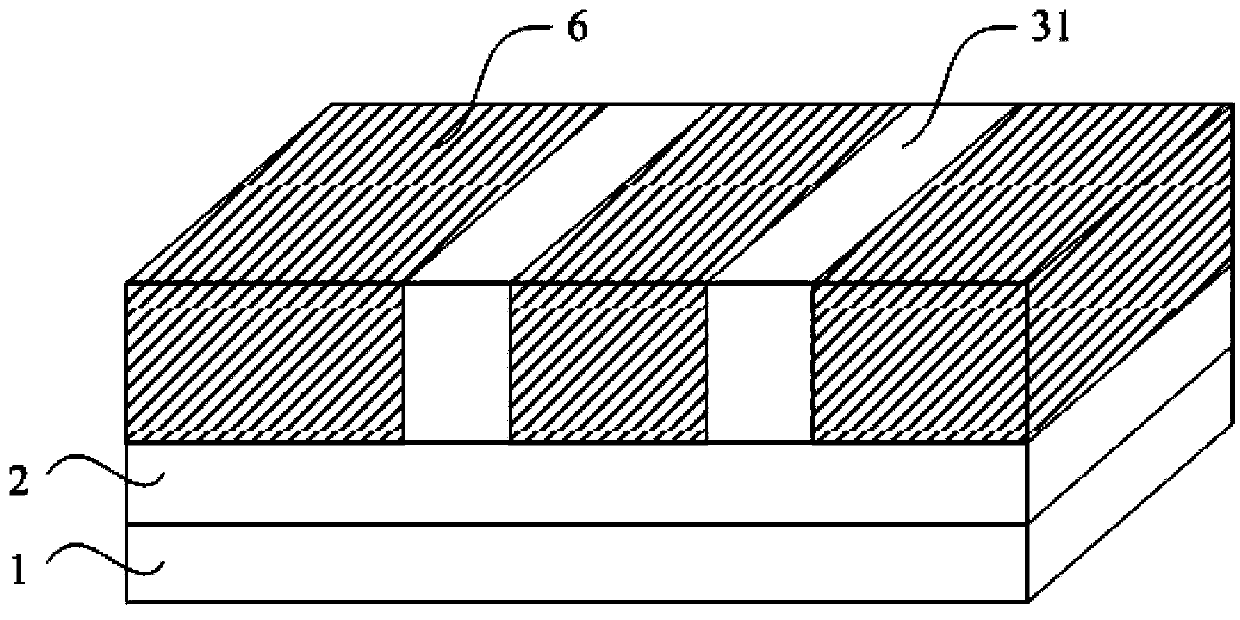

[0089] Carrying out the first etching and the second etching to the first hard mask layer 141, after the first etching and the second etching, the polysilicon layer is etched through the first hard mask layer 141 130 is etched to form a gate 132 .

[0090] refer to Figure 14 , performing a first etching on the first hard mask layer 141 .

[0091] For the first etching method, refer to the relevant steps in the first embodiment.

[0092] refer to Figure 15 , performing a second etching on the first hard mask layer 141 .

[0093] For the second etching method, refer to the relevant steps in the first embodiment.

[0094] refer to Figure 16 After the first etching and the second etching are performed on the hard mask layer 141 , the polysilicon layer 130 is etched through the first hard mask layer 141 to form the gate 132 .

[0095] For other information refer to the first embodiment.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More