Simulation reference level buffer for pipelined analog-digital converter

An analog-to-digital converter and reference level technology, applied in the direction of analog-to-digital converters, etc., can solve the problem that the working sequence cannot be maintained.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

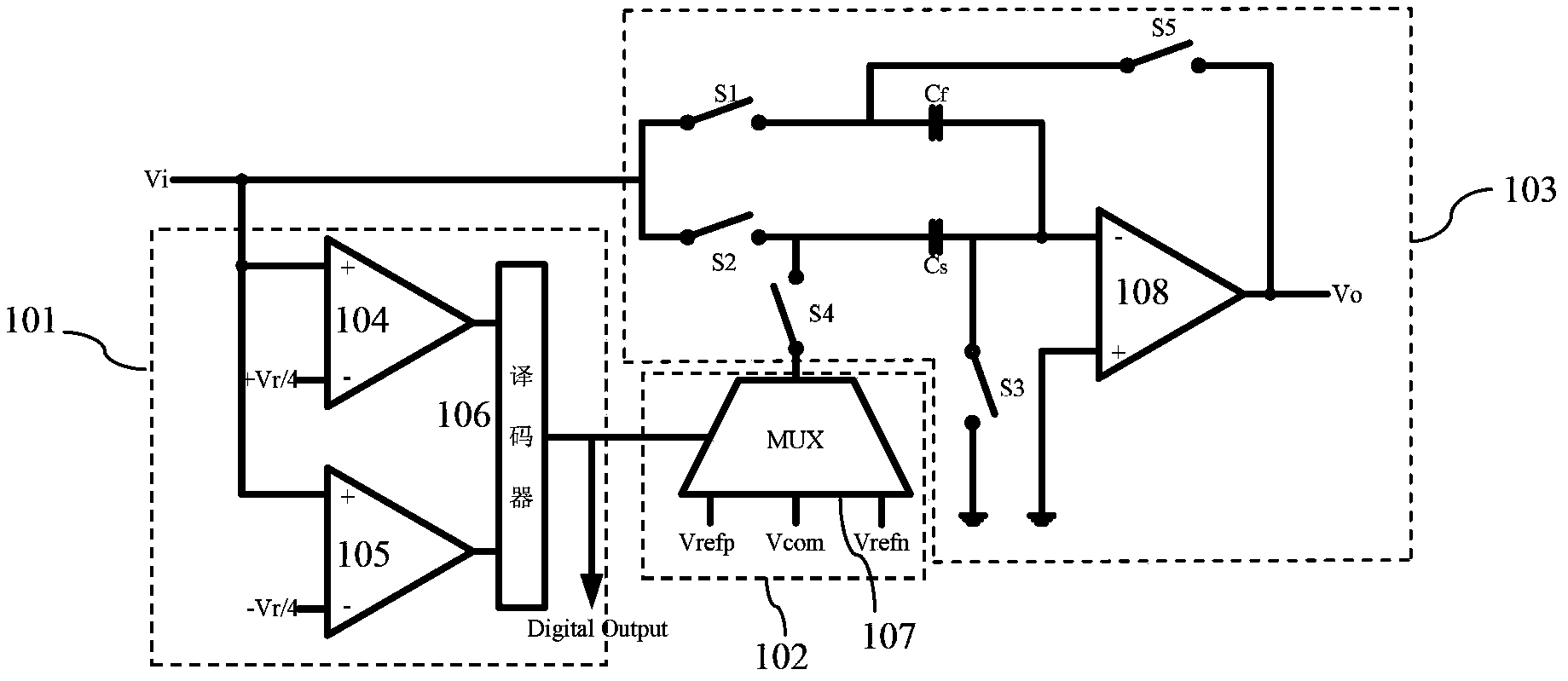

[0035] The embodiment of the present invention is used in the analog reference level buffer of a pipelined analog-to-digital converter. The output levels of the sub-analog-to-digital converters of the pipelined analog-to-digital converter include three analog reference levels. The first analog reference voltage The level inp1 is a high level, the second analog reference level inp2 is a common mode level, the third analog reference level inp3 is a low level, and the first analog reference level inp1 is greater than the second analog reference level inp2, the second analog reference level inp2 is greater than the third analog reference level inp3. The analog reference level buffer includes a first buffer, a second buffer and a third buffer.

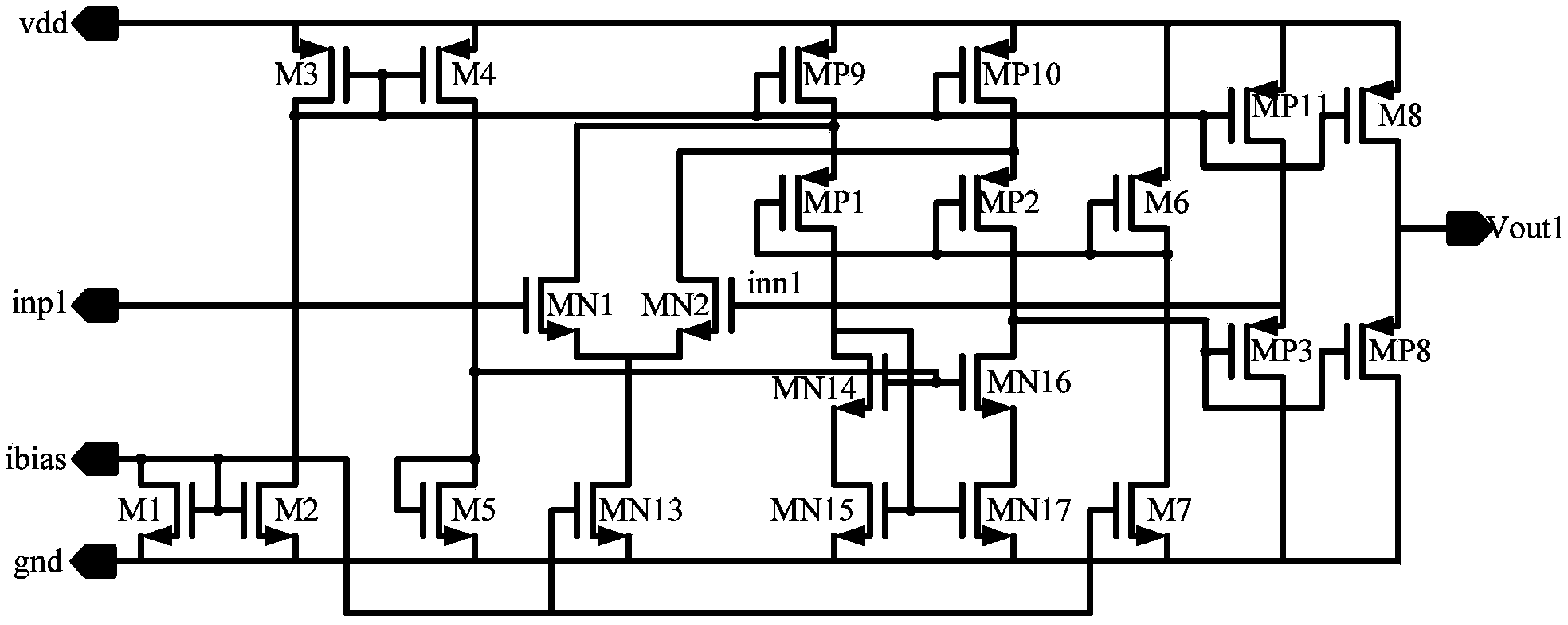

[0036] Such as figure 2 Shown is a circuit diagram of a first buffer in an embodiment of the present invention; the first buffer is used to provide buffering for the first analog reference level inp1 and improve the driving capability of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More