Folded-gated l-channel low-leakage current tunneling transistor

A tunneling transistor, low-leakage technology, applied in thyristors, circuits, electrical components, etc., can solve the problems of large static power consumption, cannot be reduced, and the gate electrode control ability is weakened, and achieves enhanced control effect, fast current rise rate, The effect of overcoming the effects of subthreshold properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

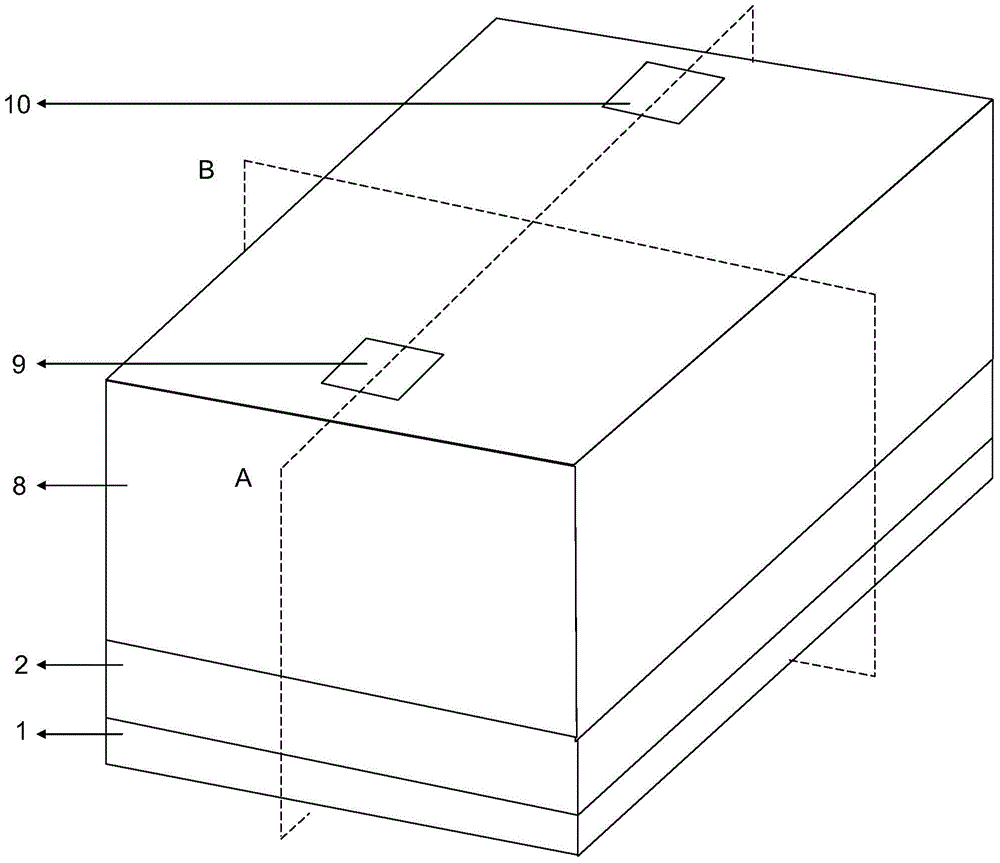

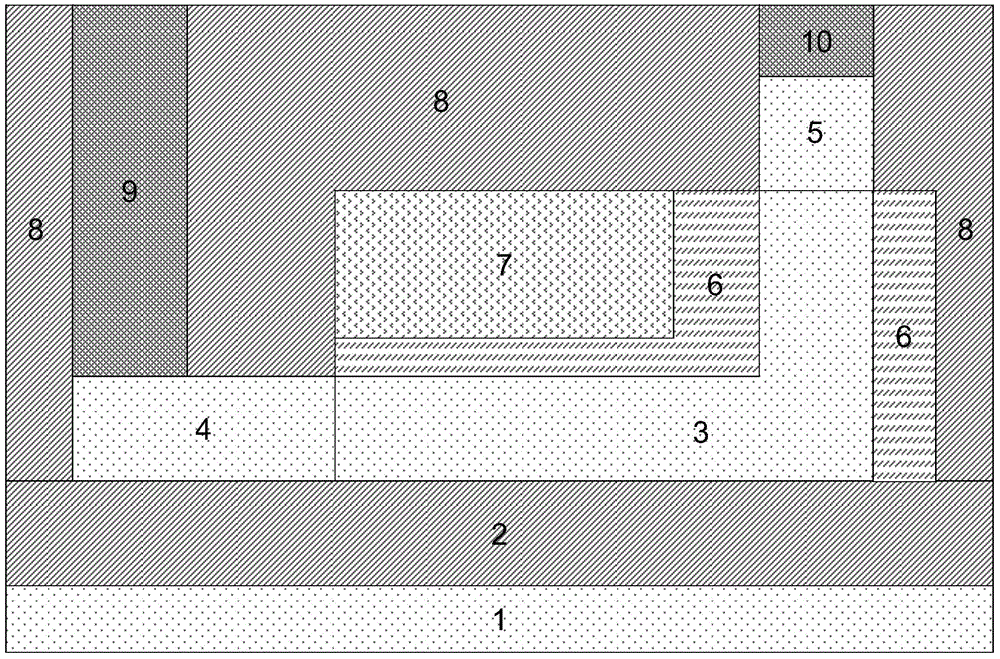

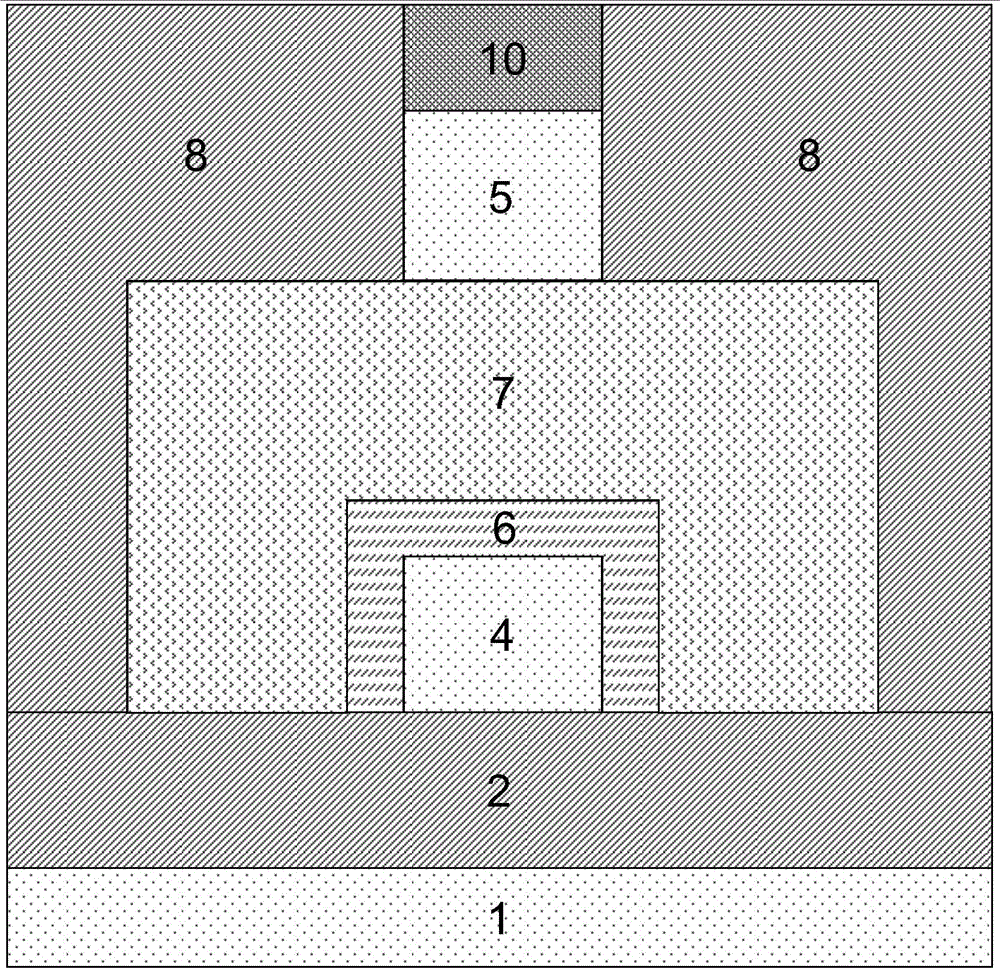

[0030] The invention provides a folded gate-controlled L-shaped channel low-leakage current tunneling transistor, comprising a silicon substrate 1 of an SOI wafer; an insulating layer 2 of the SOI wafer is above the silicon substrate 1 of the SOI wafer; and the SOI wafer Above the insulating layer 2 is an L-shaped intrinsic silicon 3; one end of the horizontal portion of the L-shaped intrinsic silicon 3 forms a heavily doped source region 4 by ion implantation; the upper end of the vertical portion of the L-shaped intrinsic silicon 3 A heavily doped drain region 5 is formed by ion implantation; a gate insulating layer 6 with a high dielectric constant is formed above the middle position of the horizontal part of the L-shaped intrinsic silicon 3 and on the side of the vertical part close to the source region; Above the high dielectric constant gate insulating layer 6 is the folded gate electrode 7; above the source region 4 and the drain region 5 are the source electrode 9 and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More