Device equivalent circuit model parameter extracting method and bonding pad parasitic parameter extracting method

An equivalent circuit model and parameter extraction technology, which is applied in electrical digital data processing, instruments, and special data processing applications, etc., can solve problems such as the difficulty of completely stripping parasitic capacitance parameters and affecting the accuracy of extracted inductance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

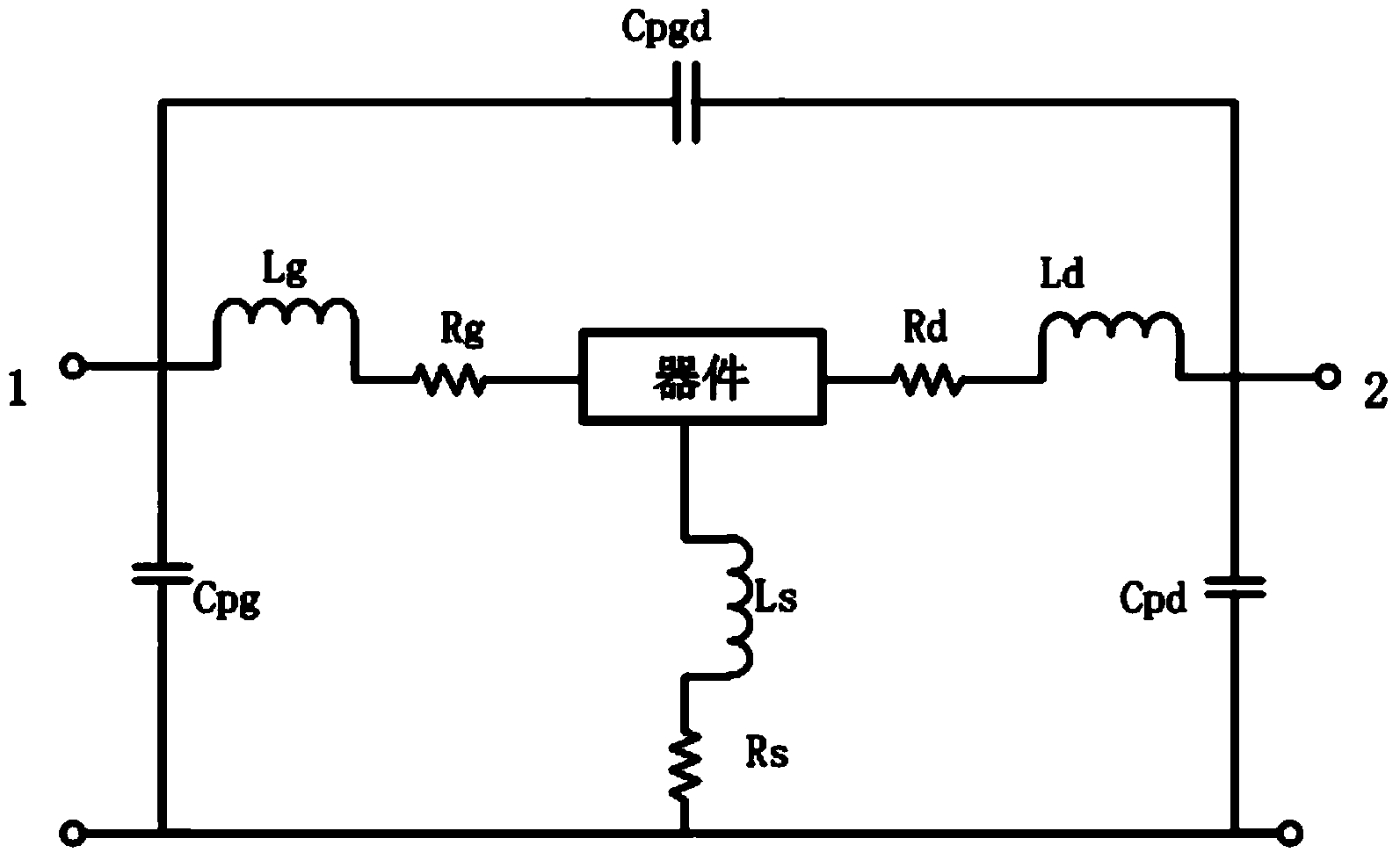

[0035] figure 1 It is the device test equivalent circuit diagram used in the method for extracting pad parasitic parameters in the embodiment of the present invention, and the equivalent circuit diagram includes the peripheral parasitic capacitance C pg 、C pd 、C pgd , the series parasitic resistance R g , R d , R s and series series parasitic inductance L g , L d , L s . The method of parameter extraction here is also an illustration of how to extract the above parameters in this equivalent circuit diagram.

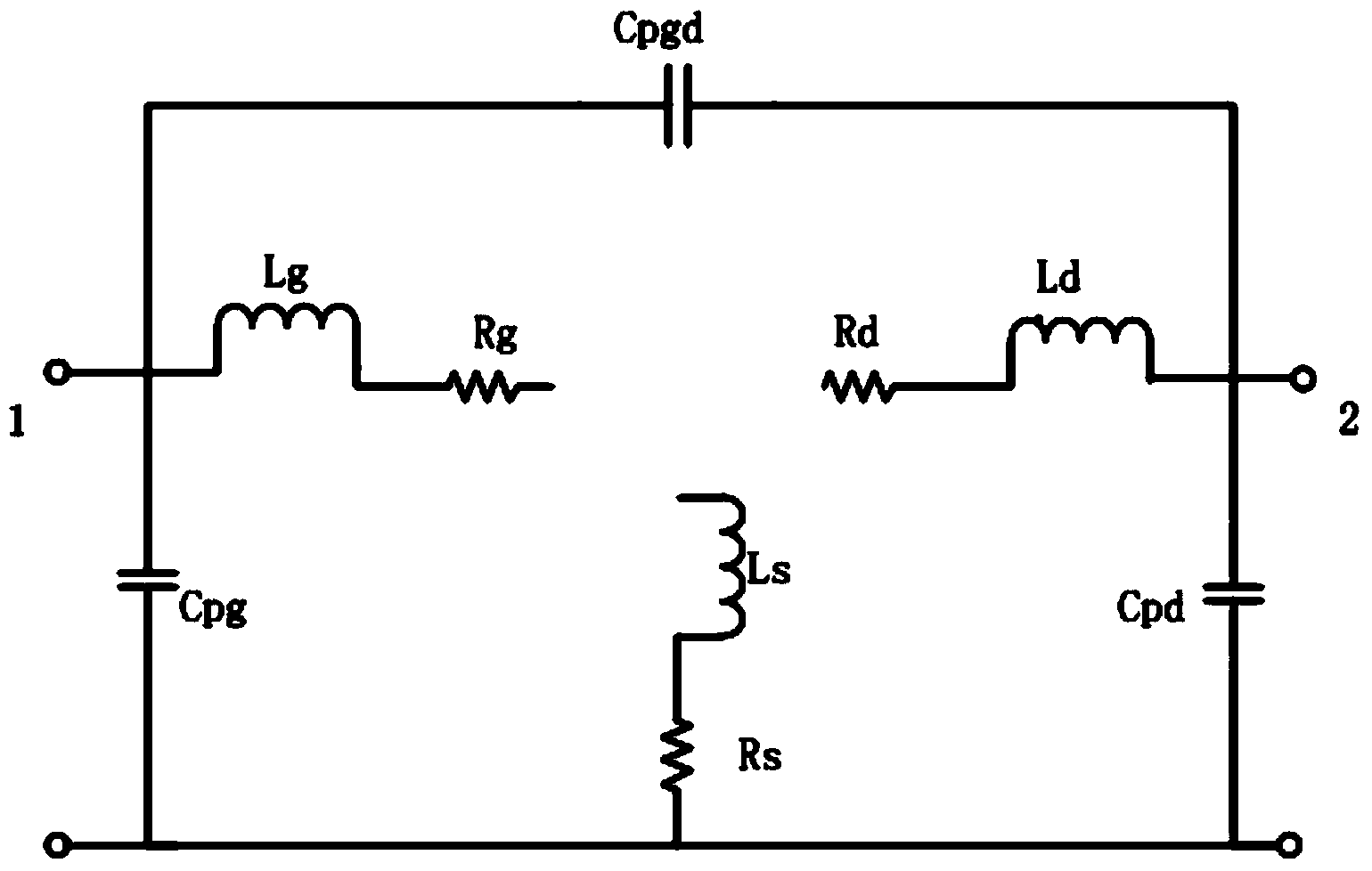

[0036] figure 2 It is the topology diagram of the equivalent circuit model under the pad open circuit structure in which the peripheral parasitic capacitance parameters are extracted in the pad parasitic parameter extraction method of the embodiment of the present invention, including three peripheral parasitic capacitance param...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com