Chip automatic simulation verification system

A chip system, simulation verification technology, applied in software testing/debugging, etc., can solve problems such as time-consuming and labor-consuming, complex communication protocol interaction between C model and circuit, high threshold of automatic simulation platform, etc., and achieve high efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

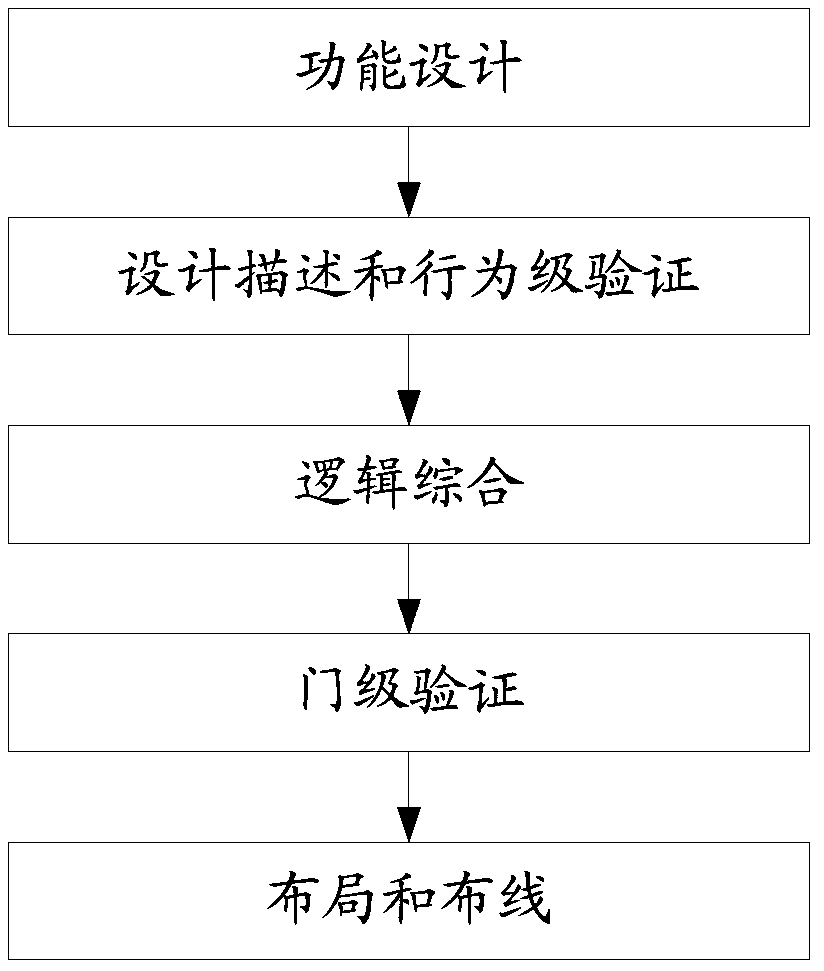

[0024] Such as figure 1 Shown is a schematic diagram of the SoC development process. The system-on-chip needs to go through the following main stages from the initial requirements to the final product: functional design, design description and behavior-level verification, logic synthesis, gate-level verification, layout and wiring, etc.

[0025] The purpose of verification (verification) is to confirm that the functional correctness and performance (speed and power consumption, etc.) of the design meet the design requirements, throughout the entire design process. A system-on-chip includes hardware resources and software systems. Modern SoC design is usually software-hardware co-design. Therefore, in the design description and behavior-level verification stages, hardware resources and software modules need to be divided to form a register transfer level (RTL) level structure.

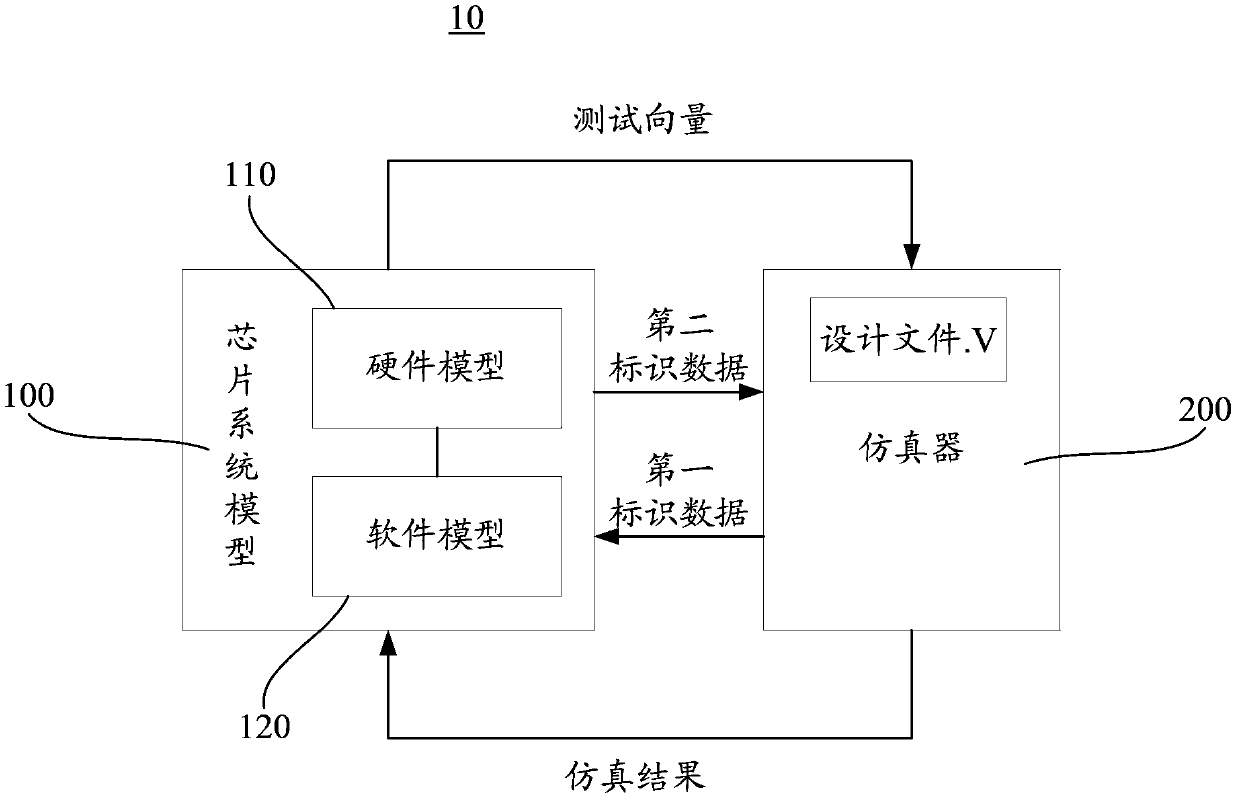

[0026] The systems and methods provided in the following embodiments are used for testing and veri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More