Fin manufacturing method

A manufacturing method and technology of fins, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as fins are fragile, small in size, easy to break or collapse, and achieve the effect of improving device performance and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

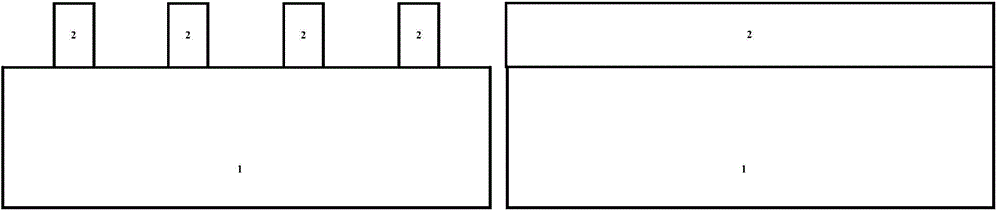

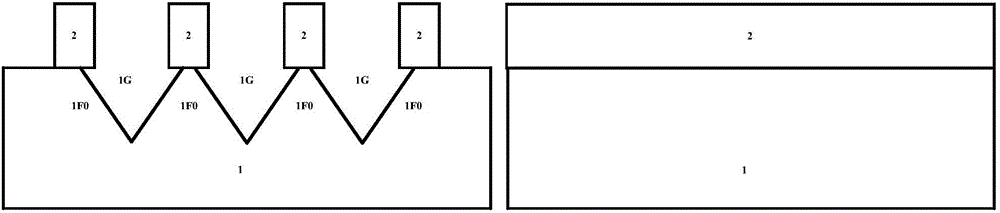

[0032] The features and technical effects of the technical solution of the present invention will be described in detail below with reference to the accompanying drawings and in conjunction with schematic embodiments, and a fin manufacturing method that can effectively improve the fineness of the fins and improve the insulation and isolation effect between the fins is disclosed. It should be pointed out that similar reference numerals represent similar structures, and the terms "first", "second", "upper", "lower" and the like used in this application can be used to modify various device structures or manufacturing processes . These modifications do not imply spatial, sequential or hierarchical relationships of the modified device structures or fabrication processes unless specifically stated.

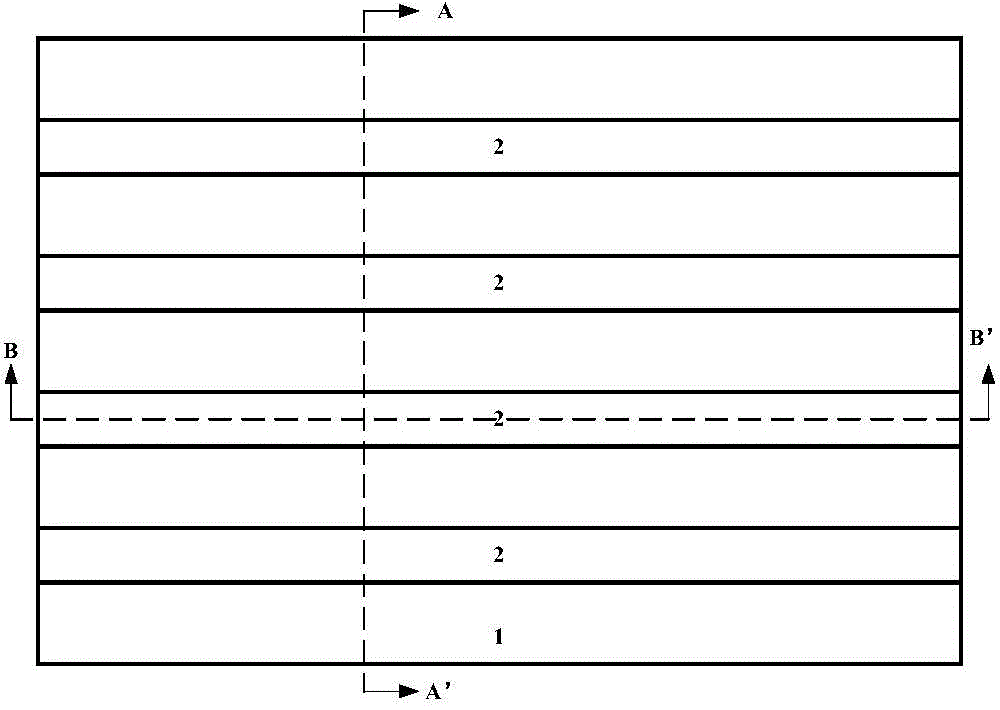

[0033] figure 1 Shown is a top view of a FinFET, tri-gate device in the prior art and the present invention, including a substrate 1 and a hard mask 2 formed on the substrate 1 . figu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More