PLL (phase-locked loop) locking state detection circuit

A technology of locked state and detection circuit, applied in the direction of electrical components, automatic power control, etc., can solve the problems of holding, not taking into account the locking signal, unable to identify the phase loss of lock, etc., to achieve the effect of simple circuit structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described in detail below in conjunction with specific embodiments, which are for explanation rather than limitation of the present invention.

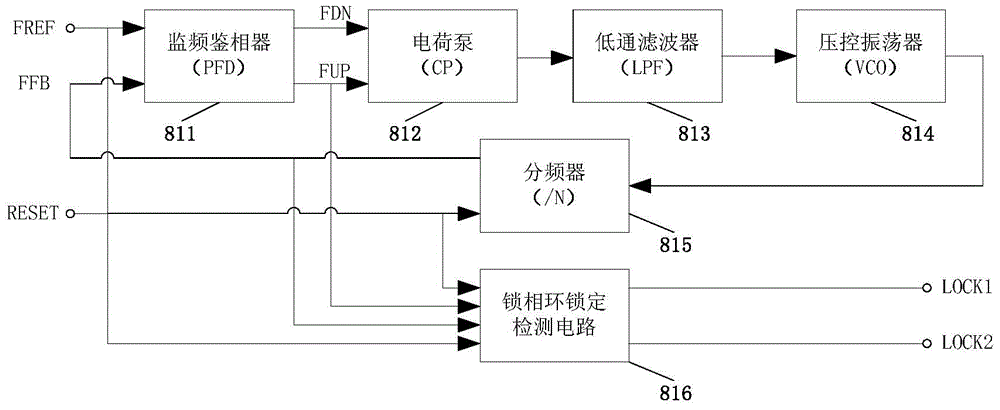

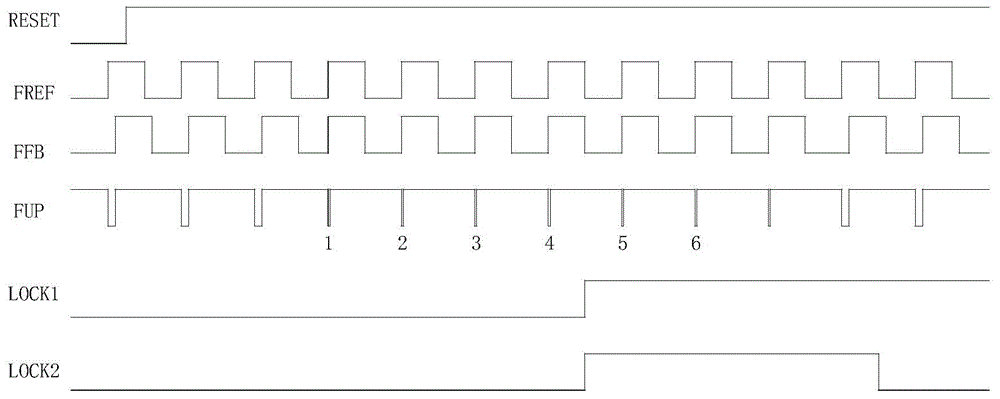

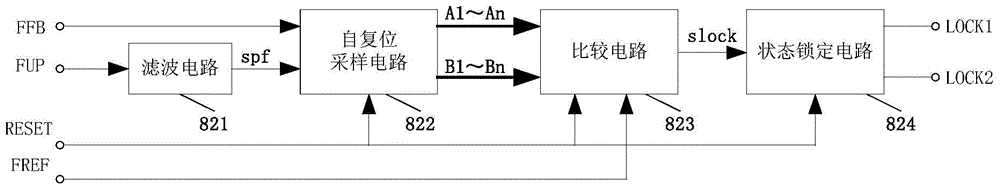

[0022] The present invention is a phase-locked loop locked state detection circuit, such as image 3 As shown, it includes a filter circuit 821, a self-reset sampling circuit 822, a comparison circuit 823, and a state lock circuit 824. And the corresponding relationship of each input signal is as follows figure 2 Shown.

[0023] Before the phase-locked loop lock state detection circuit works, the reset signal should be used to reset the circuit. See Figure 4 , The reset signal RESET is used to reset the phase-locked loop lock state detection circuit, when the RESET signal is low, the flip-flops DFFA1, DFFA2..., DFFAn, DFFAn+1, DFFB1, DFFB2..., DFFBn, DFFBn+1 The data output terminal Q of the comparison flip-flop DFF1 outputs a low level and is in a reset state; the data output terminal Q of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More