Method and system for preparing silicon-based III-V gallium arsenide semiconductor material

A gallium arsenide and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of inability to manufacture large-scale high-quality silicon-based epitaxial III-V semiconductor materials, and reduce material production cost, lower dislocation density in the upper layer, and reduced strain energy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

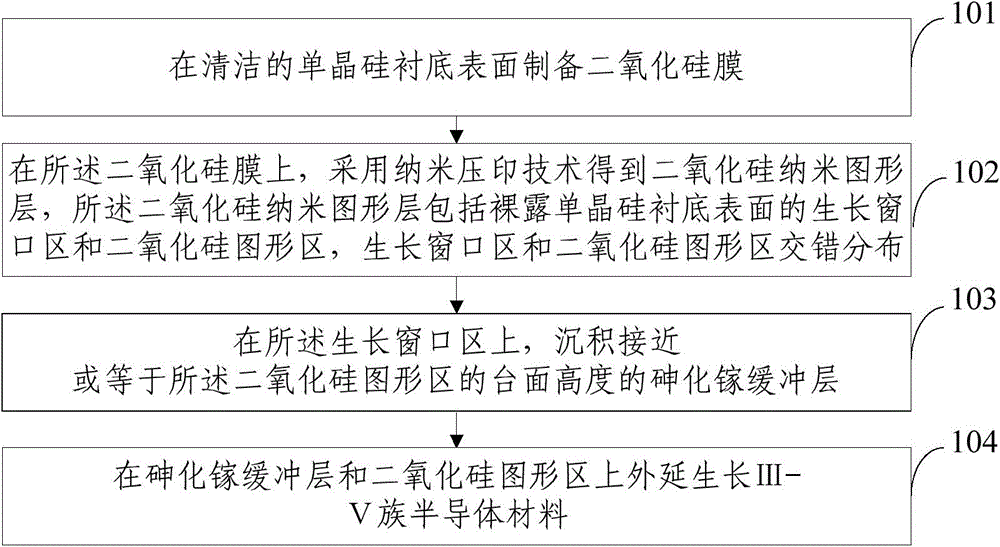

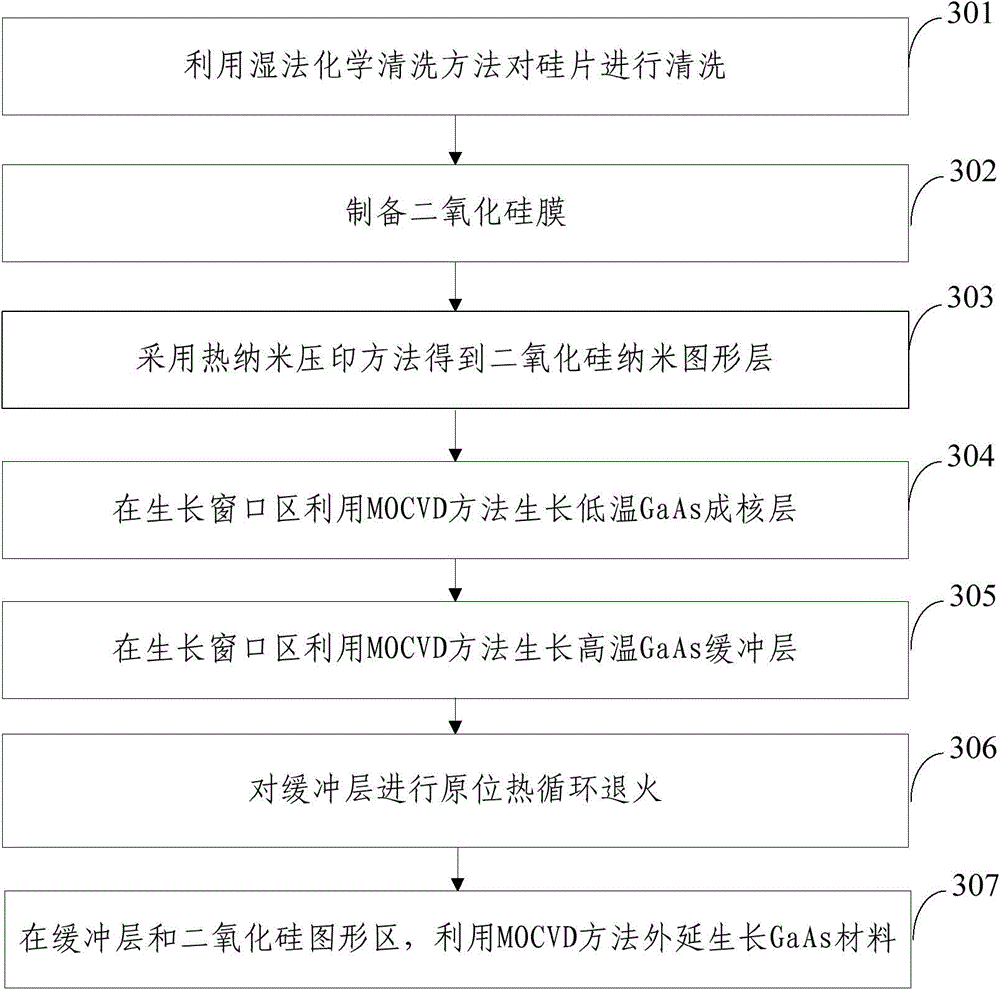

[0064] Embodiments of the present invention firstly provide a method for preparing a silicon-based III-V gallium arsenide semiconductor material, see figure 1 , the method includes:

[0065] Step 101: preparing a silicon dioxide film on the surface of a clean single crystal silicon substrate.

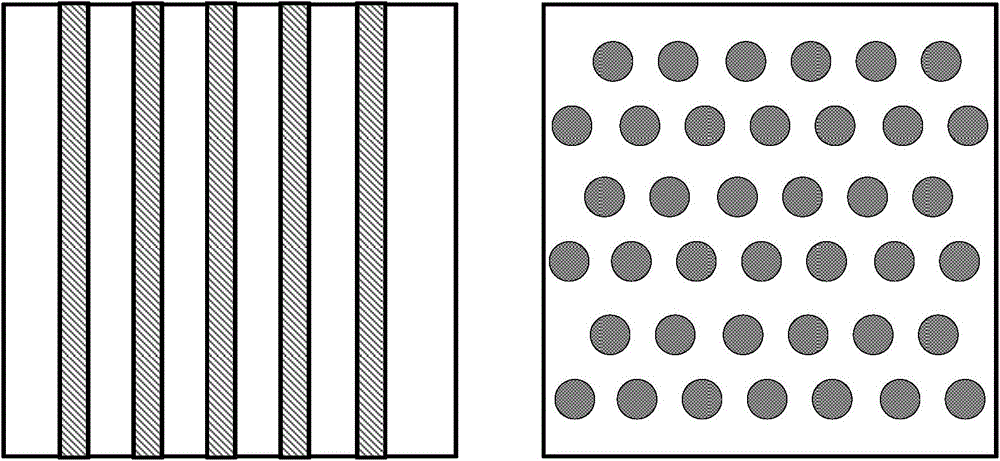

[0066] Step 102: On the silicon dioxide film, use nanoimprint technology to obtain a silicon dioxide nano-patterned layer, the silicon dioxide nano-patterned layer includes a growth window area that exposes the surface of the single crystal silicon substrate, and silicon dioxide The graphic area, the growth window area and the silicon dioxide graphic area are distributed alternately.

[0067] Step 103: On the growth window area, deposit a gallium arsenide buffer layer close to or equal to the mesa height of the silicon dioxide pattern area.

[0068] Step 104: Epitaxially grow III-V group semiconductor material on the gallium arsenide buffer layer and the silicon dioxide pattern region...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More