A delay adjustment circuit with adjustable range and step size

A technology to adjust the circuit and step size, which is applied to electrical components, pulse technology, pulse processing, etc., can solve the problem that the flipping threshold will change, and achieve the effect of small changes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The technical solution of the present invention will be further described in detail below in conjunction with the accompanying drawings, but the protection scope of the present invention is not limited to the following description.

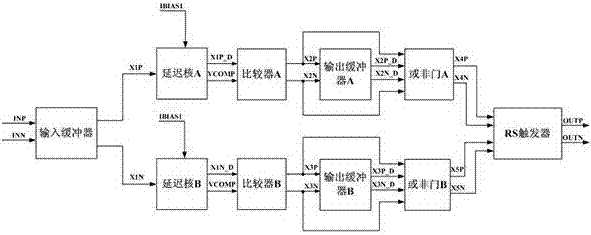

[0025] Such as figure 1 As shown, a delay adjustment circuit with adjustable range and step size, which includes an input buffer, a delay core A, a comparator A, an output buffer A, a NOR gate A, a delay core B, a comparator B, Output buffer B, NOR gate B, and RS flip-flop, the input of the input buffer is two signals (INP and INN), INP and INN are differential signals, and the input buffer is used to adjust the swing of the input signal INP and INN amplitude, and output a signal X1P suitable for the working range of the delay core A, and output a signal X1N suitable for the working range of the delay core B. The X1P signal output terminal of the input buffer is connected to the RS flip-flop through the delay core A, comparator A, output b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More