Using charge coupling to realize voltage-resistant power mos device and preparation method thereof

A MOS device and charge-coupled technology, applied in electrical components, semiconductor devices, circuits, etc., can solve the problems of small resistivity, influence, and low on-resistance of epitaxial silicon materials

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062] The present invention will be further described below in conjunction with specific drawings and embodiments.

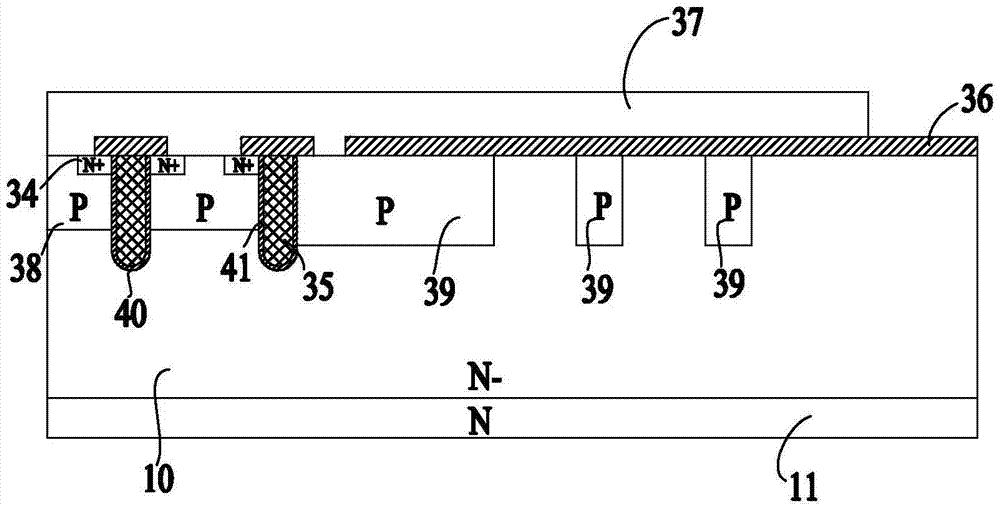

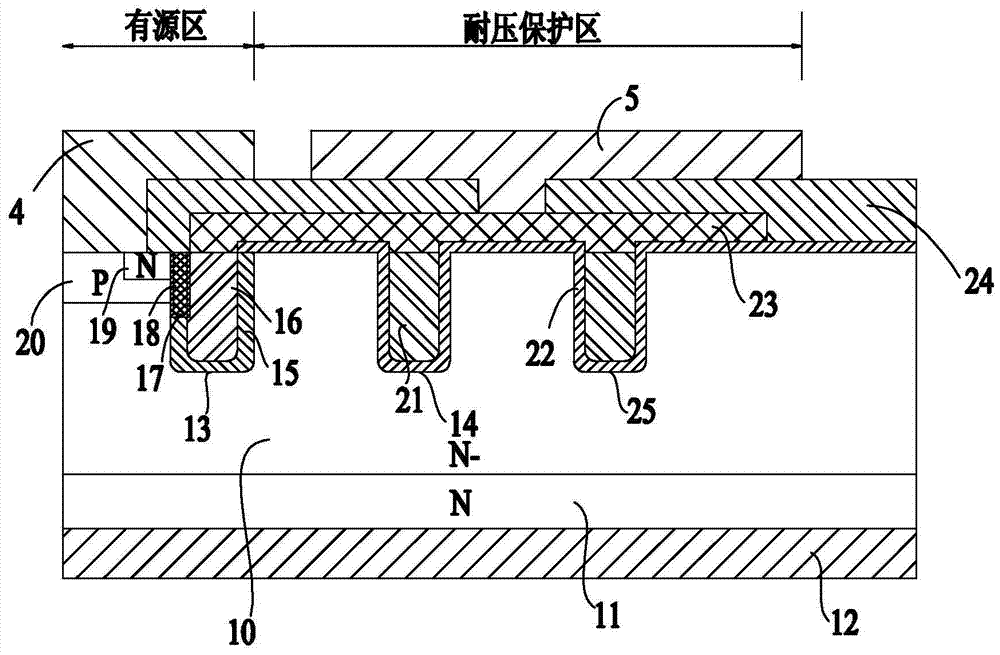

[0063] Such as figure 2 and image 3 As shown: In order to improve the withstand voltage capability and high withstand voltage reliability, and reduce the proportion of the entire chip area occupied by the terminal protection area, taking the N-type power MOS device as an example, the present invention includes the power MOS device located on the top view plane of the power MOS device. The active area 1 and the terminal protection area 2 of the semiconductor substrate, the active area 1 is located in the central area of the semiconductor substrate, the terminal protection area 2 is located at the outer circle of the active area 1 and surrounds the active area 1, and the terminal protection The region 2 includes a withstand voltage protection region 3 adjacent to the active region 1; on the cross section of the power MOS device, the semiconductor substrate i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More