Thin film transistor and manufacturing method thereof as well as array substrate and display device

A technology of a thin film transistor and a manufacturing method, applied in the field of semiconductor device preparation, capable of solving problems such as easy disconnection of pixel electrodes 5, increased production costs, uneven thickness, etc., and achieving problems of easy disconnection, improved yield, and uniform thickness Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

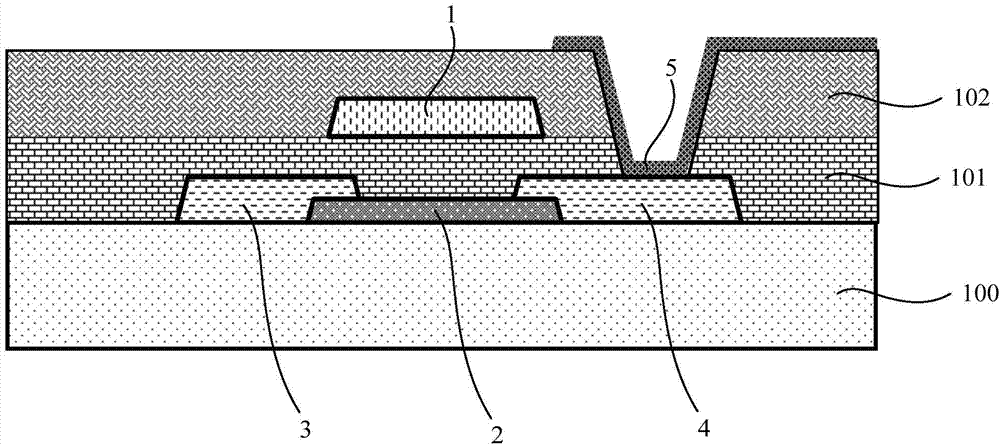

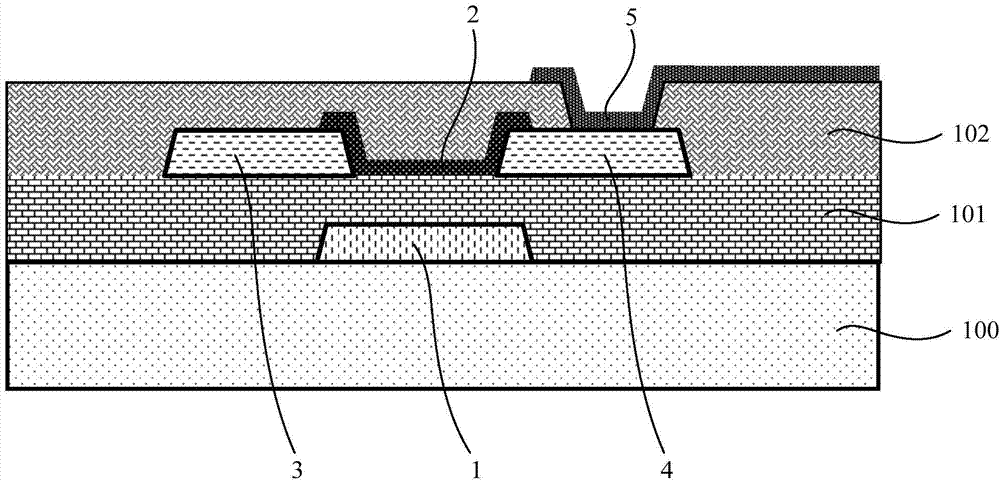

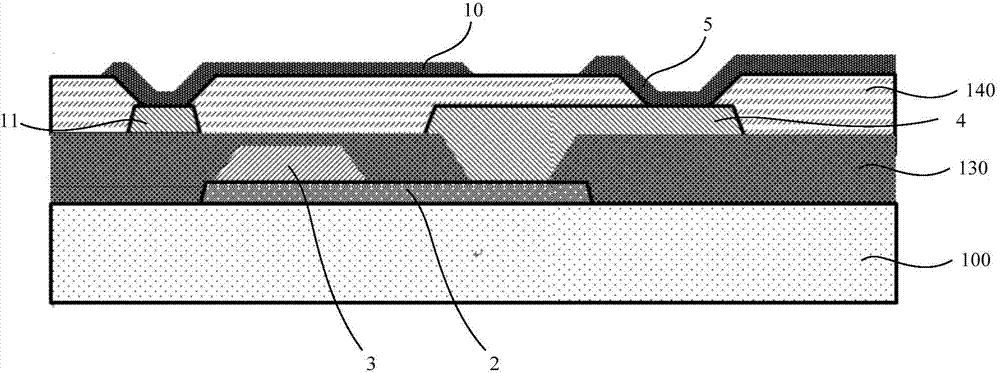

[0028] The invention provides a thin film transistor, the source electrode and the drain electrode of which are located on the active layer, and the entire active layer is located in the same plane, so that the active layer does not have the problem of easy disconnection caused by climbing difficulties, and the active layer The thickness is uniform, and the phenomenon of breakdown and short circuit is not easy to occur in the working process, which improves the yield rate of the thin film transistor. Furthermore, the source electrode and the drain electrode are arranged in a non-same-layer structure, so that the distance between the source electrode and the drain electrode can be flexibly adjusted, and it is easier to realize a narrow channel and improve the performance of the thin film transistor.

[0029] For a liquid crystal display device, the electrode on the array substrate electrically contacting the drain electrode of the thin film transistor is a transparent pixel elec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More