Fin type field-effect transistor forming method

A fin-type field effect transistor and fin technology are applied in the directions of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., which can solve the problem that the performance stability of the fin-type field effect transistor needs to be further improved, and achieve good penetration prevention effect. Guaranteed isolation effect and improved performance stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

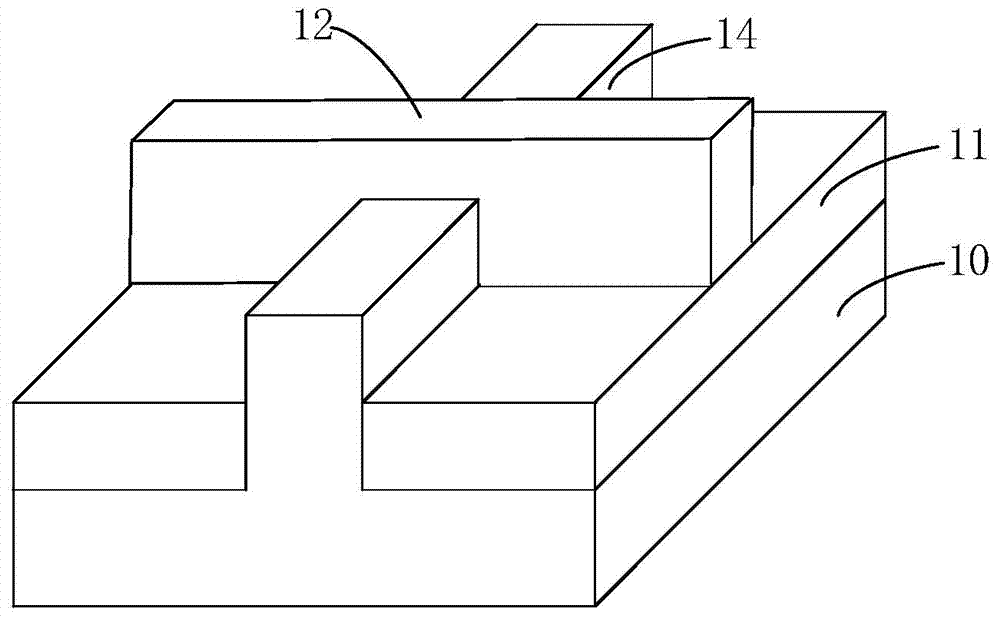

Image

Examples

Embodiment Construction

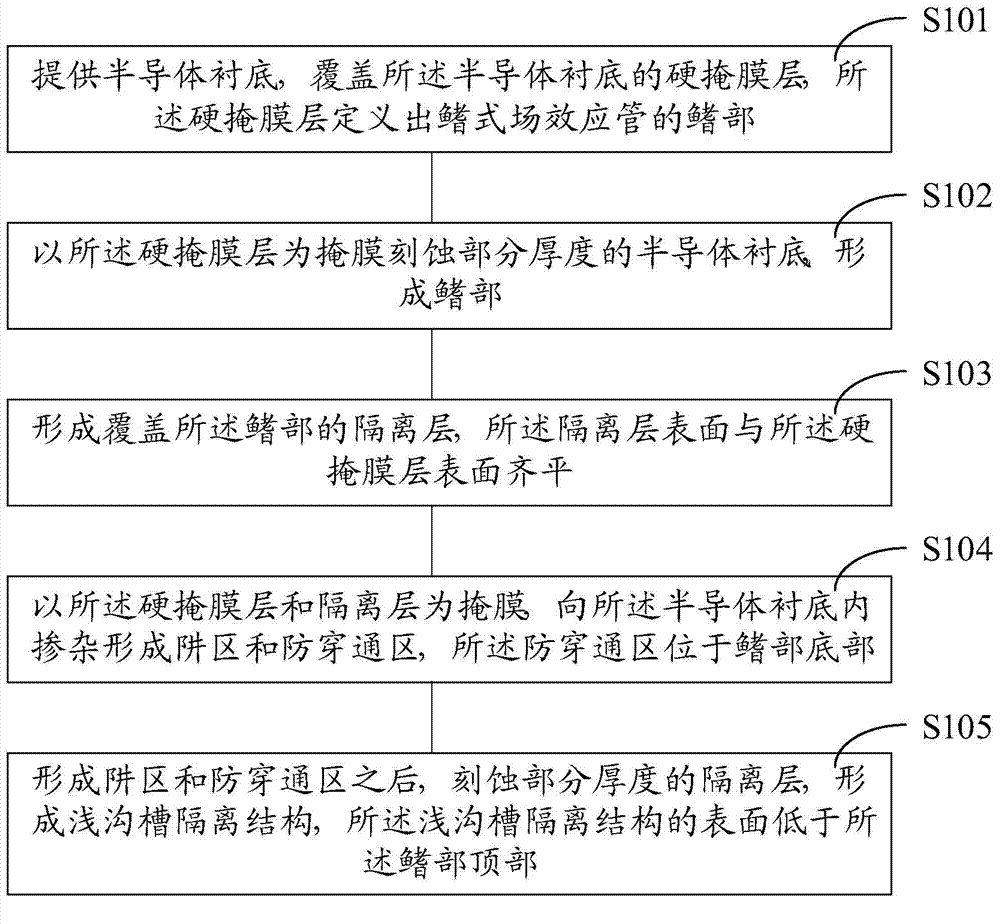

[0027] As described in the background art, the performance stability of the fin-type FET formed in the prior art needs to be further improved.

[0028] After research, it is found that the above phenomenon is caused by the following factors: one is the ion concentration of the punch-through region at the bottom of the fin; the second is the quality of the fin; and the third is the depth of the well region doping.

[0029] Through research, it is found that when forming fin-type FETs, if the semiconductor substrate is doped before the fins and shallow trench isolation structures are formed to form punch-through regions and well regions later, it can Avoid damage to the quality of the fins caused by ion doping, but the oxidation process and annealing process during the formation of the shallow trench structure are likely to cause ion diffusion (dose loss) in the anti-pierce area, resulting in low ion concentration in this area Is lower than the predetermined value, which makes the an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More