Ceramic circuit board, semiconductor device, and method for manufacturing ceramic circuit board

A technology for wiring substrates and ceramics, used in semiconductor devices, semiconductor/solid-state device parts, manufacturing tools, etc., can solve the problems of uneven shrinkage, high sintering temperature, and cannot eliminate the lowering of the position accuracy of upper and lower via holes, and achieve high The effect of reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

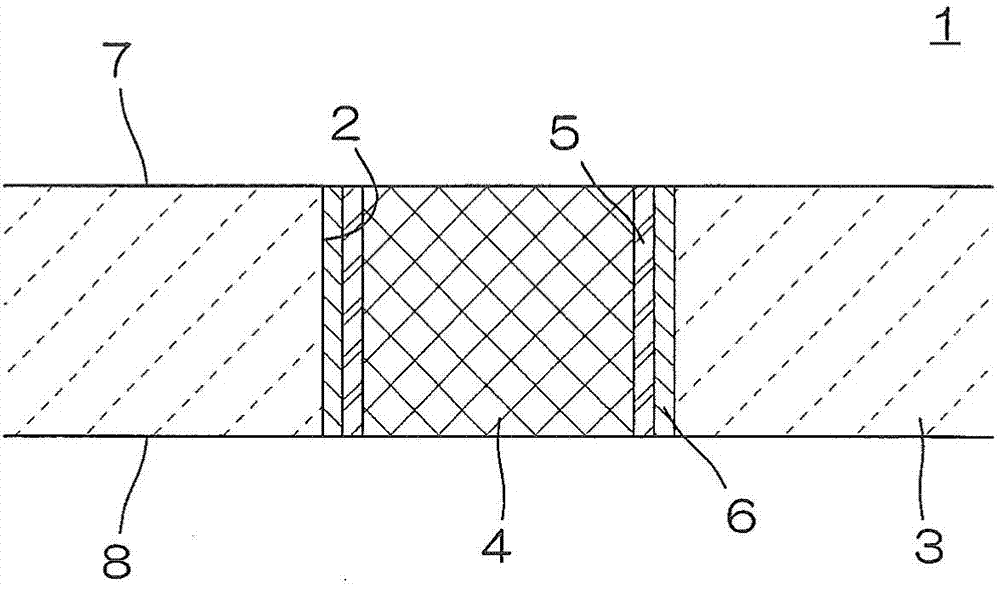

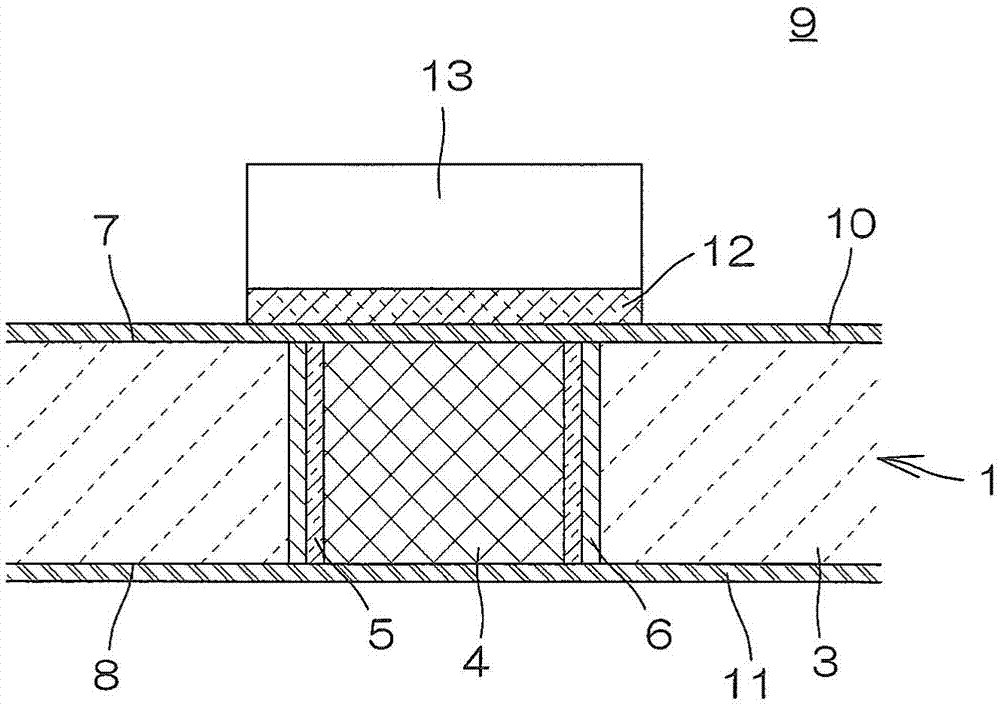

[0199] (Formation of upper and lower via holes 2)

[0200] On an AlN substrate 3 of □100×t0.5 mm polished to a surface roughness Ra of 0.5 μm, 3000 vertical via holes 2 of φ0.5 mm were formed using a YAG laser. The positional accuracy of the formed upper and lower via holes 2 was measured using a tool microscope and found to be ±20 μm.

[0201] (Formation of Adhesive Layer 6 and Intermediate Layer 5)

[0202] The substrate 3 formed with the upper and lower via holes 2 was ultrasonically cleaned with isopropyl alcohol (IPA), and the IPA was volatilized by air blowing, and then dried by heating in an oven at 100° C. for 10 minutes.

[0203] Then, on the surfaces 7 and 8 on both sides of the substrate 3 and the inner surfaces of the upper and lower via holes 2, a Ti film with a thickness of 0.1 μm as the adhesive layer 6 and a Ti film with a thickness of 1.0 μm as the intermediate layer 5 were sequentially formed by sputtering. The W film.

[0204] The film is formed in the sp...

Embodiment 2

[0241] Except that the thickness of the W film as the intermediate layer 5 is set to 0.01 μm (Example 2-1), 0.1 μm (Example 2-2), 0.3 μm (Example 2-3), 0.5 μm (Example 2- 4), 3.0 μm (Example 2-5), and 10.0 μm (Example 2-6), complete the ceramic wiring substrate 1 in the same manner as Example 1, form metallization layers 10, 11, and the metallization The cross-sectional observations 1 and 2 were performed after the layers 10 and 11 were patterned. The results are shown in Table 1 together with the results of Example 1 and Comparative Example 1.

[0242] [Table 1]

[0243] Table 1

[0244]

[0245] According to the results of Example 1, Examples 2-1 to 2-6, and Comparative Example 1 in Table 1, it is known that by forming a W film as an intermediate layer 5 on the inner surface of the upper and lower via holes 2, the W film from the ceramics can be suppressed. Diffusion of Al in the substrate 3 made and the generation ratio of voids in the upper and lower conductors 4 cau...

Embodiment 3

[0248] In addition to being the intermediate layer 5, forming a thickness of 0.01 μm (Example 3-1), 0.1 μm (Example 3-2), 0.3 μm (Example 3-3), 0.5 μm (Example 3-4), 1.0 μm (Example 3-5), 3.0 μm (Example 3-6), or 10.0 μm (Example 3-7) Mo film, complete the ceramic wiring substrate 1 in the same manner as in Example 1, and form a metallization layer 10. , 11, and after patterning the metallized layers 10, 11, cross-sectional observations 1, 2 were implemented. The results are shown in Table 2 together with the results of Comparative Example 1.

[0249] [Table 2]

[0250] Table 2

[0251]

[0252] From the results of Examples 3-1 to 3-7 and Comparative Example 1 in Table 2, it is known that the same effect as that of the W film of Examples 1 and 2 can be obtained even when a Mo film is formed as the intermediate layer 5 .

[0253] That is, it was found that by forming a Mo film as the intermediate layer 5 on the inner surface of the upper and lower via holes 2, the diffus...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More