FPGA-based multichannel cyclic data compressor and decompressor and method

A compressor and memory technology, applied in electrical components, code conversion, etc., can solve the problems of less system development, low data quantization accuracy, and poor real-time performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] Now in conjunction with embodiment, accompanying drawing, the present invention will be further described:

[0054] The hardware environment used for implementation is: Spartan-6 series of XILINX company, two FPGA chips of model XC6SLX150, oscilloscope, logic analyzer, and the running software environment is: ISE14.5. Taking four-way data processing as an example, we implemented the method proposed by the present invention with ISE14.5 software.

[0055] Multiplex Data Loop Compressor Module

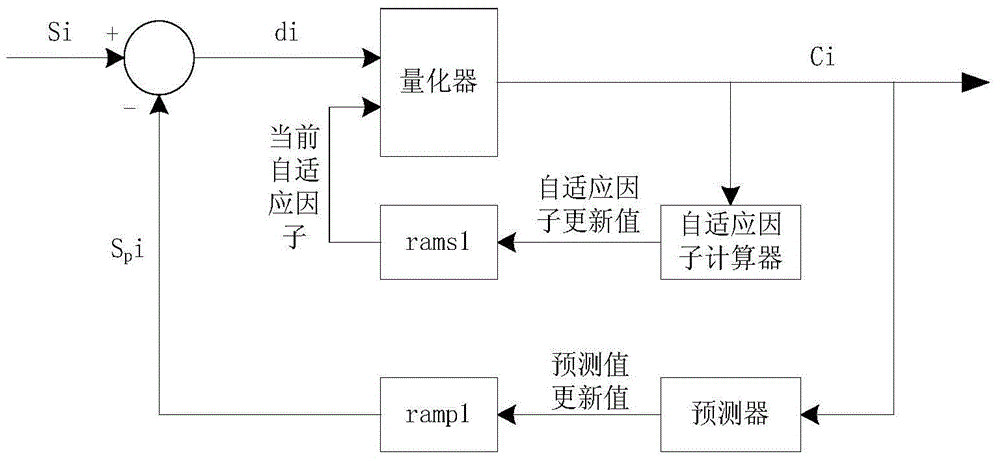

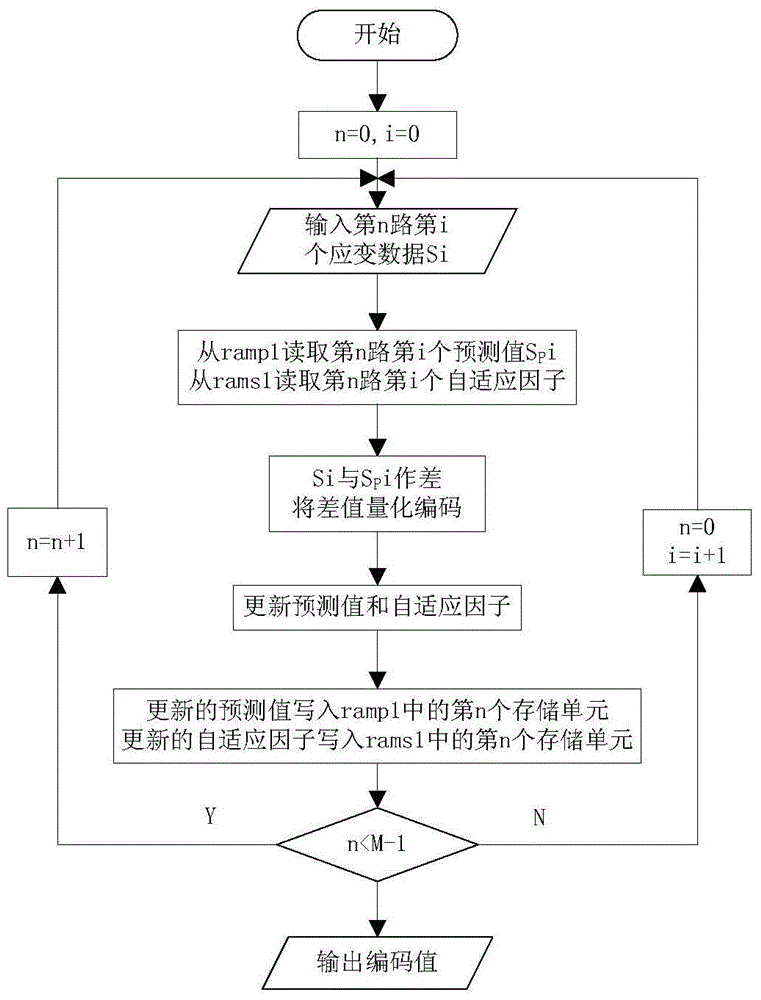

[0056] Its implementation is as follows figure 1 The design architecture shown is completed, and the modules included in the architecture and their structural realization relations are as follows:

[0057] ramp1 memory: written and generated in VHDL, with a data width of 16 bits and a data depth of 4. Its input terminal is connected to the output terminal of the predictor, which is used for buffering the predicted value parameters of multi-channel compression, and the output te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More