SRAM (Static Random Access Memory) time sequence control circuit with copy unit word line voltage rise technology

A timing control circuit and duplication unit technology, which is applied in the direction of digital memory information, information storage, static memory, etc., can solve the problems of inability to better improve the process deviation, increase the area of the multiplying circuit, and reduce the working speed of the chip, etc., to achieve optimal The ability to resist process changes, reduce delay deviation, and increase the effect of area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

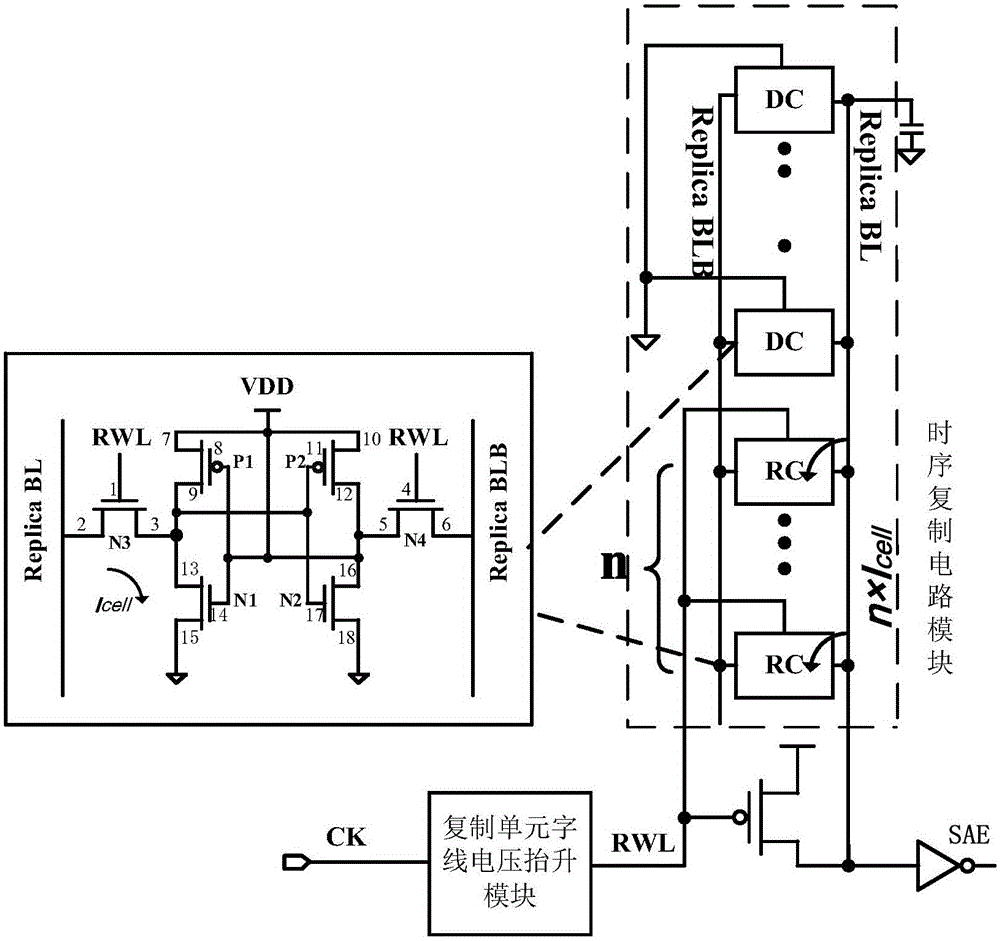

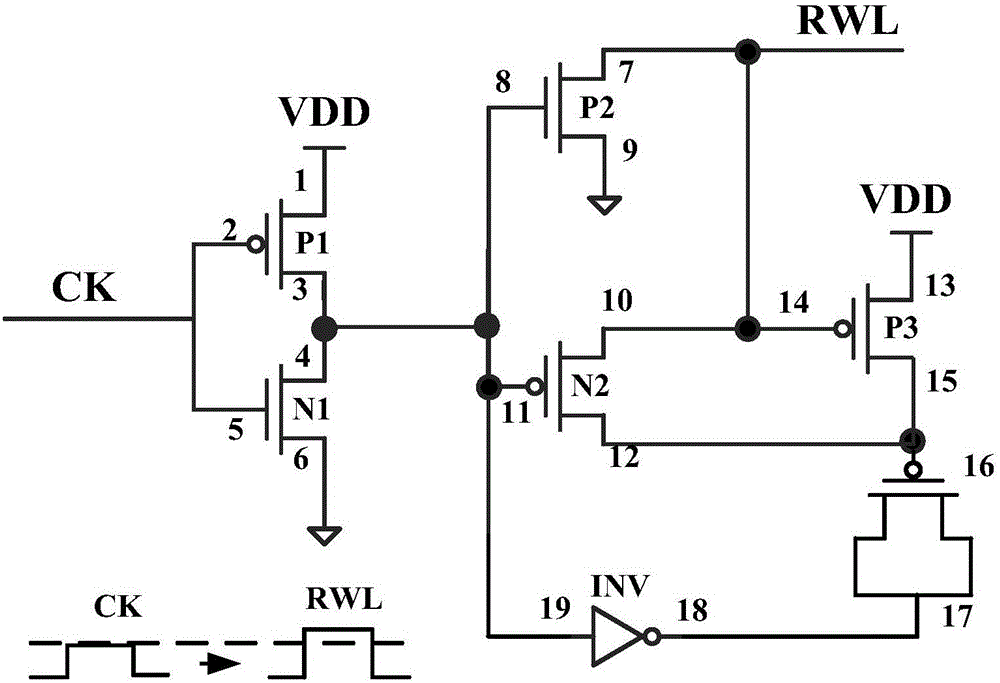

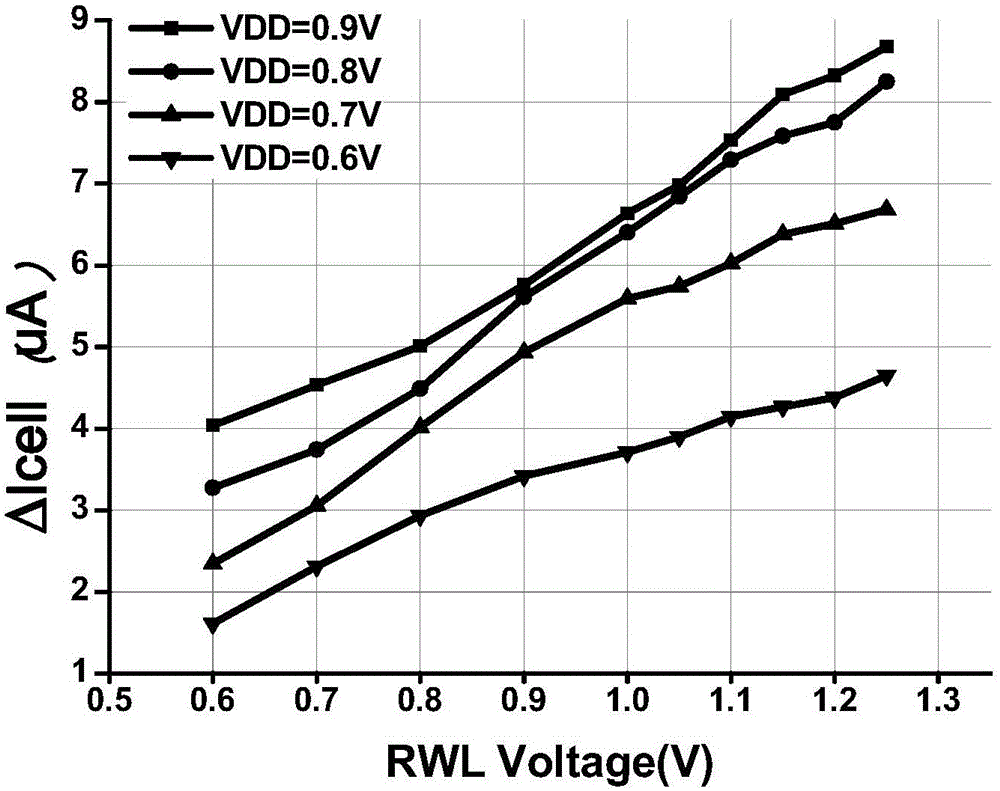

[0034] figure 1 A timing control circuit for an SRAM with the word line voltage boosting technique for replicating cells provided for an embodiment of the present invention, such as figure 1 As shown, it mainly includes: timing replication circuit module and replication cell word line voltage boosting module; where:

[0035] The timing replication circuit module is connected in parallel between the replication unit word line and the replication bit line, and is used to replicate the discharge time of the storage array, which includes n serially connected replica cells (RC) and several serially connected redundant cells (DC) ; There are two copy bit lines, such as figure 1 The replica bit lines ReplicaBL and ReplicaBLB in the replica; wherein, the two ends of all replica units are respectively connected to the replica bit lines ReplicaBL and ReplicaBLB, and the control ends of all replica units are connected to the replica unit word line (RWL); the redundancy Both ends of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More