Chip DRAM (dynamic random access memory) pad arrangement structure for improving encapsulation compatibility

A compatibility, pad technology, applied in electrical components, electrical solid devices, circuits, etc., can solve problems such as low compatibility, achieve strong compatibility, and improve package compatibility.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

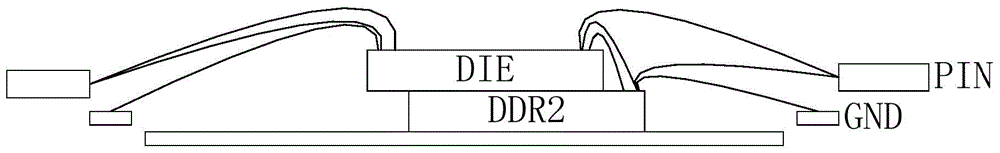

[0020] In order to make the purpose, technical solution and advantages of the present invention clearer, the chip DRAM pad layout structure and specific implementation methods for improving packaging compatibility of the present invention will be described below with reference to the accompanying drawings. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0021] The present invention proposes a solution for the actual IPC (IPCamera, network camera) market demand, and meets the following requirements:

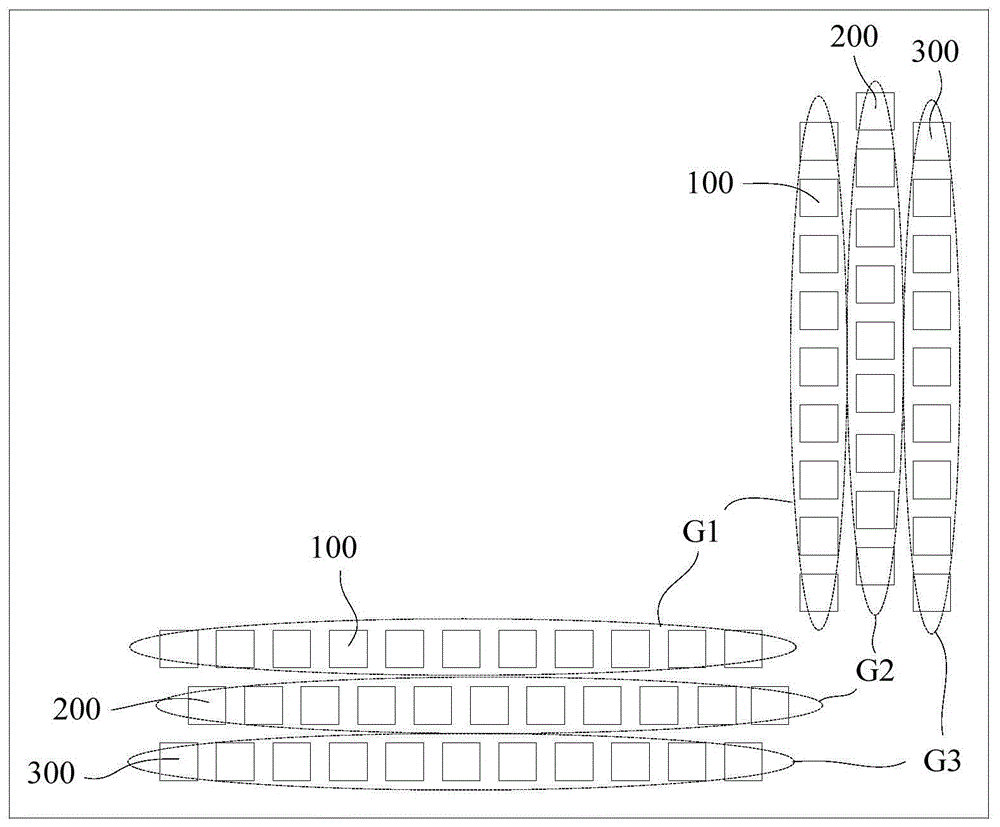

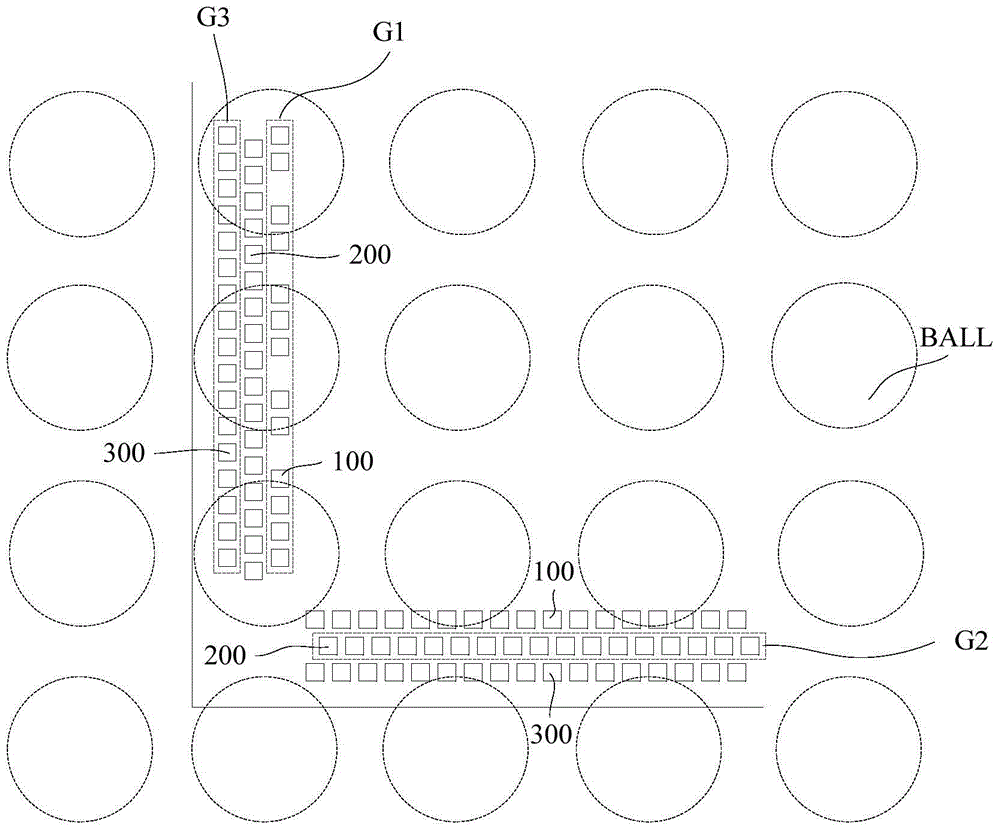

[0022] The chip design can meet the WBBGA packaging scheme, and provide a full-featured product for mid-level and low-level customers;

[0023] The same chip design satisfies the eLQFP128 package design of the DDR2 (Second Generation Double Data Rate Synchronous Dynamic Random Access Memory) KGD of two different DRAM manufacturers at the same time. product.

[0024] Since i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More