A vertical tunneling field effect transistor

A tunneling field effect and transistor technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of increasing static power consumption of devices and increasing leakage current, reducing leakage current, increasing on-state current, The effect of reducing the tunneling distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

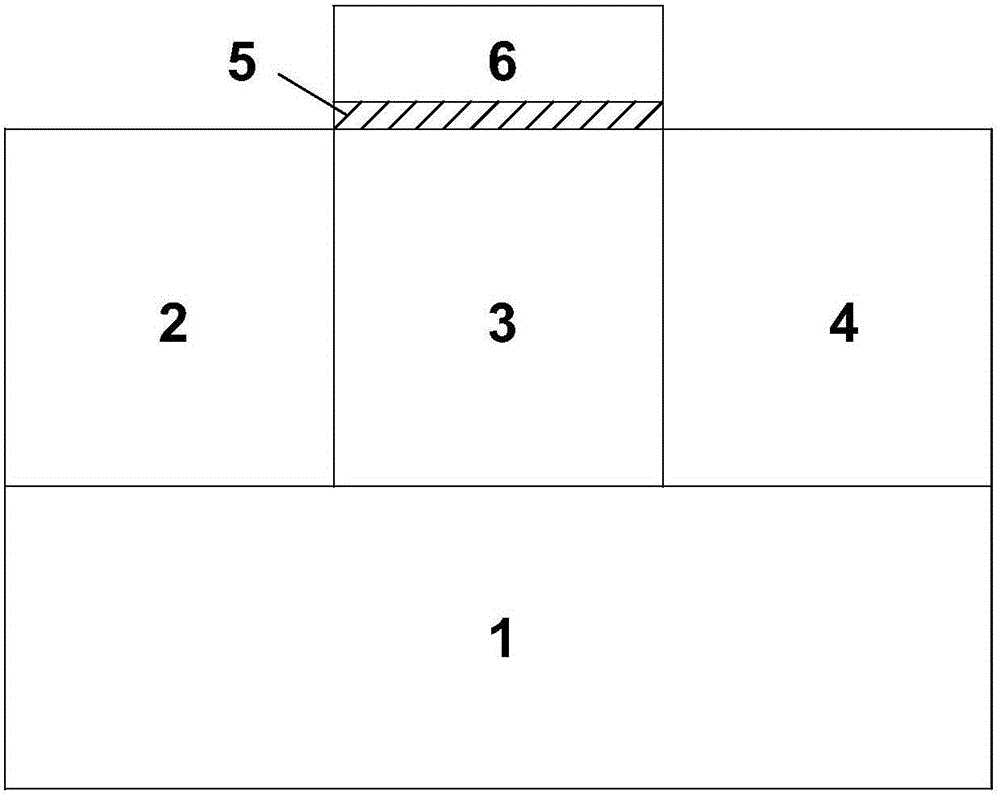

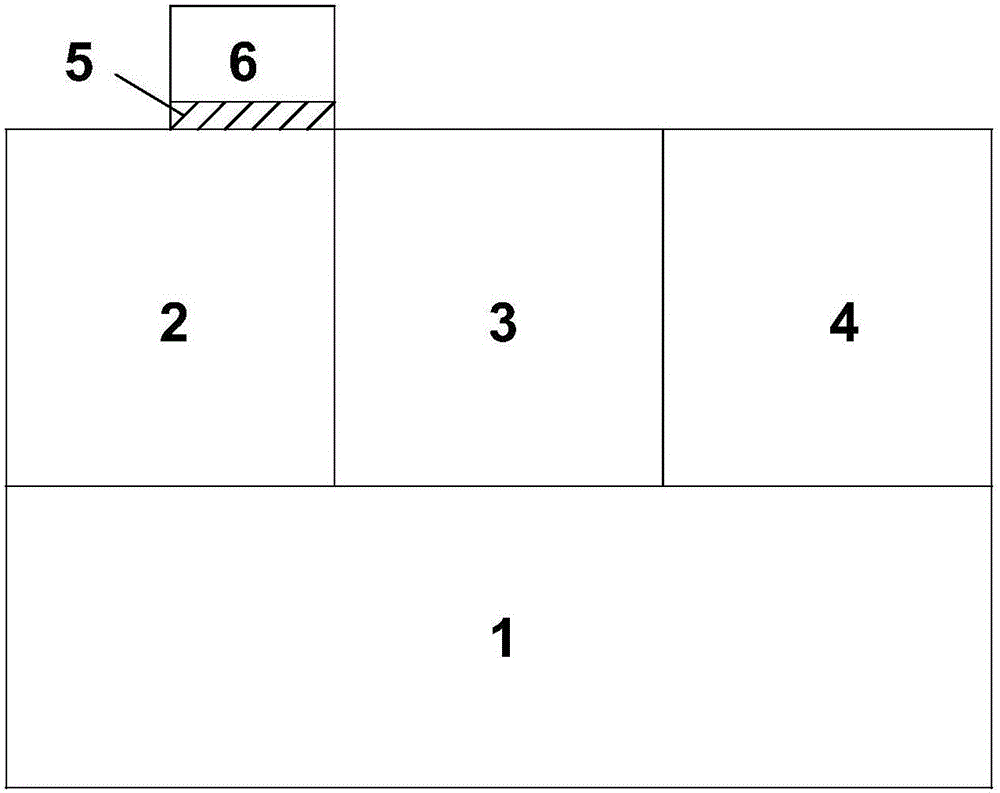

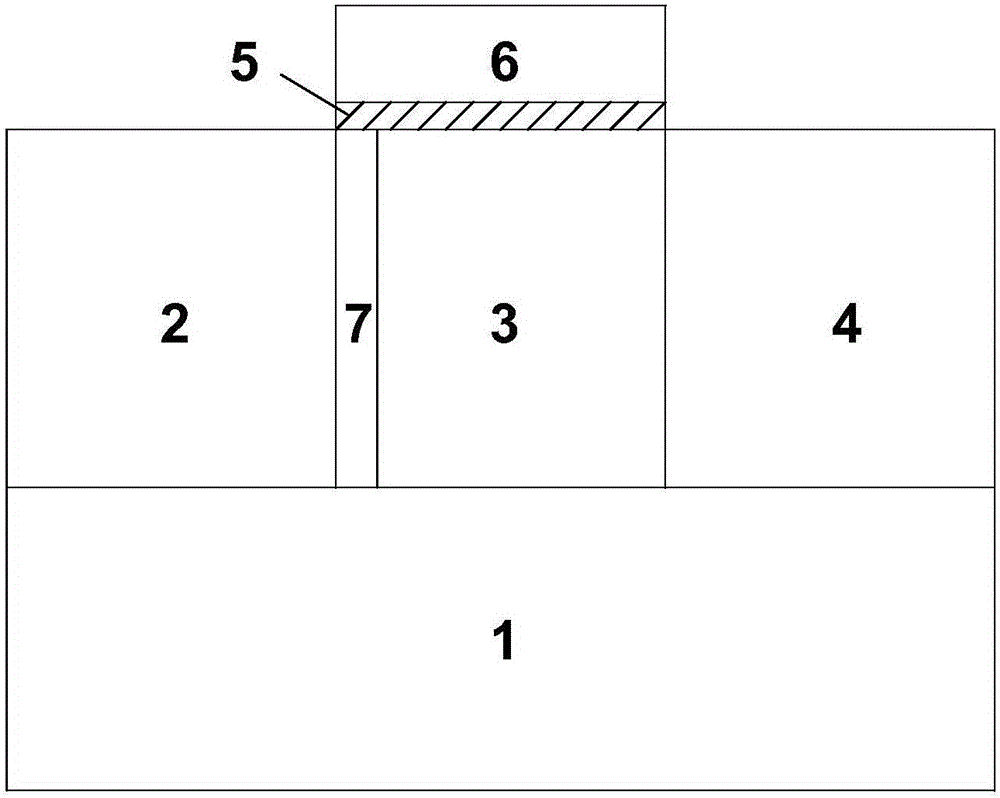

[0033] For the longitudinal tunneling field effect transistor in the embodiment of the present invention, the cross-sectional view of the device can be found in Figure 5 , which includes a semiconductor substrate 1, a source region 2, an intrinsic region 3, a drain region 4, a gate oxide layer 5, a metal gate 6, a buffer layer 10, an epitaxial intrinsic region 11, a stress film 12 and two sidewalls 9, Wherein, the buffer layer 10 is disposed above the semiconductor substrate 1, the source region 2, the intrinsic region 3 and the drain region 4 are respectively disposed above the buffer layer 10, and the two sides of the intrinsic region 3 are connected to the source region 2 and the drain region 4 respectively. The source region 2 and the intrinsic region 3 have the same thickness and are smaller than the thickness of the drain region 4. The epitaxial intrinsic region 11 is arranged above the intrinsic region 3, one side is in contact with the drain region 4, and the other sid...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More