An efficient cdr verification system and method

A verification system and verification method technology, applied in the field of EDA verification, can solve problems such as data and clock errors, reduce simulation efficiency, increase simulation overhead, etc., achieve stability and efficiency satisfaction, improve simulation efficiency, and reduce simulation overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

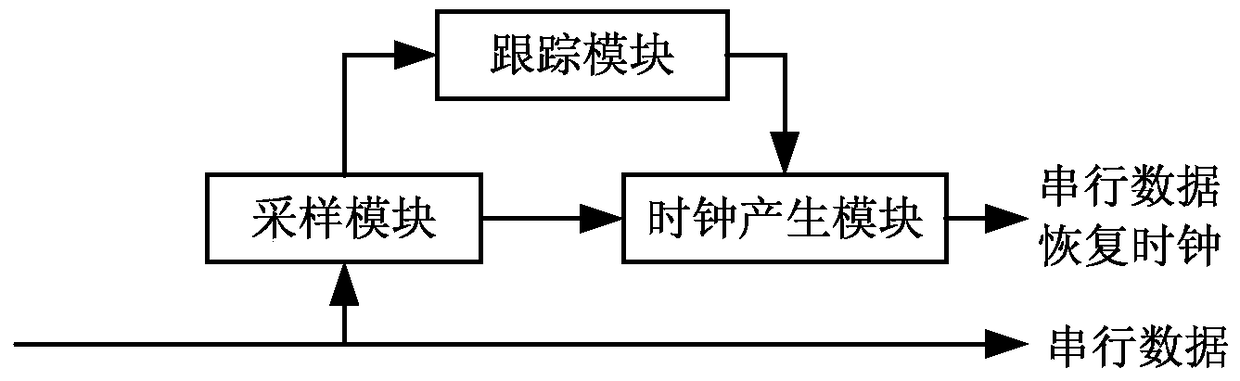

[0027] see figure 1 As shown, the embodiment of the present invention provides an efficient CDR verification system, including a sampling module, a tracking module and a clock generating module, wherein the sampling module is connected to the tracking module and the clock generating module, and the tracking module is connected to the clock generating module.

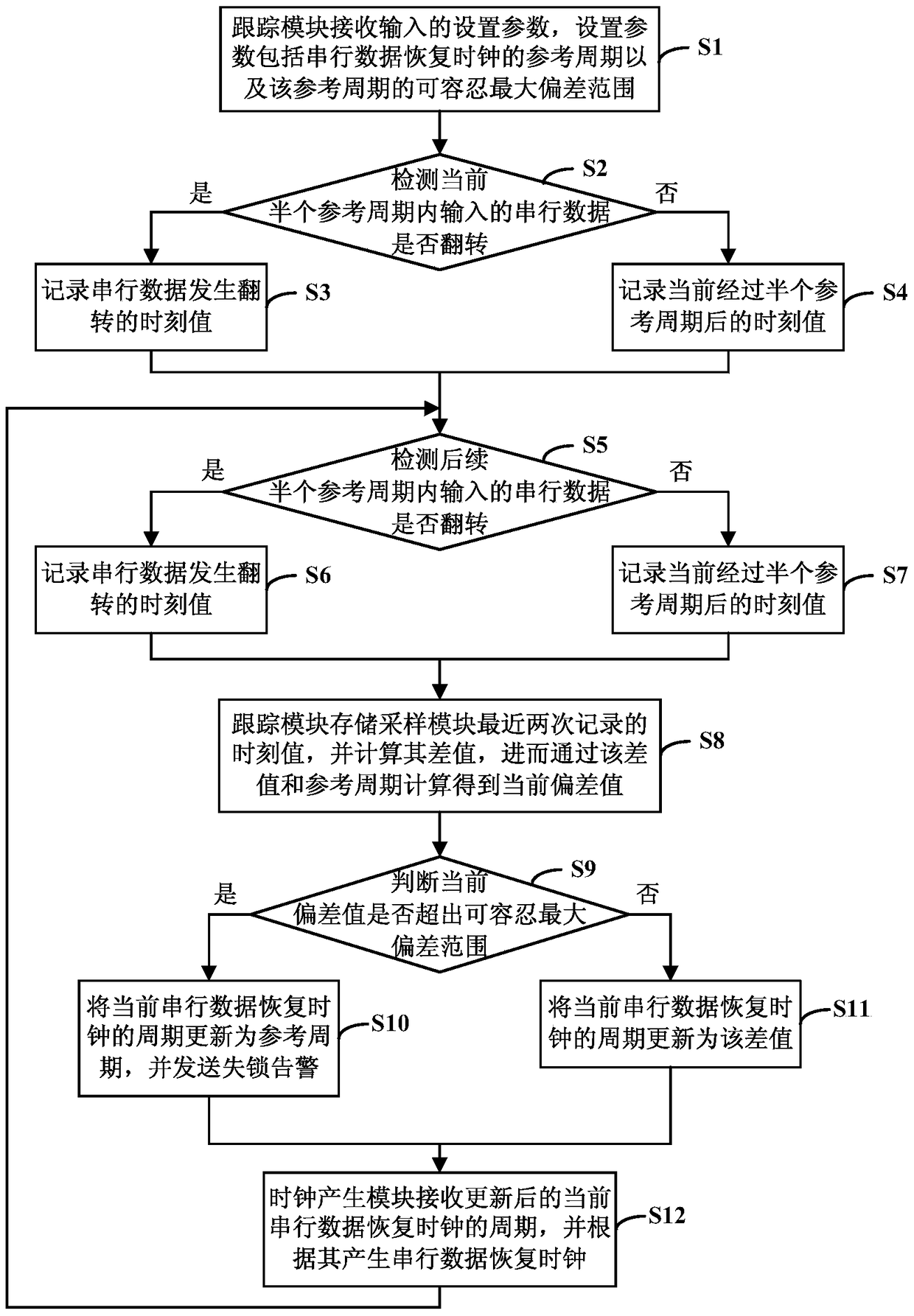

[0028] The sampling module is used to detect whether the input serial data is reversed in every half reference period, and record the time value at which the serial data is reversed or the current time value after half of the reference period has passed.

[0029] The tracking module is used to receive input setting parameters. The setting parameters include the reference period of the serial data recovery clock and the tolerable maximum deviation range of the reference period; the refere...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More