A resistive memory cell

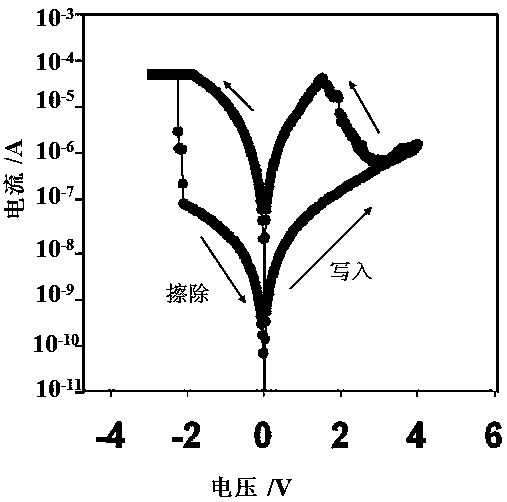

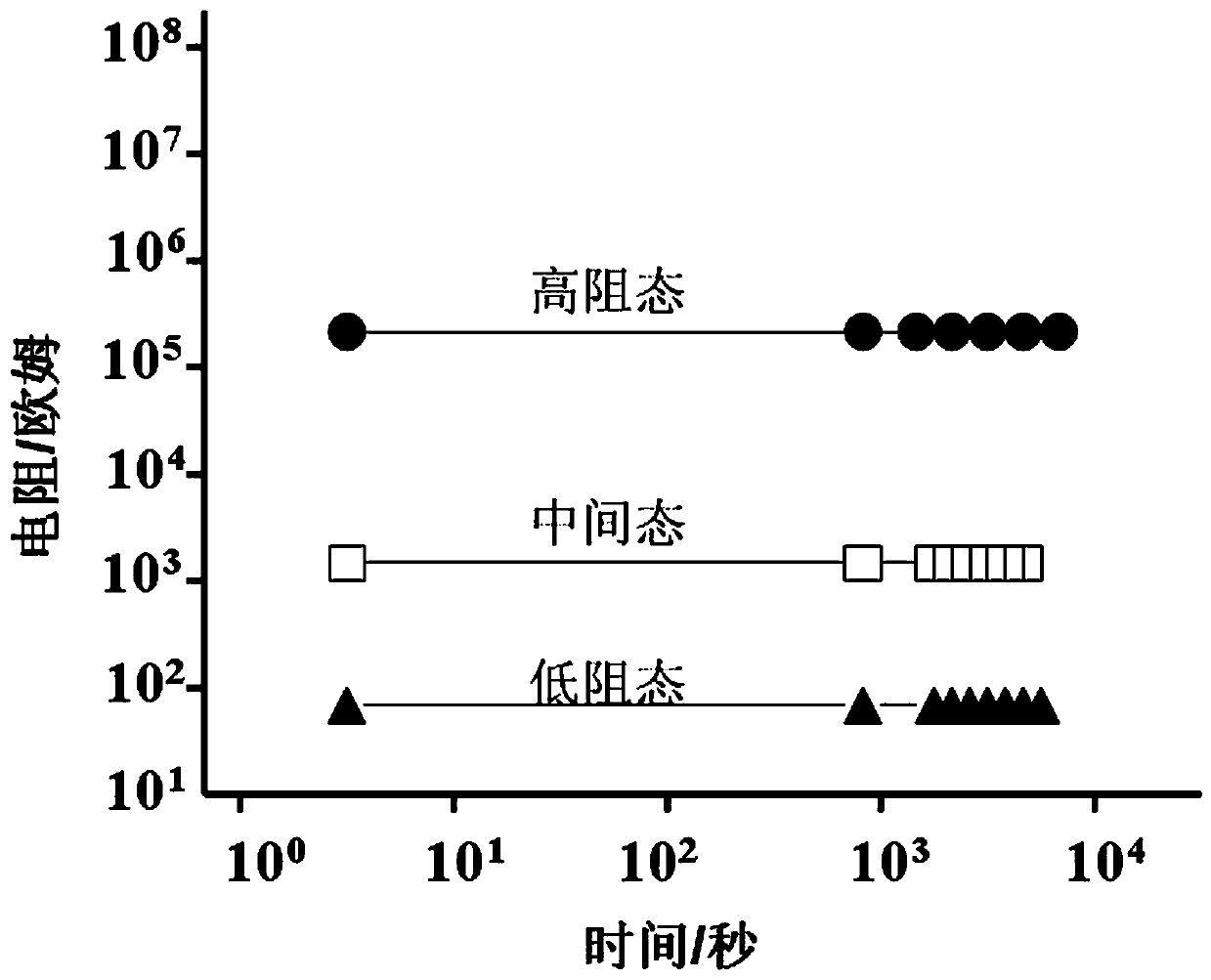

A storage unit and resistance-type technology, applied in electrical components and other directions, can solve the problems of no stable intermediate state and difficult to guarantee the consistency of multi-value storage, so as to improve the storage density and stability, and achieve the effect of stability and consistency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

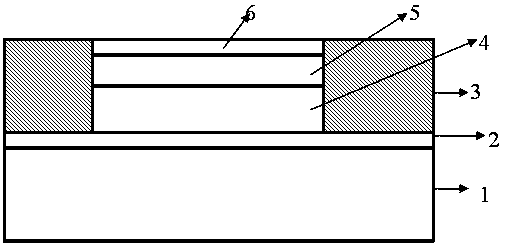

[0035] A preparation method of a resistive memory cell, the steps are as follows:

[0036] (1) The lower electrode layer is formed on the substrate by magnetron sputtering coating method: a metal Cu target is used, and Ar gas is used as the working gas to form a Cu thin film on the glass substrate by sputtering, and the working pressure during sputtering is 5 ×10 -1 Pa~10×10 - 1 Pa, the sputtering time is 20~25min, the sputtering voltage is 300~380V, the sputtering current is 120~180mA, and finally a Cu lower electrode layer with a thickness of about 80-150nm is formed on the glass substrate;

[0037] (2) Form an insulating dielectric layer on the Cu lower electrode layer: the method of forming the insulating dielectric layer can be atomic layer deposition or spin coating, and the thickness of the insulating dielectric layer is 300nm~5000nm. Material can be SiO 2 Or SiN, after the insulating dielectric layer is formed, a trench is formed on the insulating dielectric layer ...

Embodiment 2

[0042] A preparation method of a resistive memory cell, the steps are as follows:

[0043] (1) Use a metal Pt target, use Ar gas as the working gas, and form a Pt film on a semiconductor substrate by sputtering. The semiconductor substrate can be a Si substrate, and the working pressure during sputtering is 5×10 -1 Pa~10×10 -1 Pa, the sputtering time is 20~45min, the sputtering voltage is 300~380V, the sputtering current is 120~180mA, and a Pt lower electrode layer with a thickness of about 80-150nm is formed;

[0044] (2) Form an insulating dielectric layer on the Pt lower electrode layer. The method of forming the insulating dielectric layer can be deposition or spin coating. The thickness of the insulating dielectric layer is 300nm~5000nm. The material of the insulating dielectric layer can be SiO 2 Or SiN material, after forming the insulating dielectric layer, using a traditional photolithography process to form a trench on the insulating dielectric layer to form other ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More