Patents

Literature

34results about How to "Implement multi-value storage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

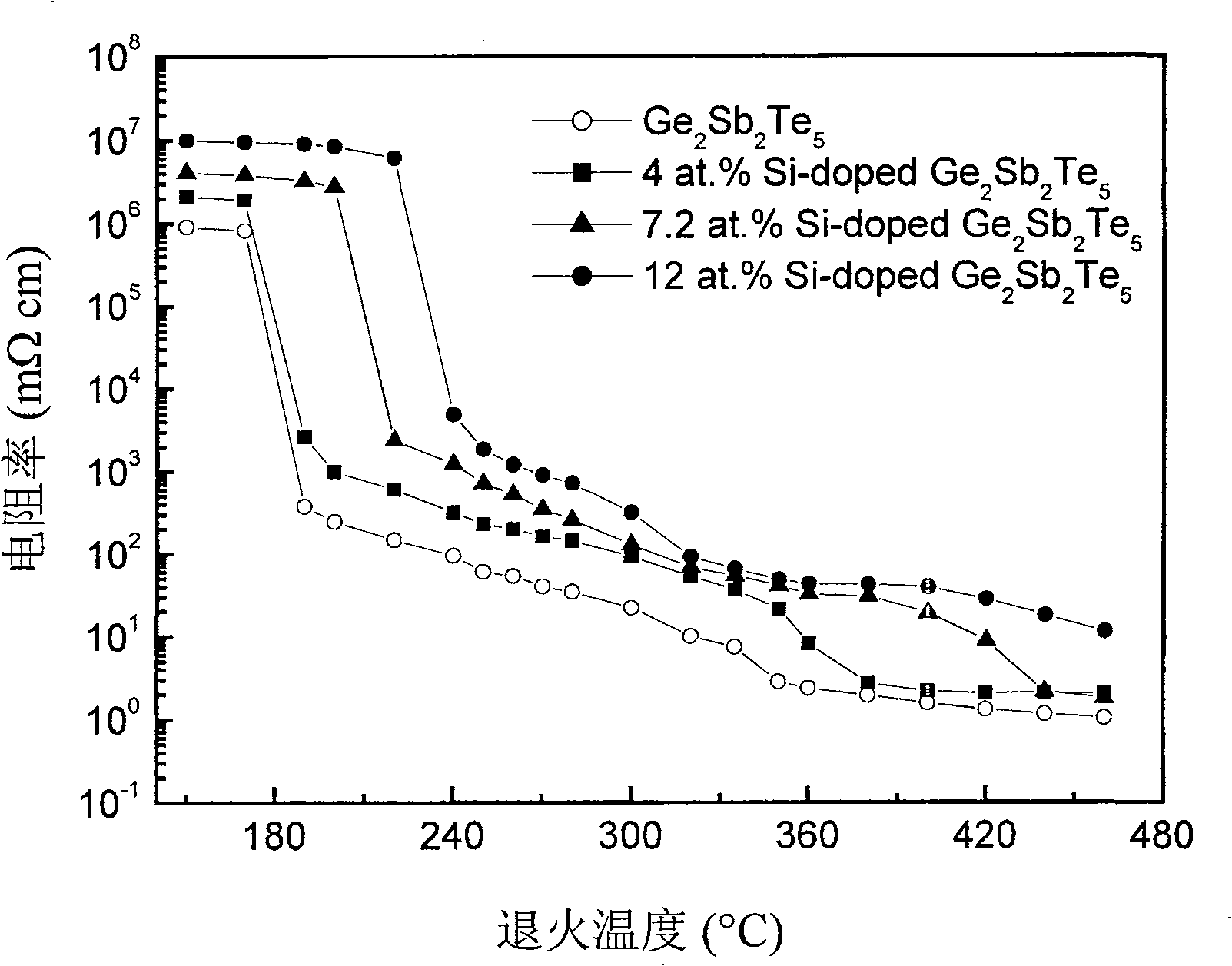

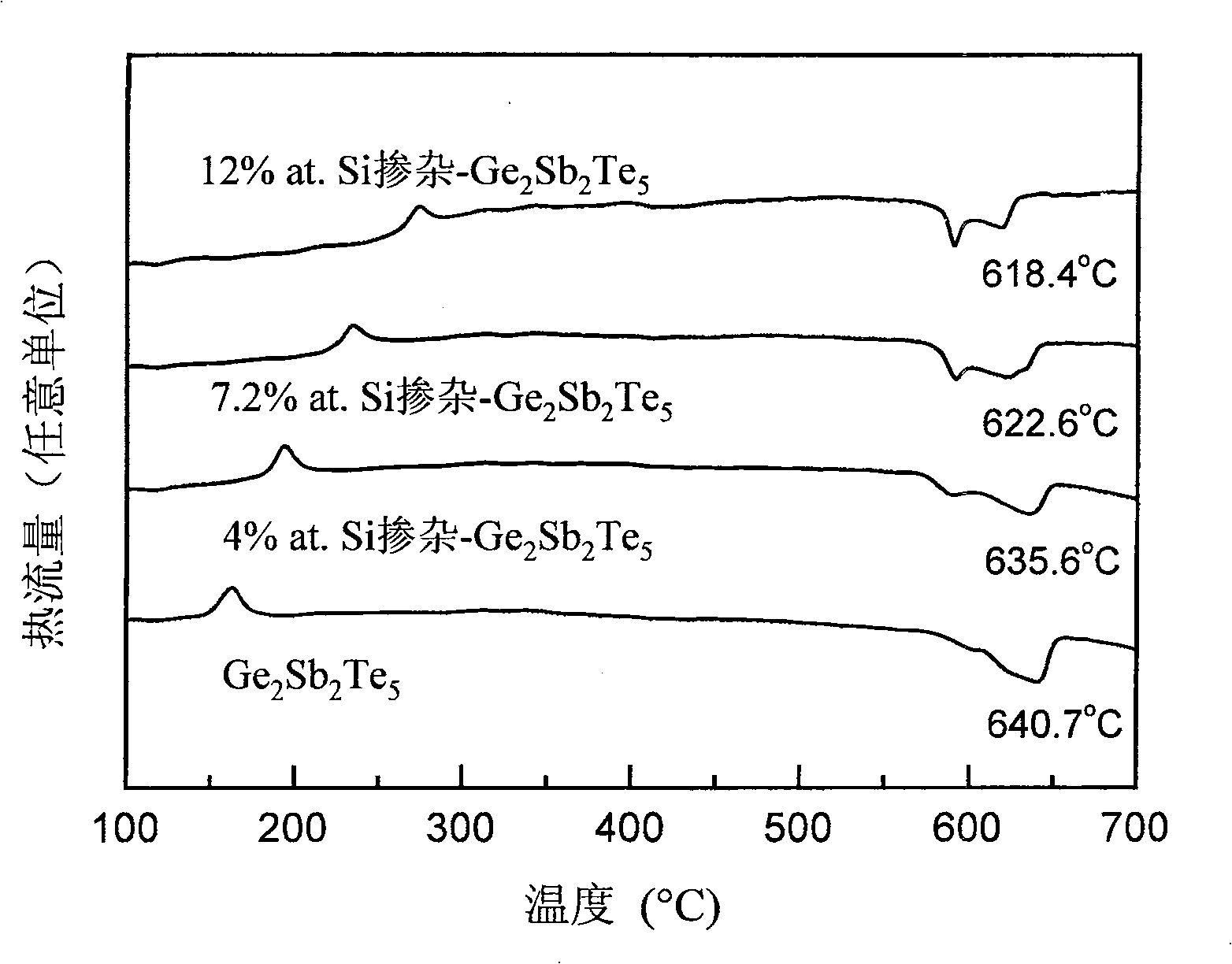

Phase change film material of silicon-adulterated sulfur series for phase change memory

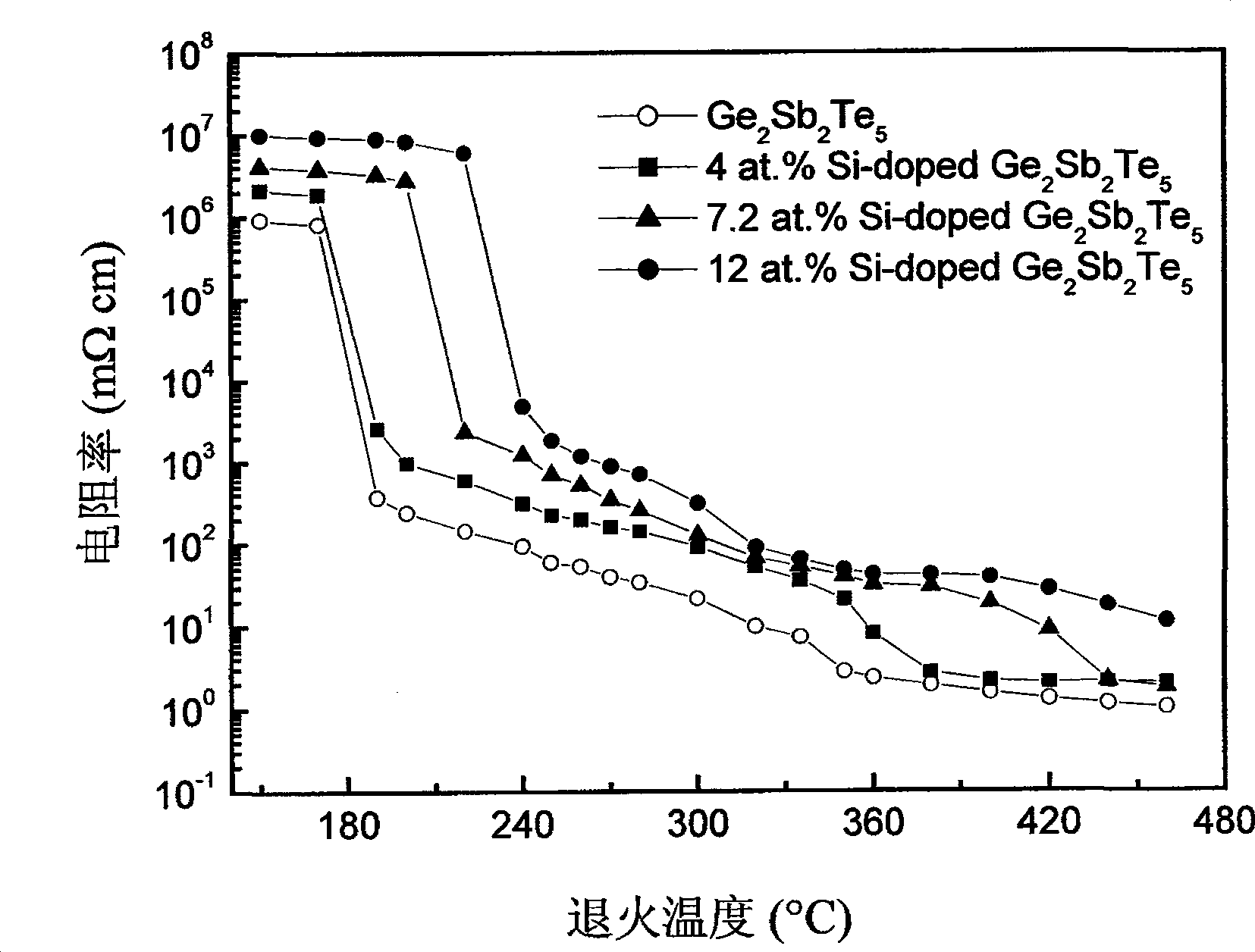

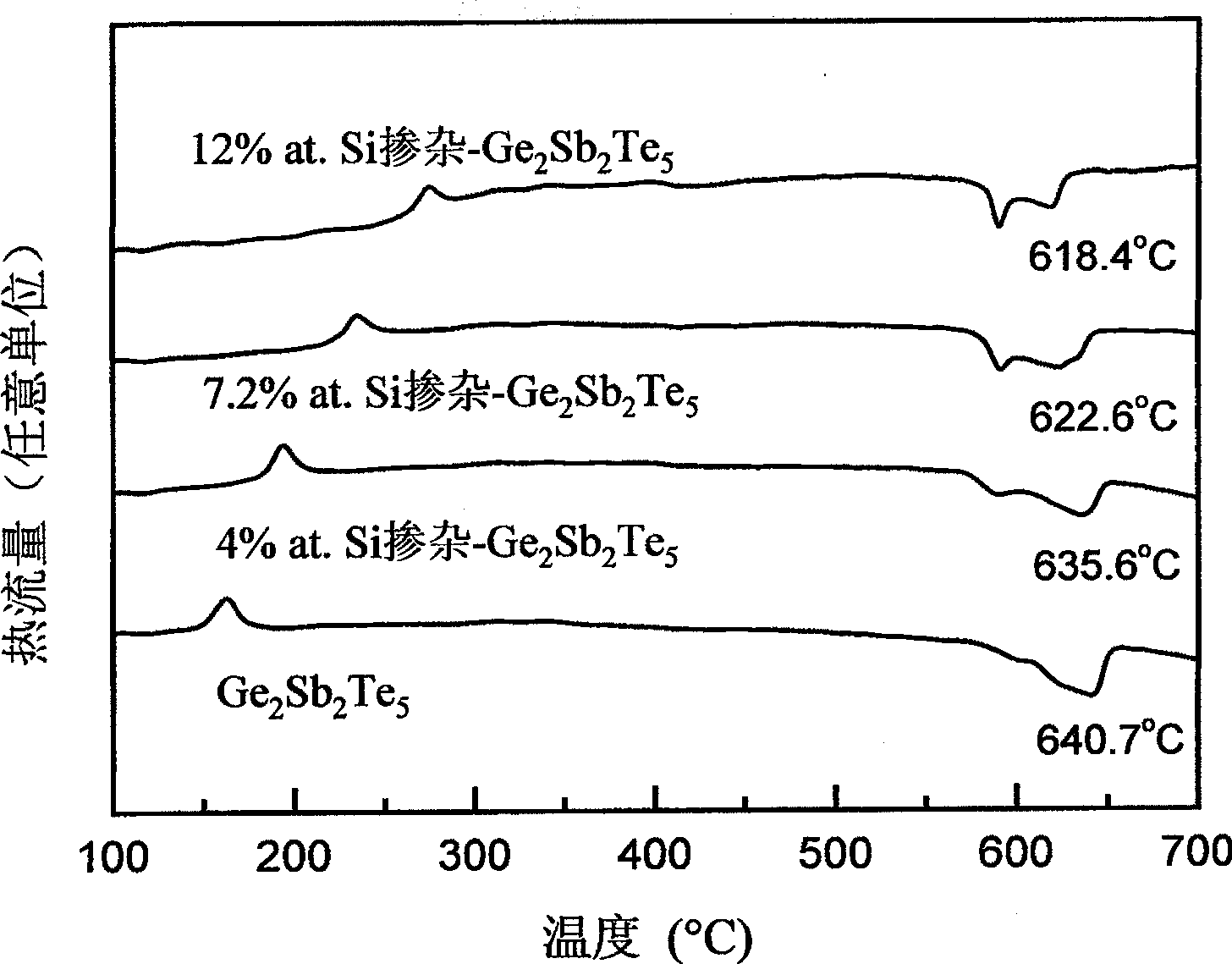

InactiveCN101101965AEasy transferLower write operation currentChalcogenide/metal/alloy compound compositionsElectrical apparatusElectrical resistance and conductancePhase-change memory

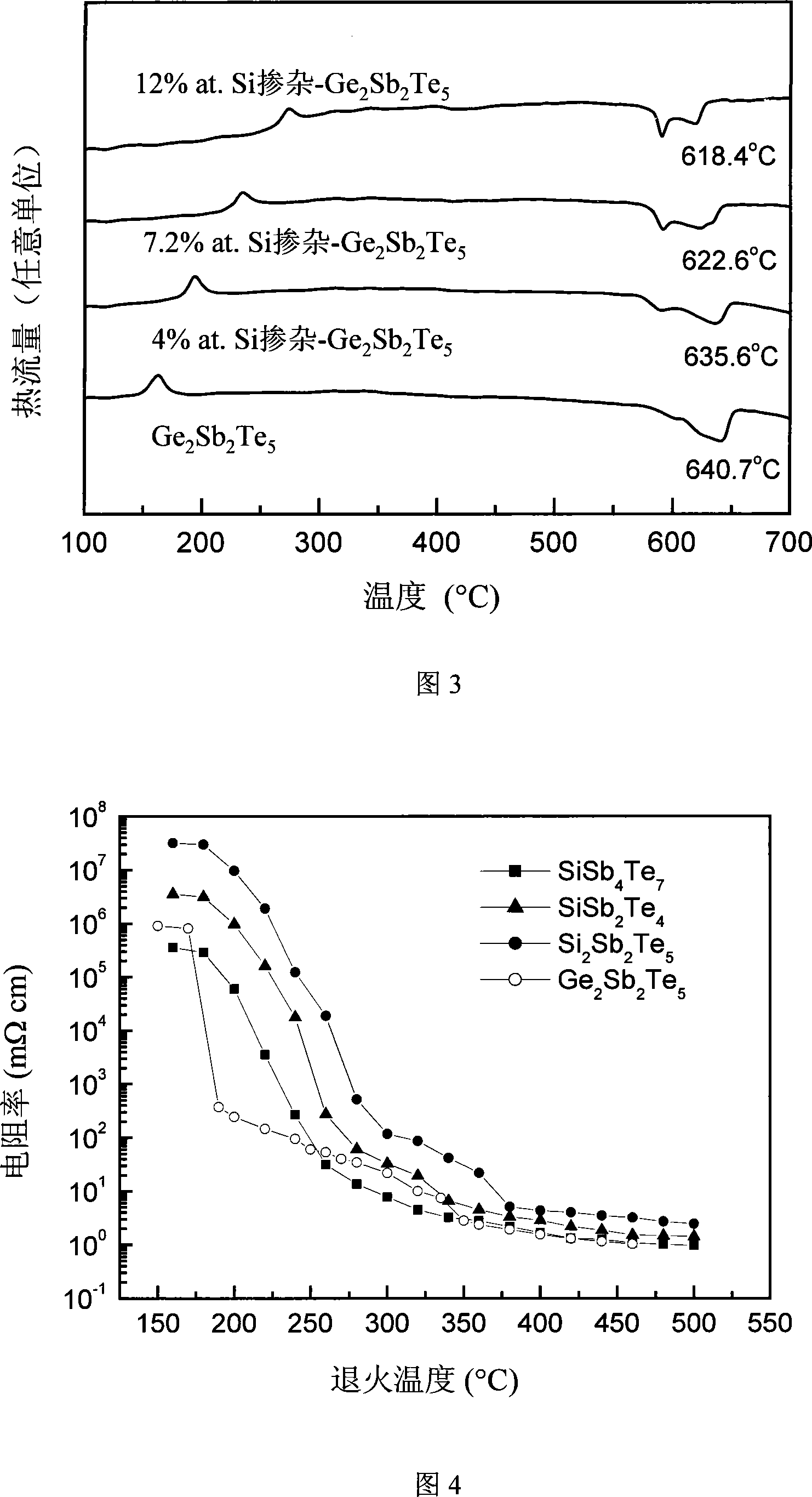

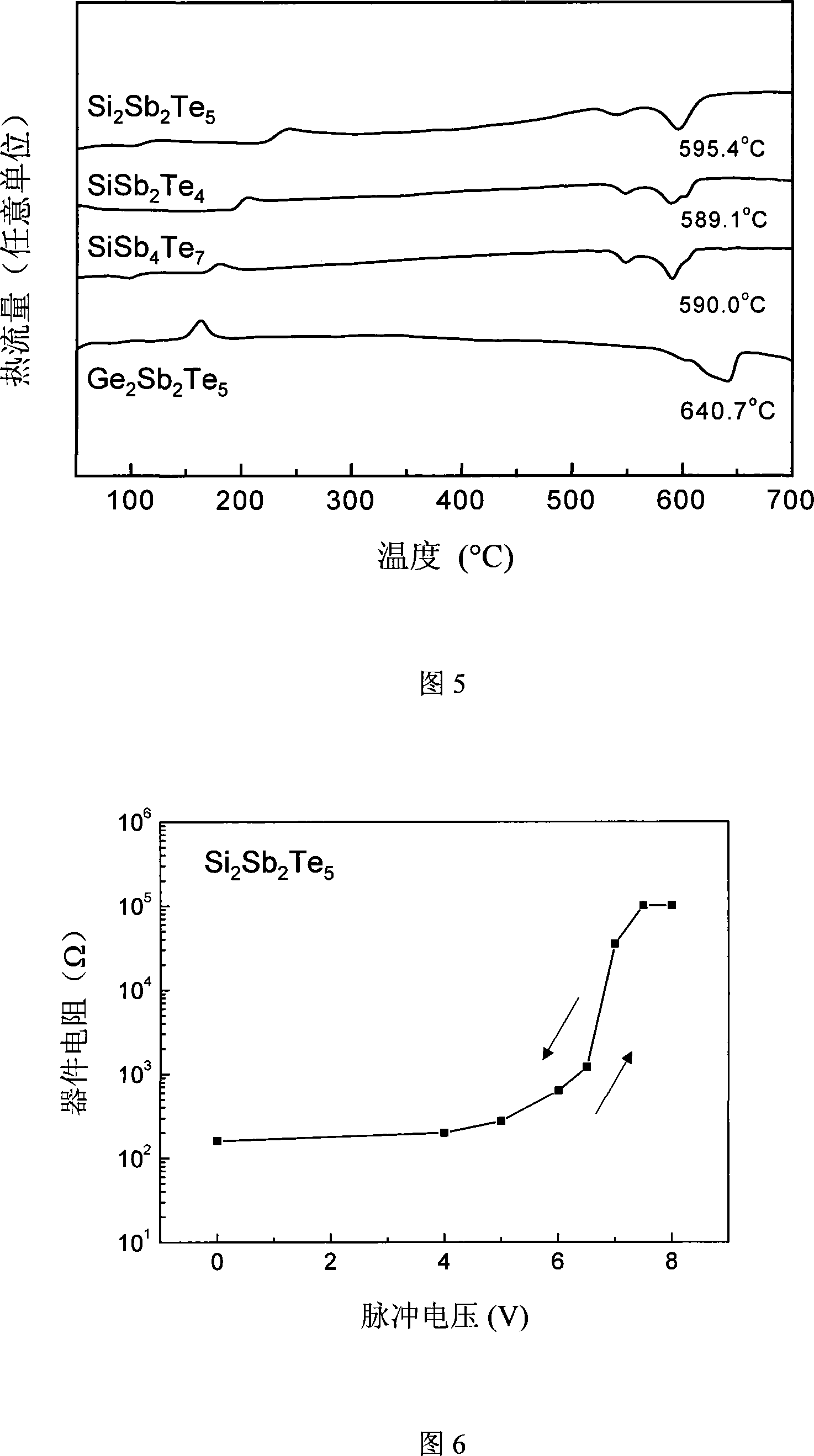

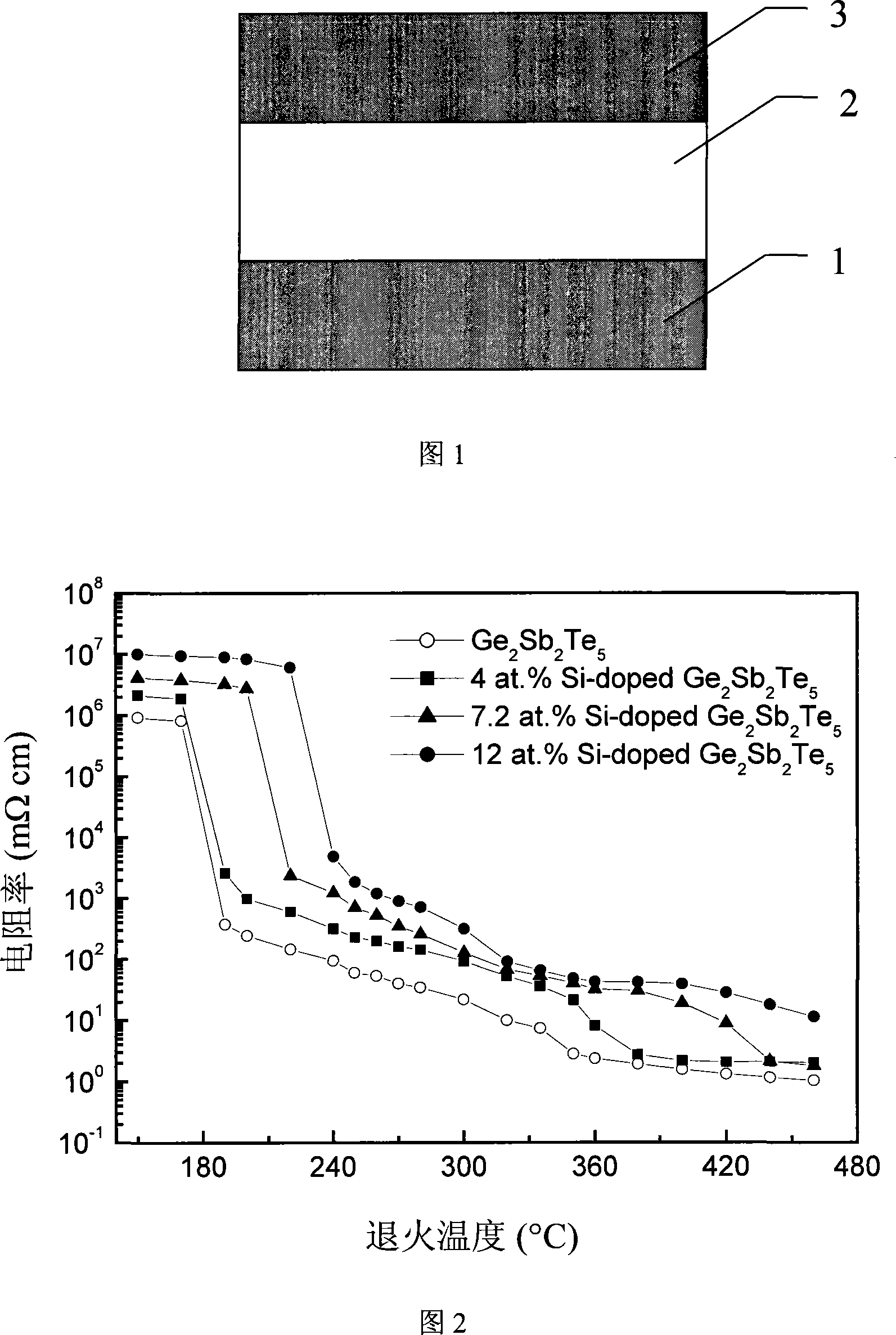

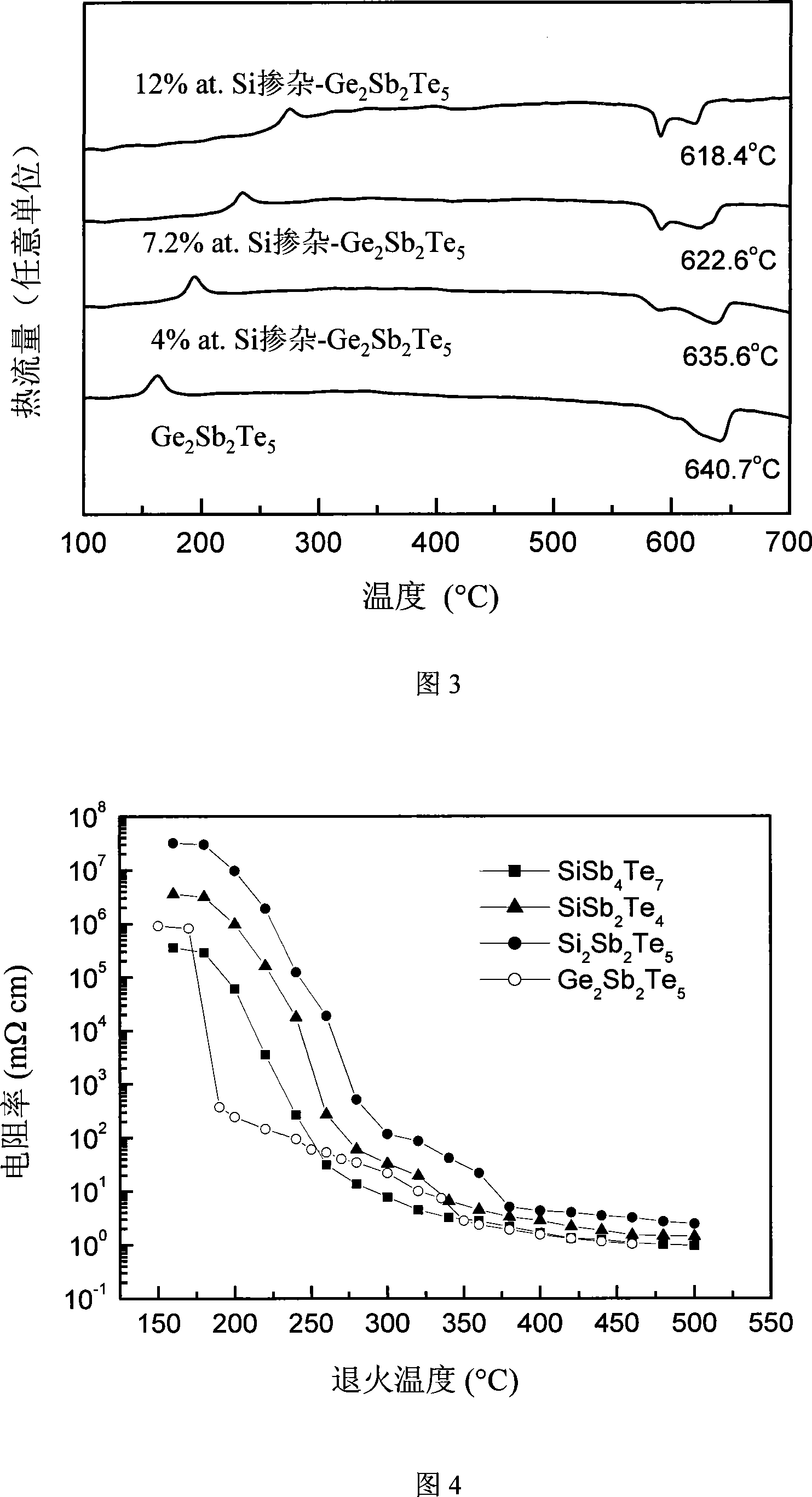

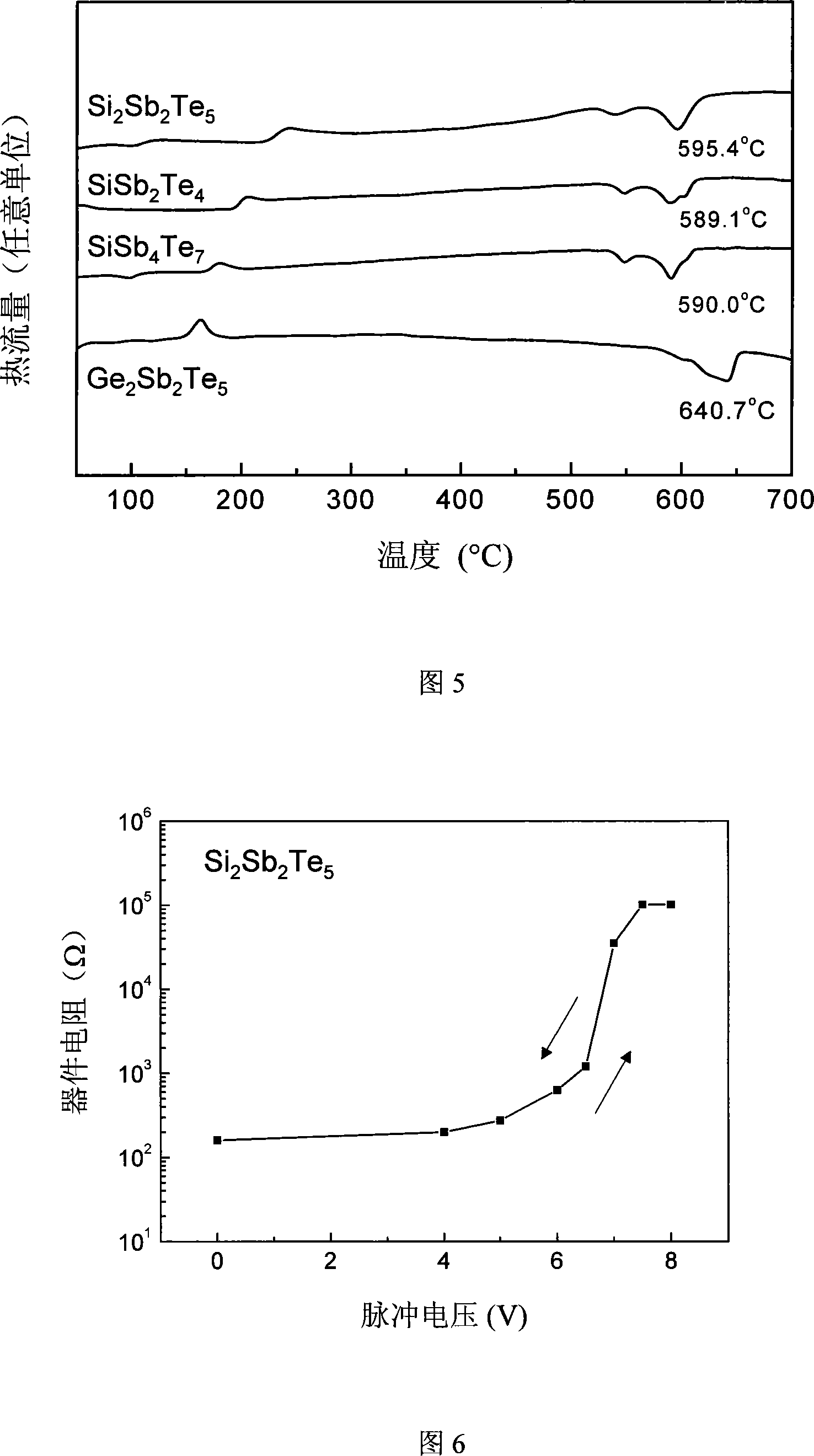

The invention is concerned with the phase change film material containing silicon series cluster subject, that is the silicon group subject alloy TeaSibSb100-(a+b) with the a no lesser than 48 but no more than 60, and the b no less than 8 but no more than 40. The invention has the higher crystalline state resistance and non / crystalline resistance change ratio compare to the Ge2Sb2Te5 phase change film, the lower change ratio of the non / crystalline film thickness and melting point. The memorizer including the Si series sulfur group subject phase change film is with the higher ratio sum of the switch stability and it helps the writing operation current.

Owner:SHANGHAI JIAO TONG UNIV +1

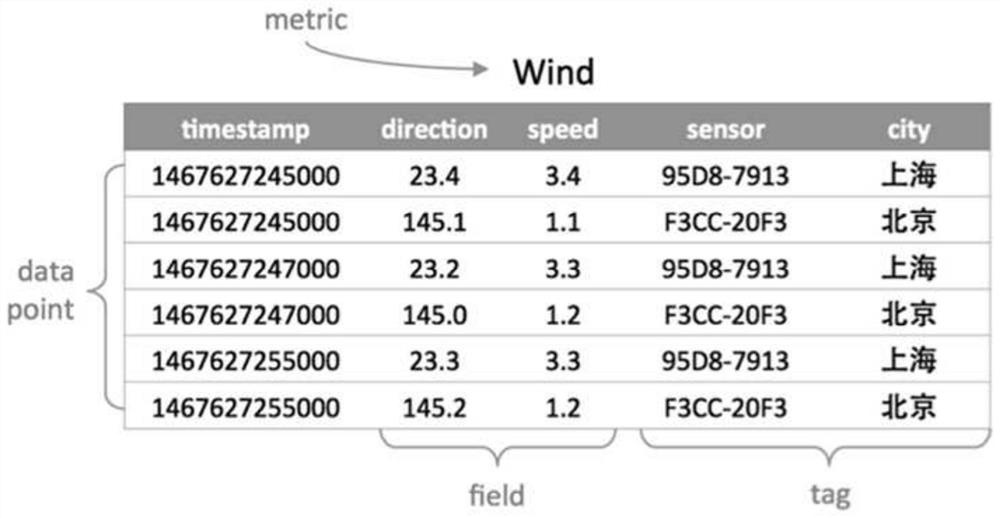

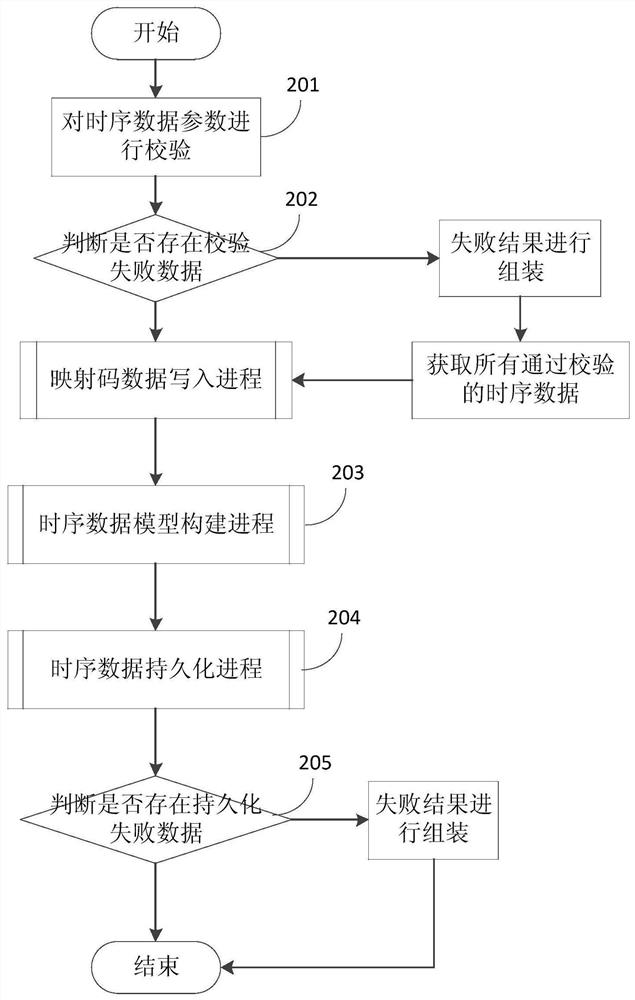

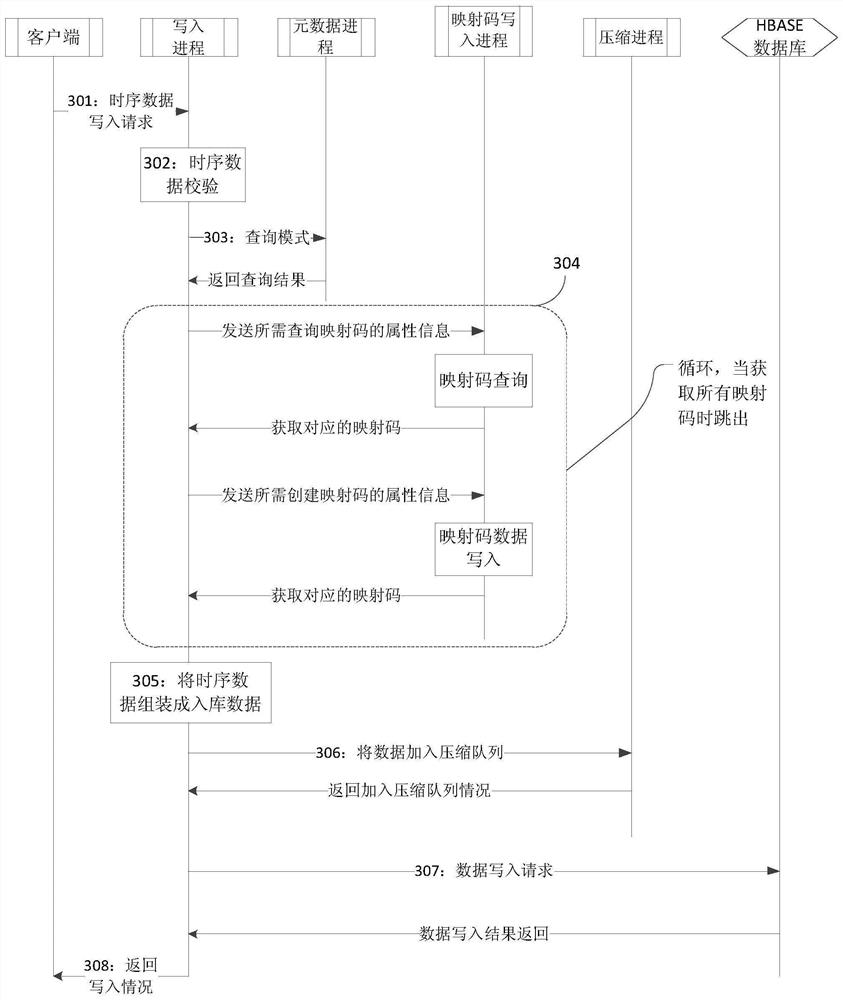

Time series data storage method and device

PendingCN111813782AImplement multi-value storageReduce redundancySpecial data processing applicationsDatabase indexingAlgorithmEngineering

The invention discloses a time series data storage method, which comprises the steps of processing to-be-stored time series data into a defined data structure, and assembling the defined data structure into storage data; wherein the data structure at least comprises a measurement name, a label key, measurement and a time precision field of the time series data; wherein the warehouse-in data takesa mapping code at least comprising a measurement name mapping code, a timestamp and a label value included in a label key as a row key in the data point and takes a time difference relative to the timestamp as a limiter in the data point, and the time difference is related to time precision; and writing the storage data into a time sequence database. According to the method and the device, the label data which can be contained in the row key in the data point is improved, the multi-value storage of the time series data is realized, and the storage pressure caused by splitting the time series data is avoided.

Owner:HANGZHOU HIKVISION DIGITAL TECH

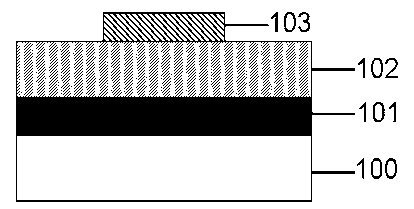

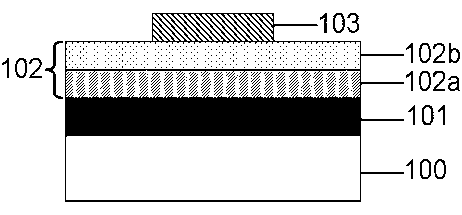

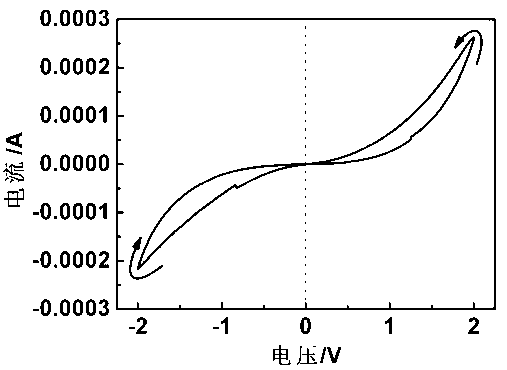

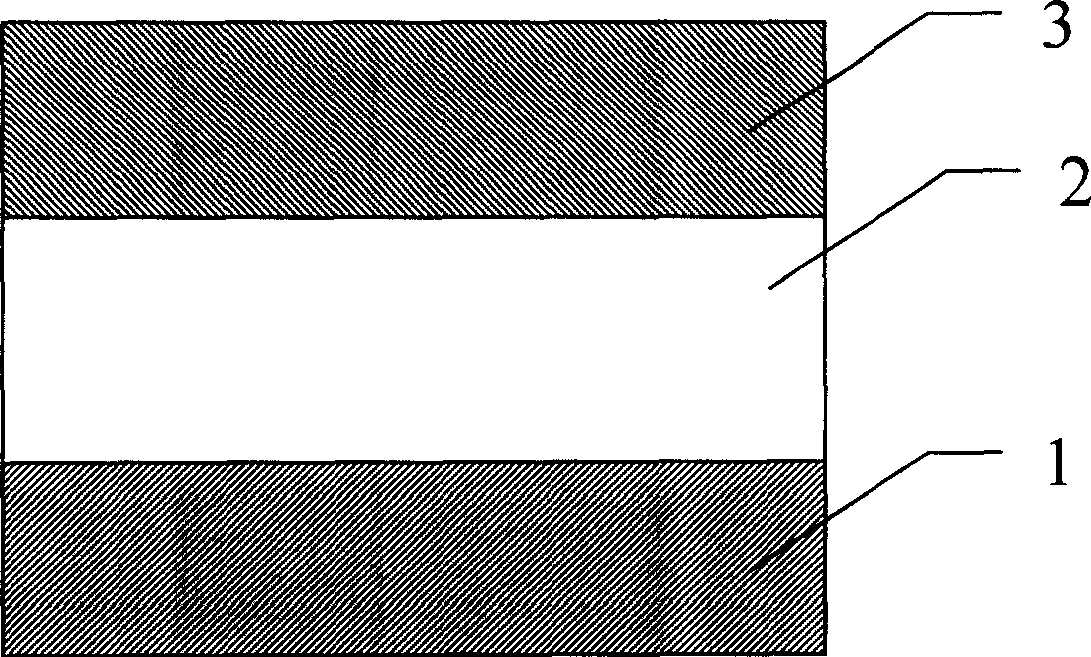

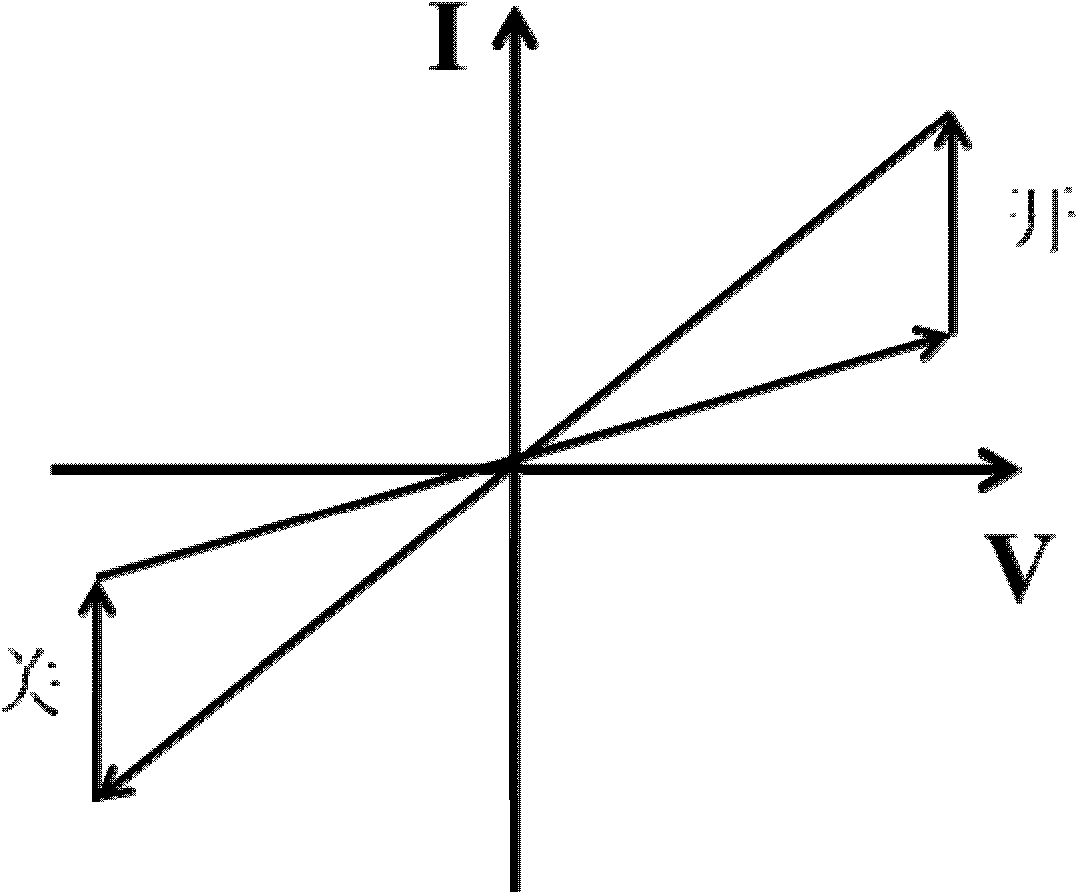

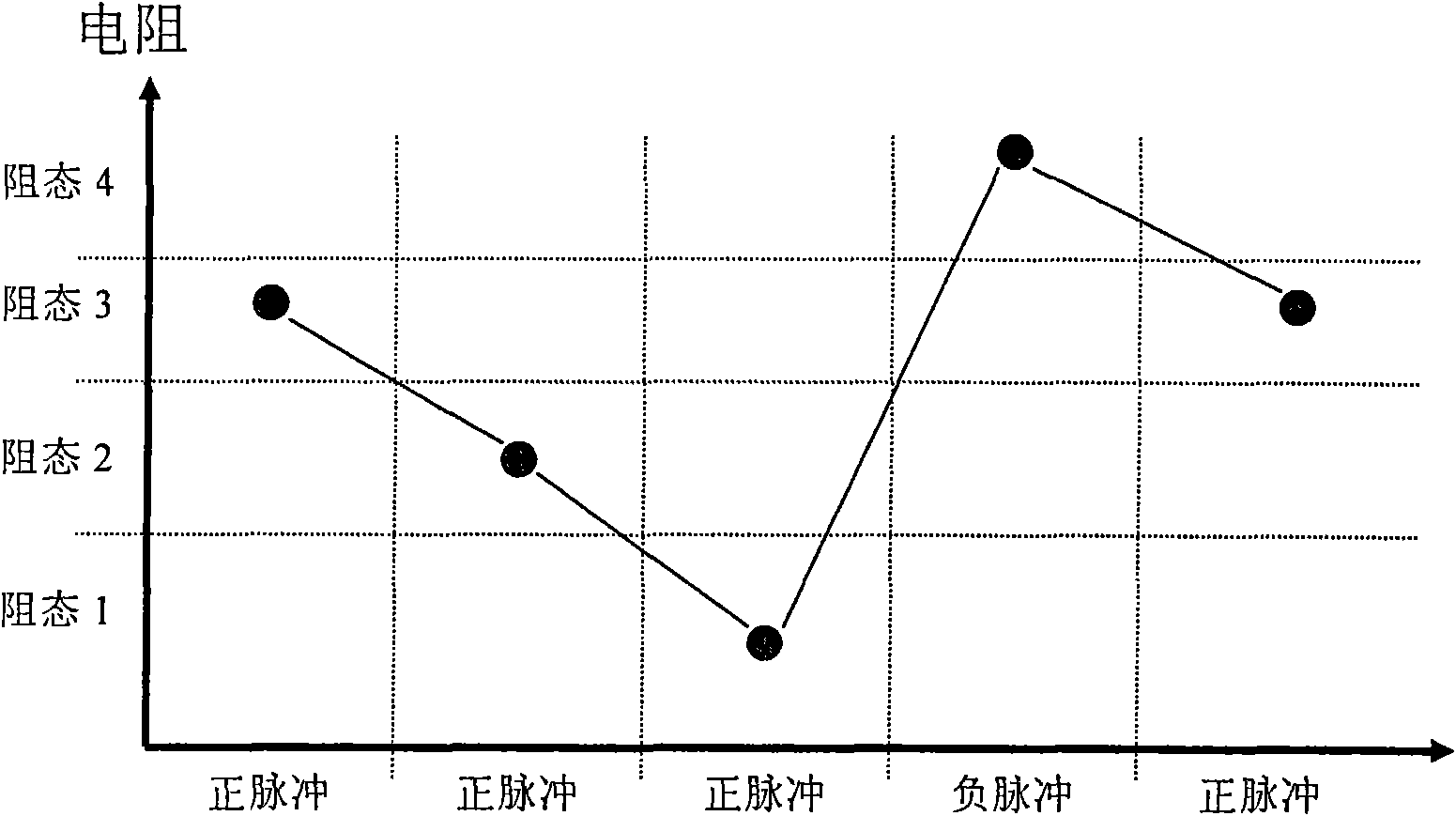

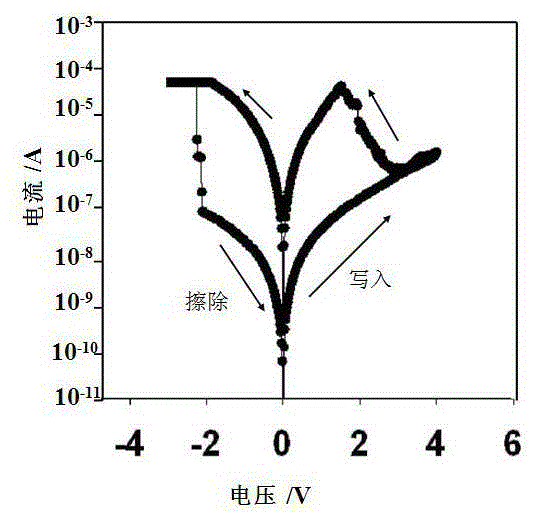

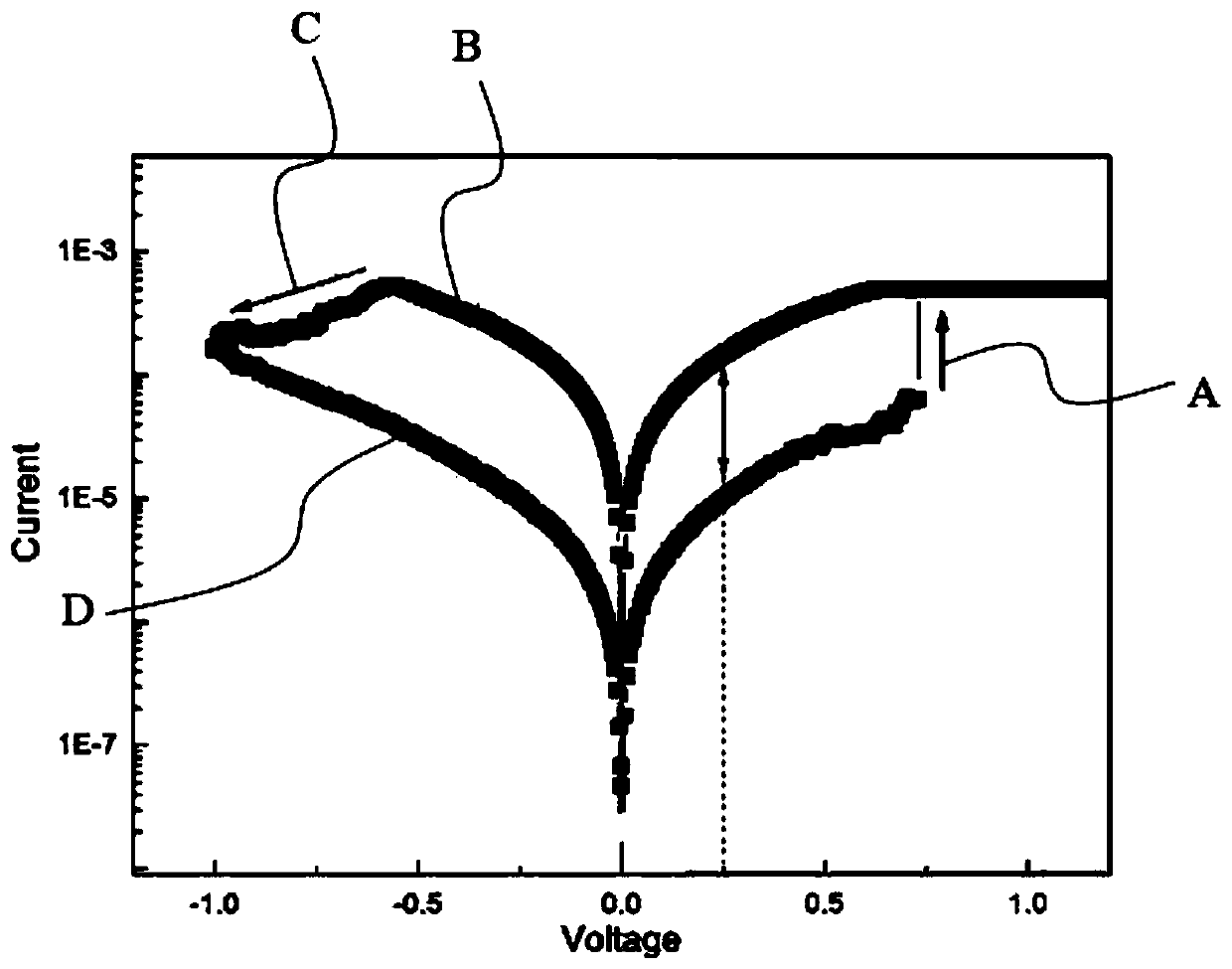

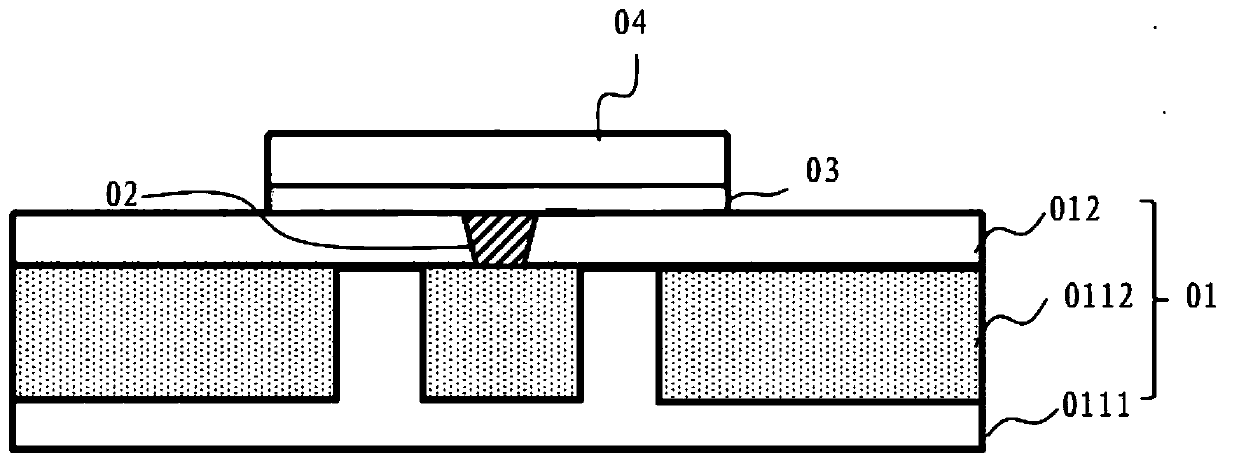

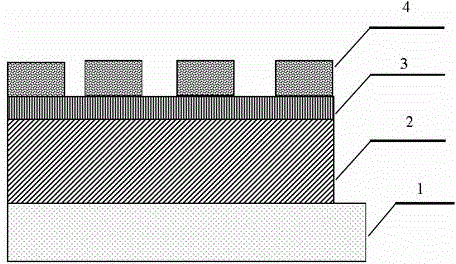

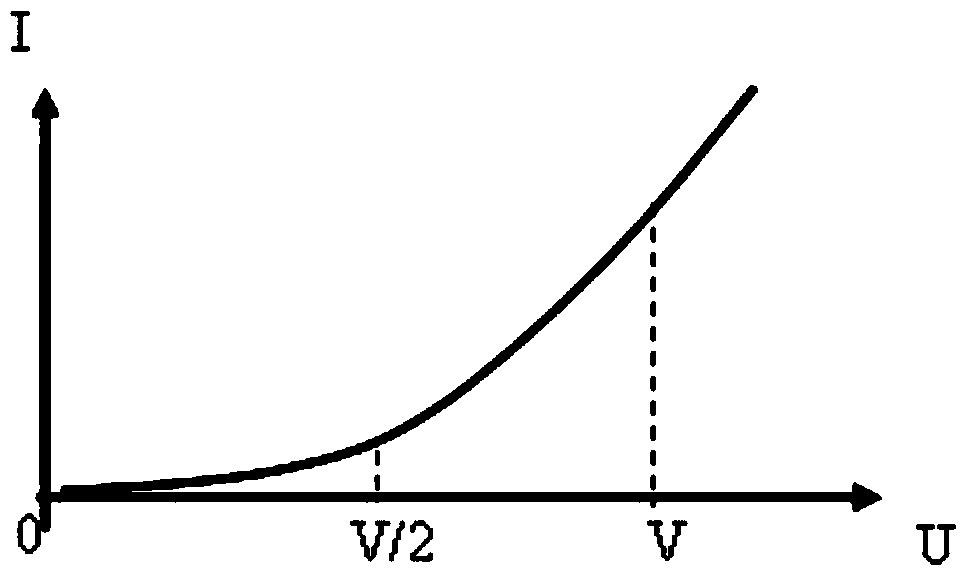

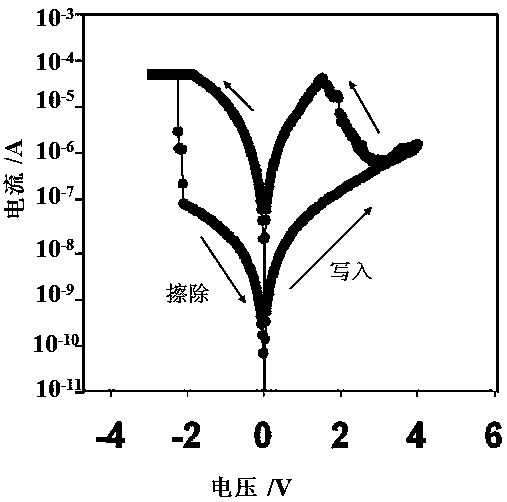

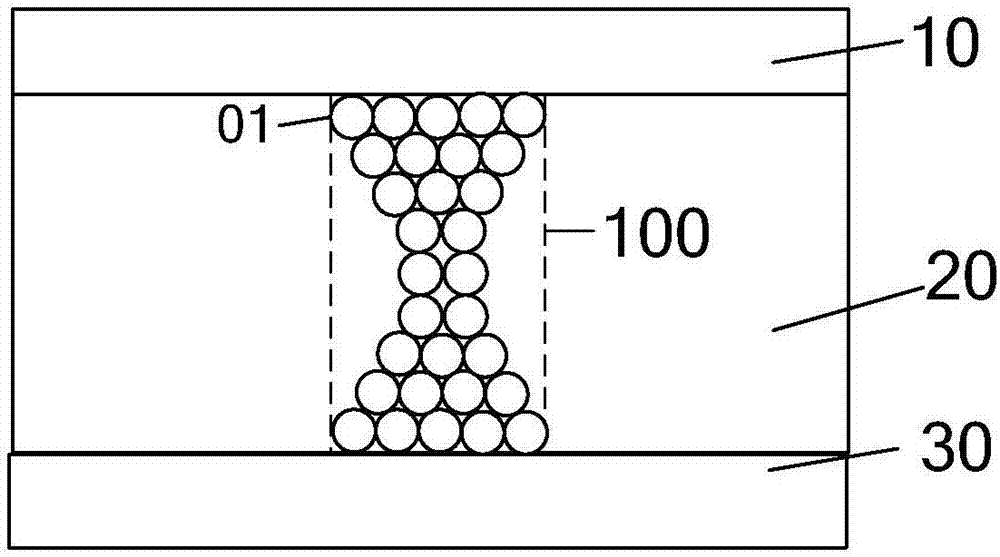

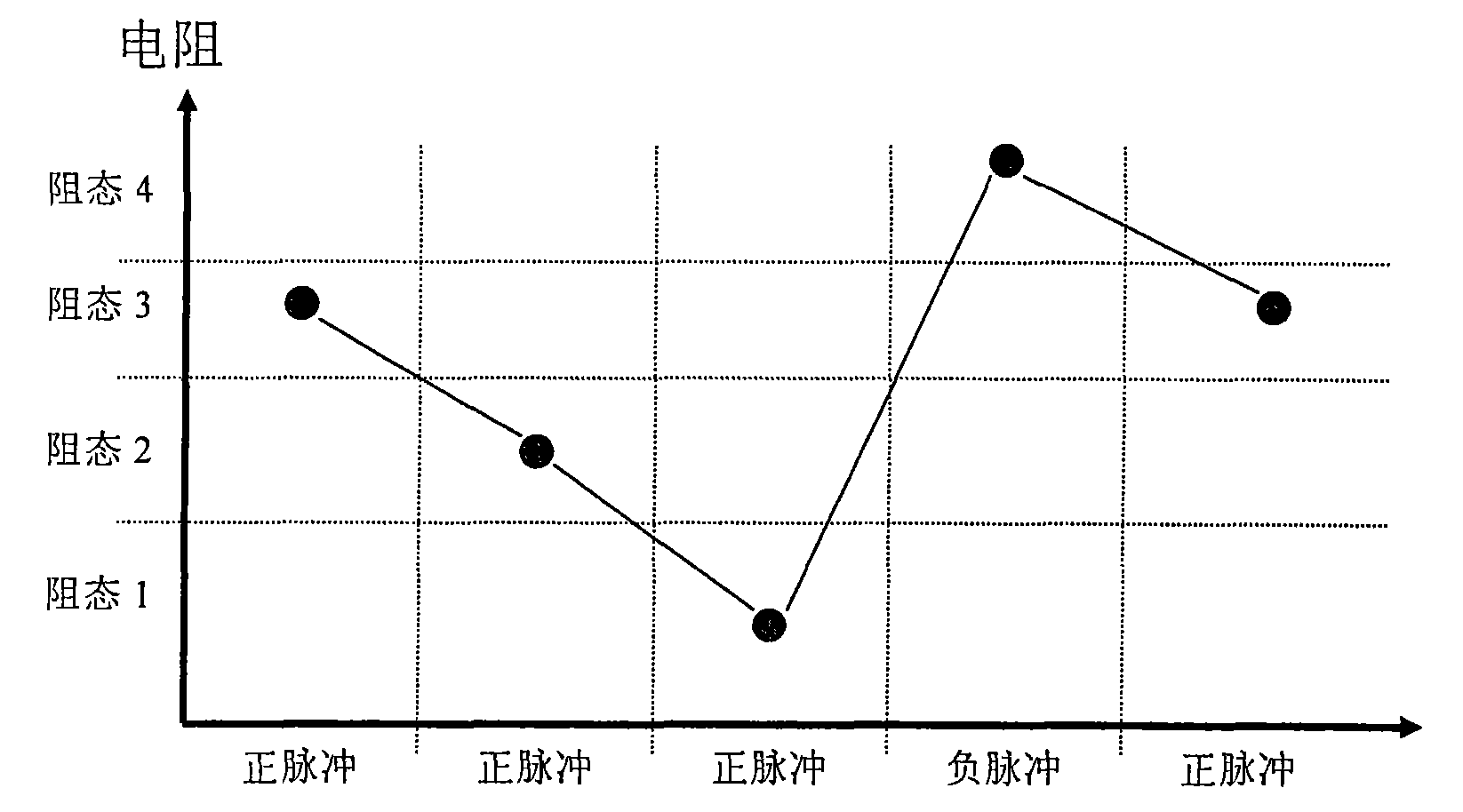

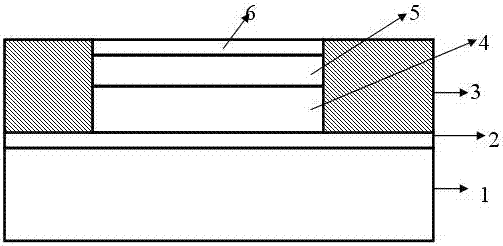

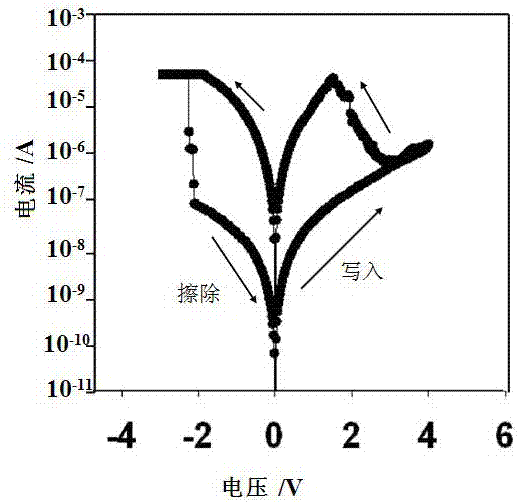

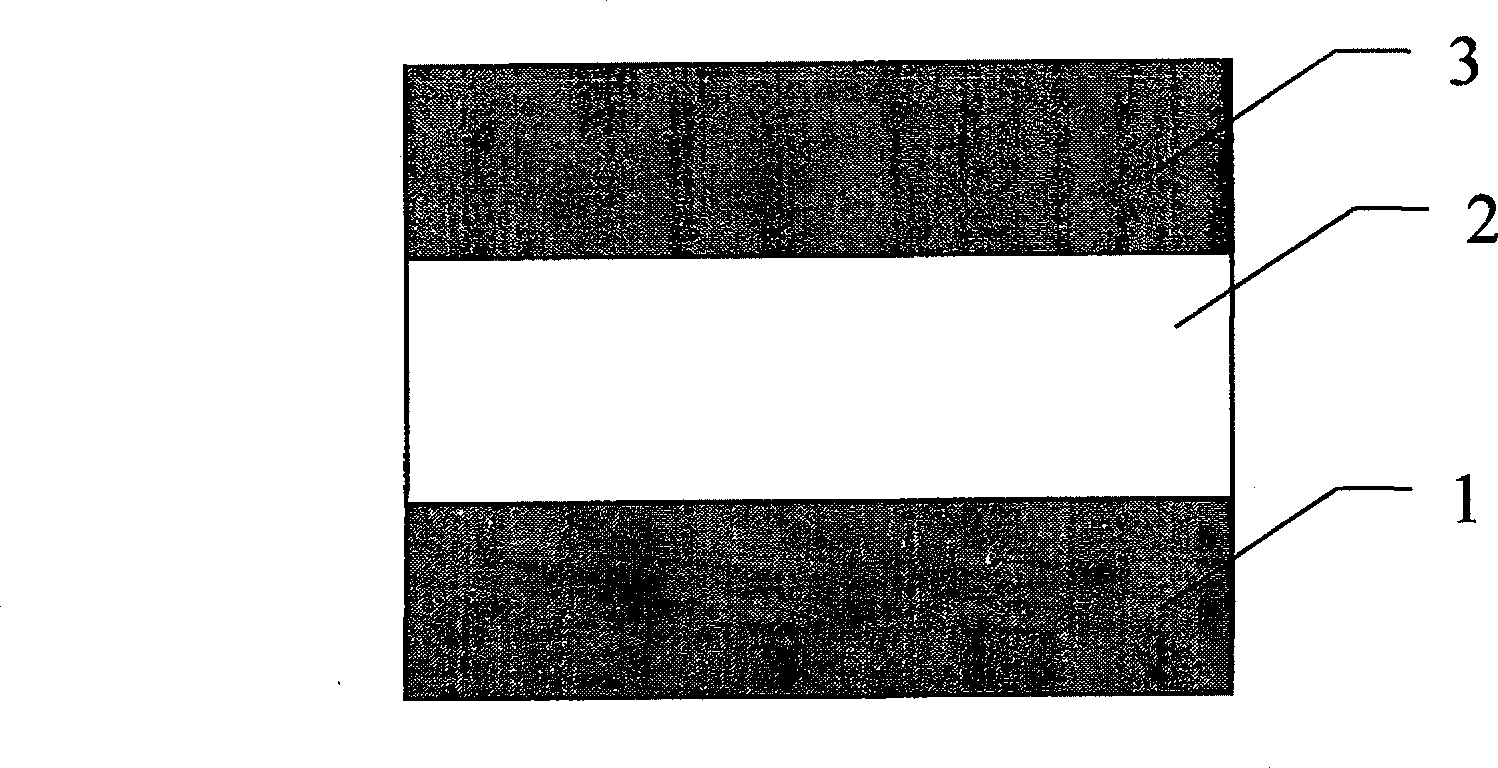

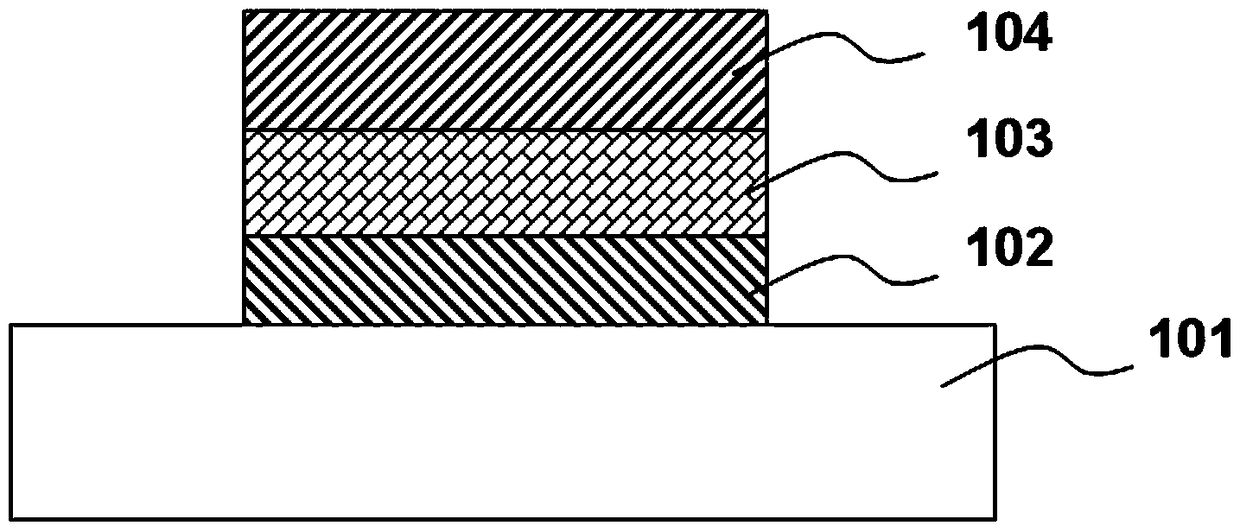

Semiconductor device possessing memristor characteristic and method for realizing multilevel storage

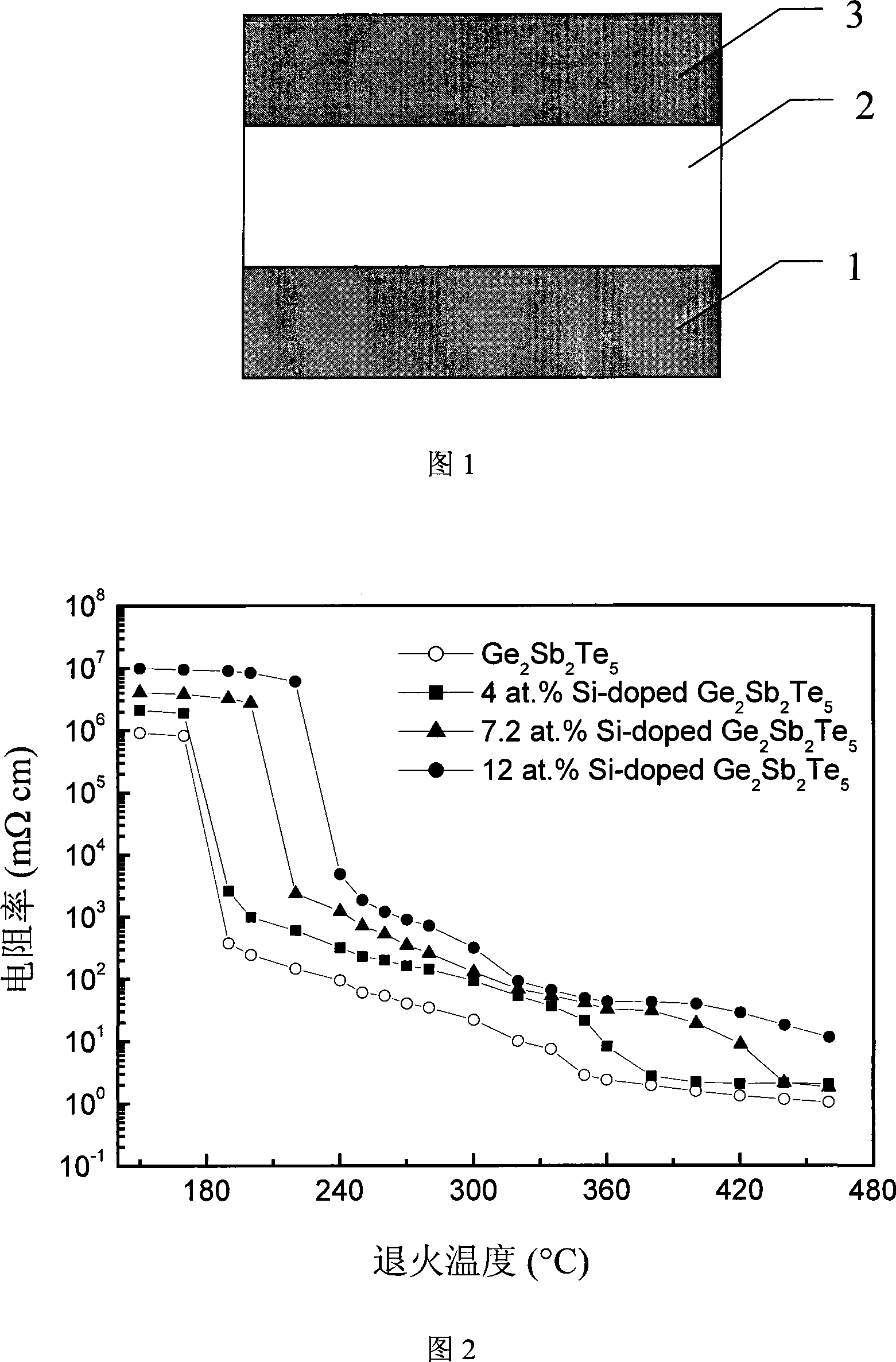

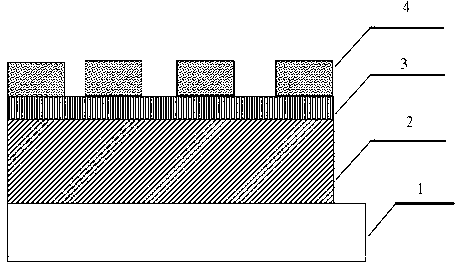

InactiveCN102738388AImplement multi-value storageIncrease storage capacitySolid-state devicesDigital storageMedia layerSemiconductor

The invention relates to a semiconductor device possessing a memristor characteristic and a method for realizing multilevel storage. The semiconductor device comprises an upper electrode, a lower electrode and a storage medium layer arranged between the upper electrode and the lower electrode. According to the invention, when the semiconductor device possessing the memristor characteristic generates mutual conversion between a high impedance state and a low impedance state, different high impedance state or low impedance state resistance values can be obtained through controlling a conversion voltage so that multilevel storage of multi-bit data is stored in each memory cell; a storage capacity of the semiconductor device possessing the memristor characteristic is increased and making cost of the semiconductor device possessing the memristor characteristic is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

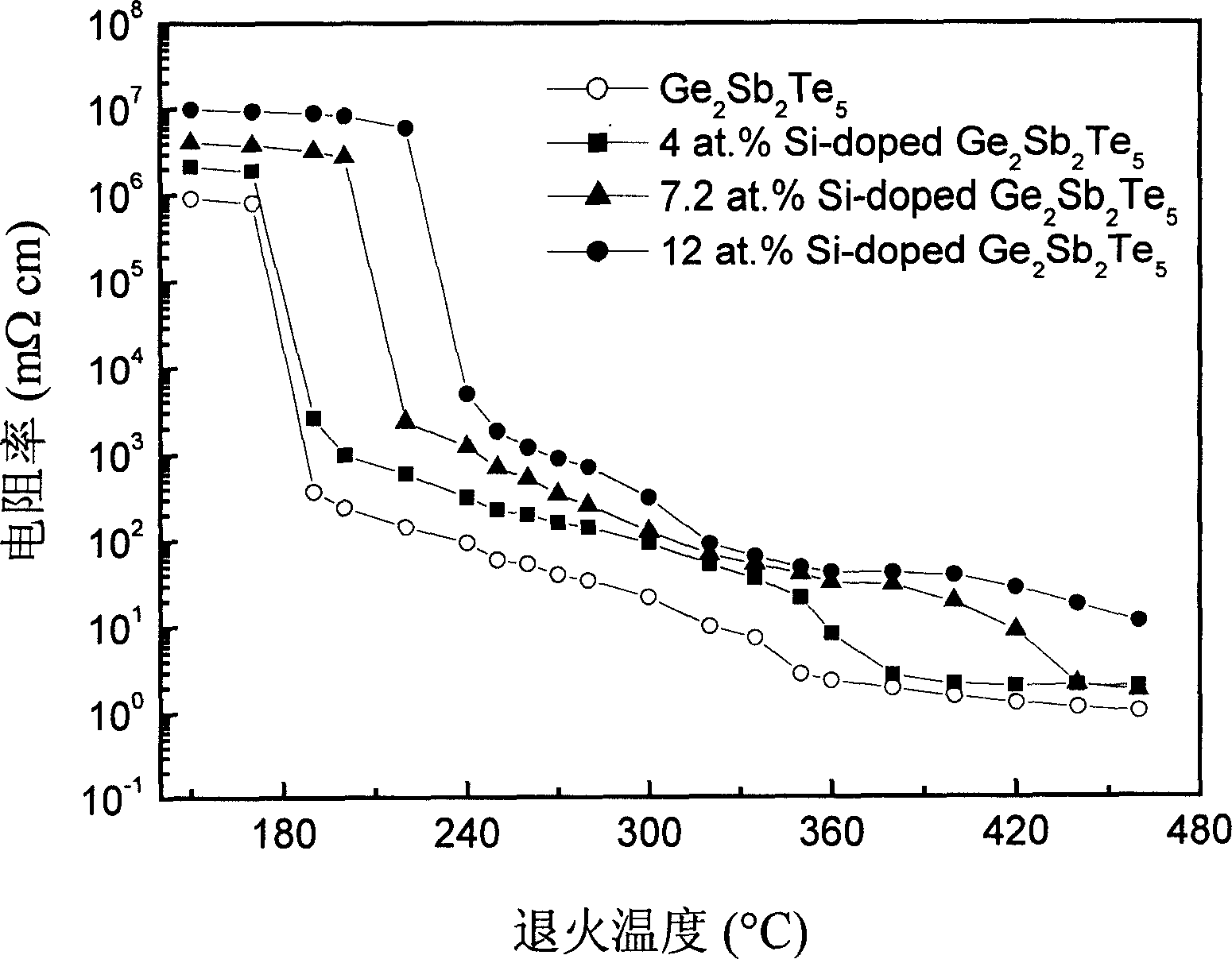

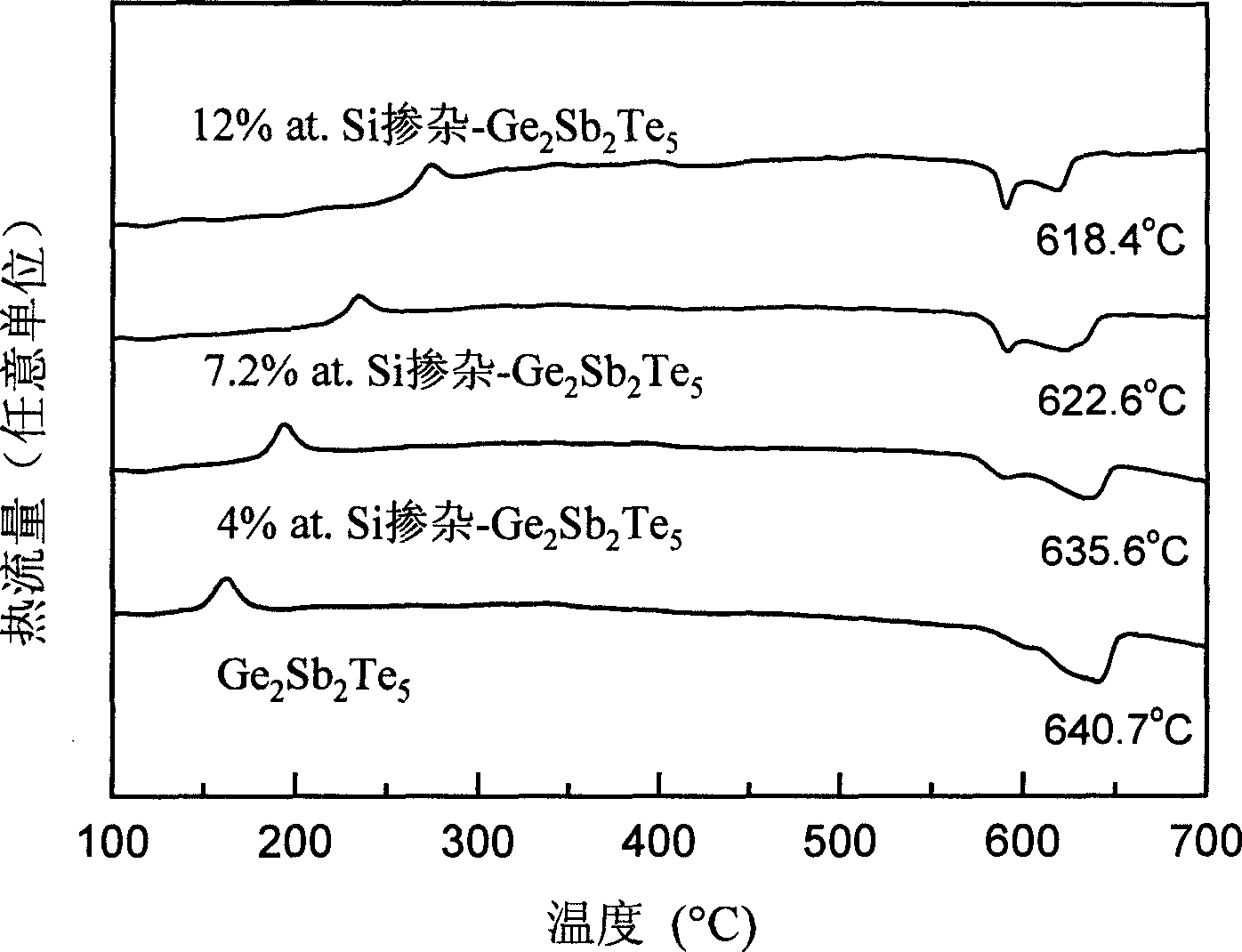

Silicon-contained series surfur-family compound phase transformation film material for phase transformation memory

InactiveCN1744340AEasy transferLower write operation currentElectrical apparatusHigh resistanceHigh rate

The disclosed materials include three types: (1) alloy firm of TeaSibSbl00-(a+b); (2) firm of (TeaGebSb l00-(a+b) )c Si1oo-c formed from Ge-Sb-Te alloy with Si being doped into; (3) alloy firm of TeaSicGe(b-c)Sb l00-(a+b) obtained by using Si to partially replace Ge in Ge-Sb-Te alloy. Comparing common Ge2Sb2Te5 film of phase change, the invention possesses higher resistance of crystalline state, higher rate of change of amorphous state / crystalline state, lower rate of change of film thickness of amorphous state / crystalline state, and lower melting point. These characters make storage devices of film of phase change containing chalcogenide in Si group possess higher rate of on / off and stability of device. The invention makes for lowering operation current for writing storage devices as well as for realizing storage in multiple values in higher density.

Owner:SHANGHAI JIAO TONG UNIV +1

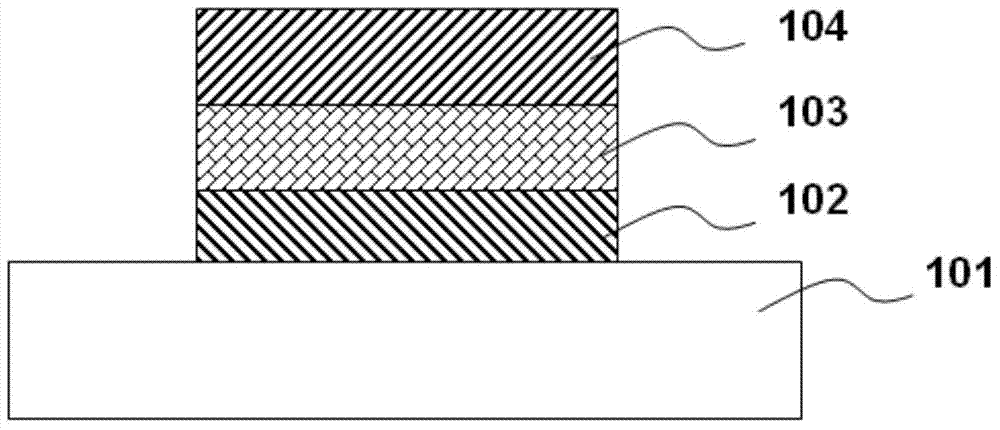

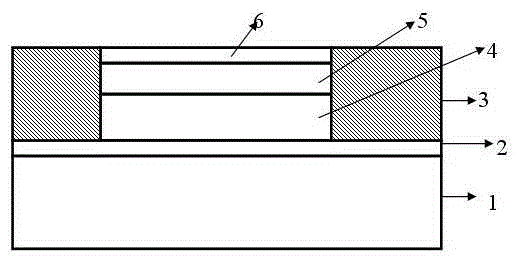

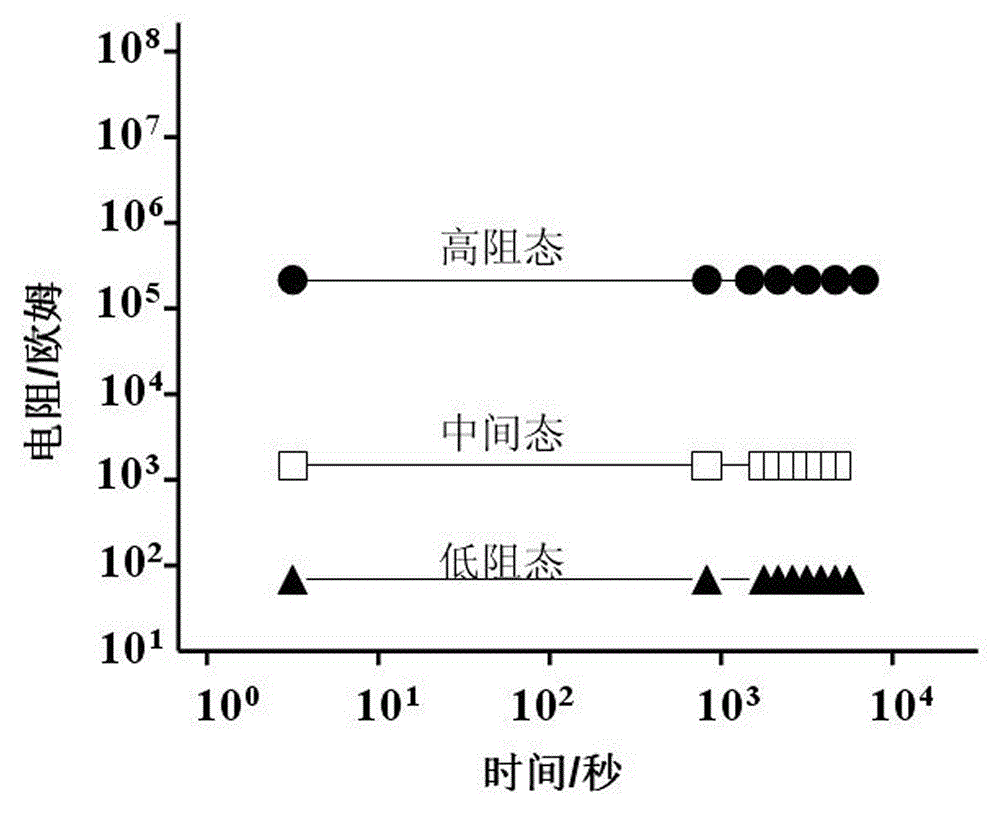

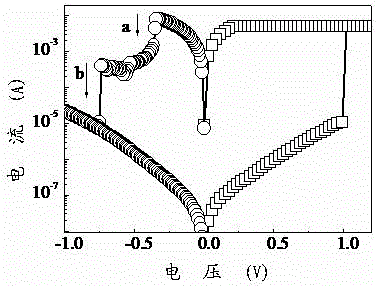

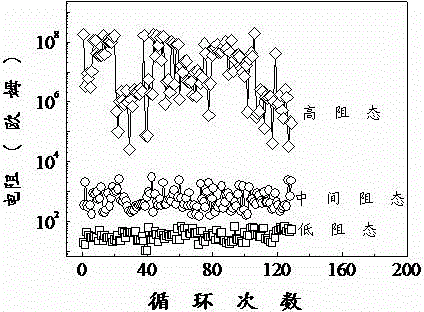

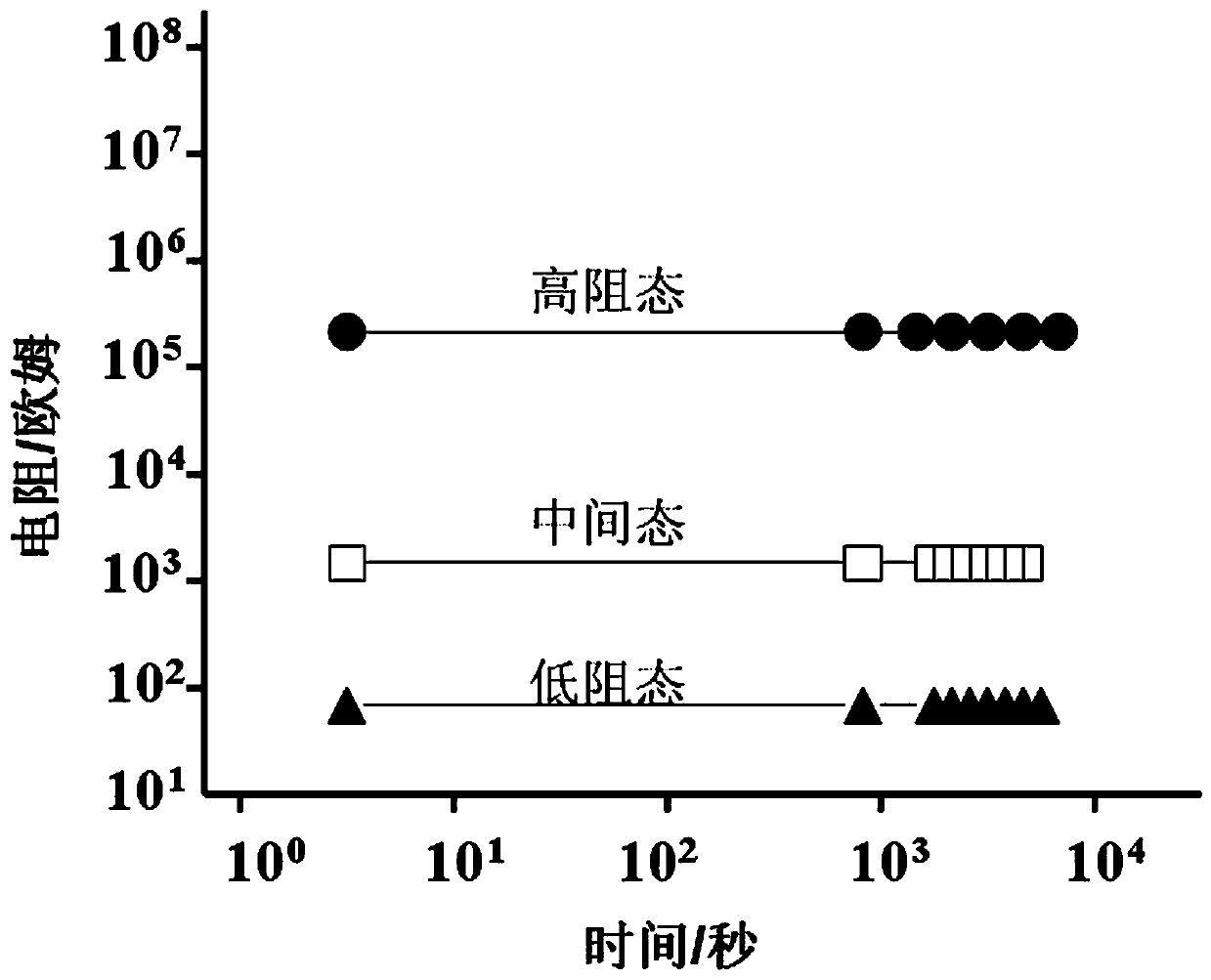

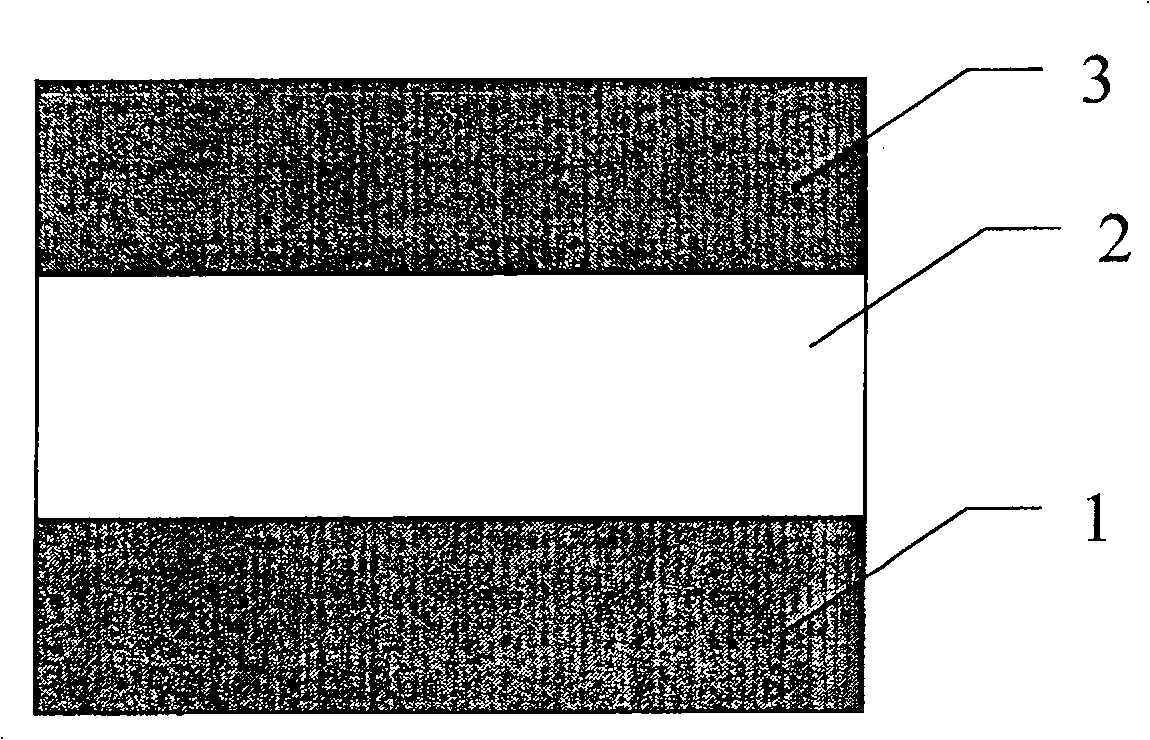

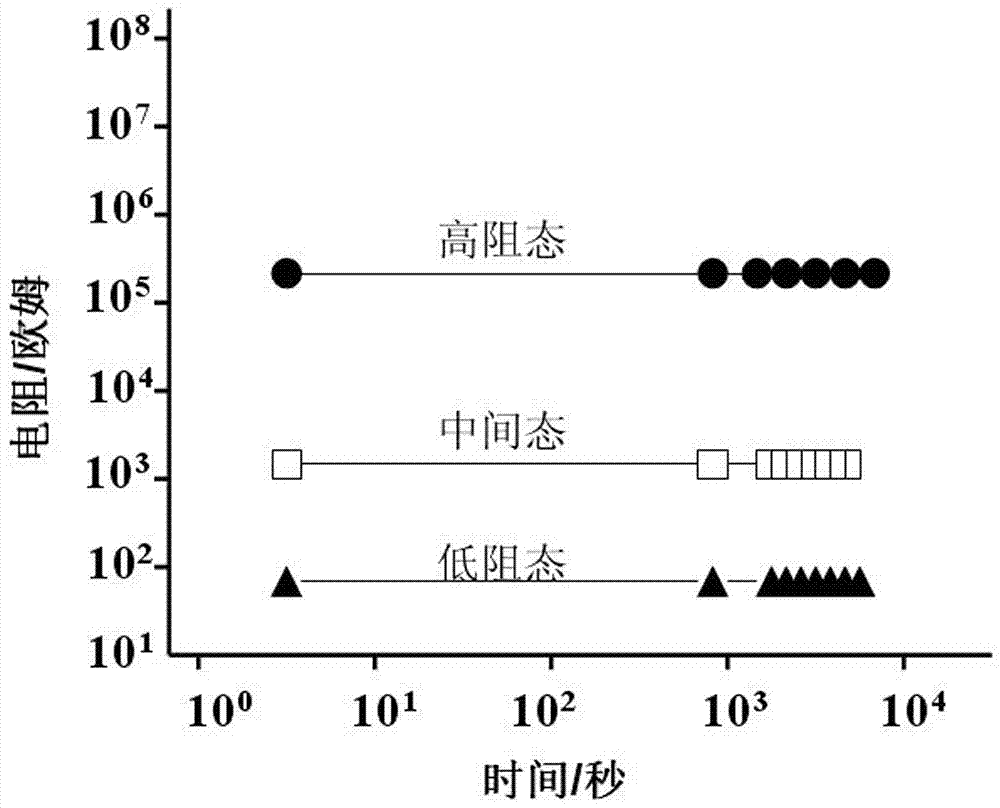

Resistance random access memory based on vanadium oxide/aluminum oxide laminated structure and manufacturing method thereof

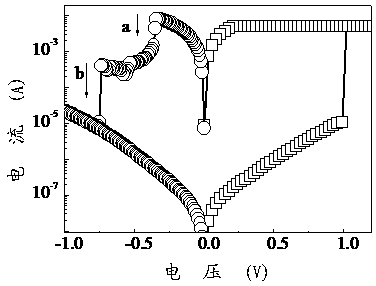

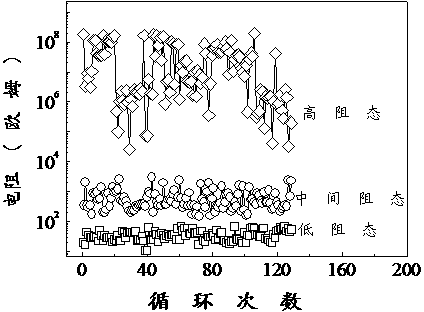

ActiveCN103311435AImplement multi-value storageImprove retentionElectrical apparatusDigital storagePhysicsThin membrane

The invention provides a resistance random access memory based on a vanadium oxide / aluminum oxide laminated structure. The resistance random access memory is composed of a lower electrode, a resistance random layer and an upper electrode to form of the laminated structure, wherein the resistance random layer is of a laminated structure of a vanadium oxide film and an aluminum oxide film. The thickness of each layer is that: the thickness of the lower electrode is 50-200nm, the thickness of the vanadium oxide film is 5-100nm, the thickness of the aluminum oxide film is 1-50nm, and the thickness of the upper electrode is 50-200nm. In a manufacturing method of the resistance random access memory, the vanadium oxide film is manufactured by a radio-frequency sputtering method, and the aluminum oxide film is manufactured by a magnetron sputtering or thermal oxidation method on the vanadium oxide film. The resistance random access memory has the advantage that the resistance random access memory adopts the vanadium oxide / aluminum oxide laminated structure and has twice reset phenomena, three impedance states including a low resistance state, a middle resistance state and a high resistance state can be obtained, resistance value ratio among the resistance states is more than 10 times, in addition, the resistance random access memory is further provided with good retentivity and repeatability.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

One time programmable memory and preparation method thereof

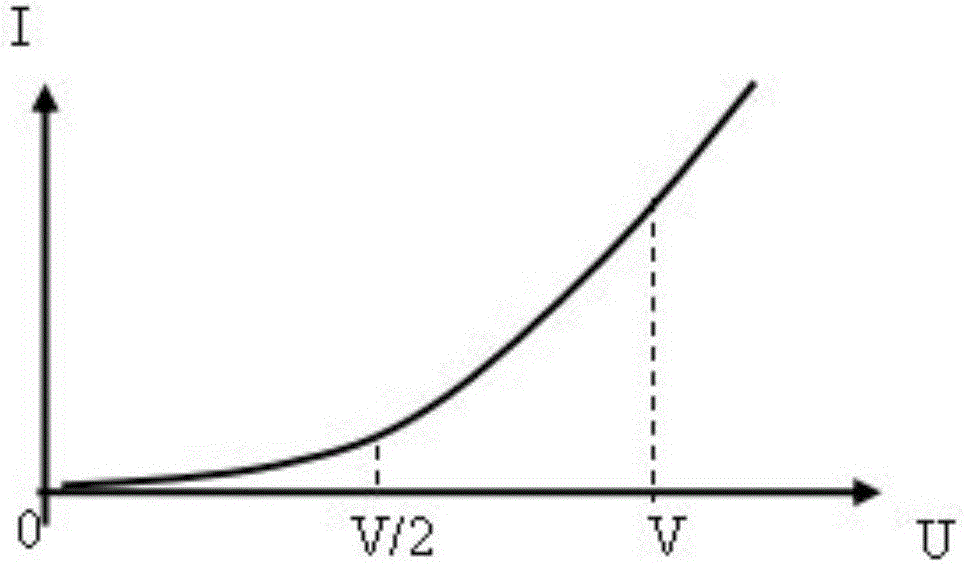

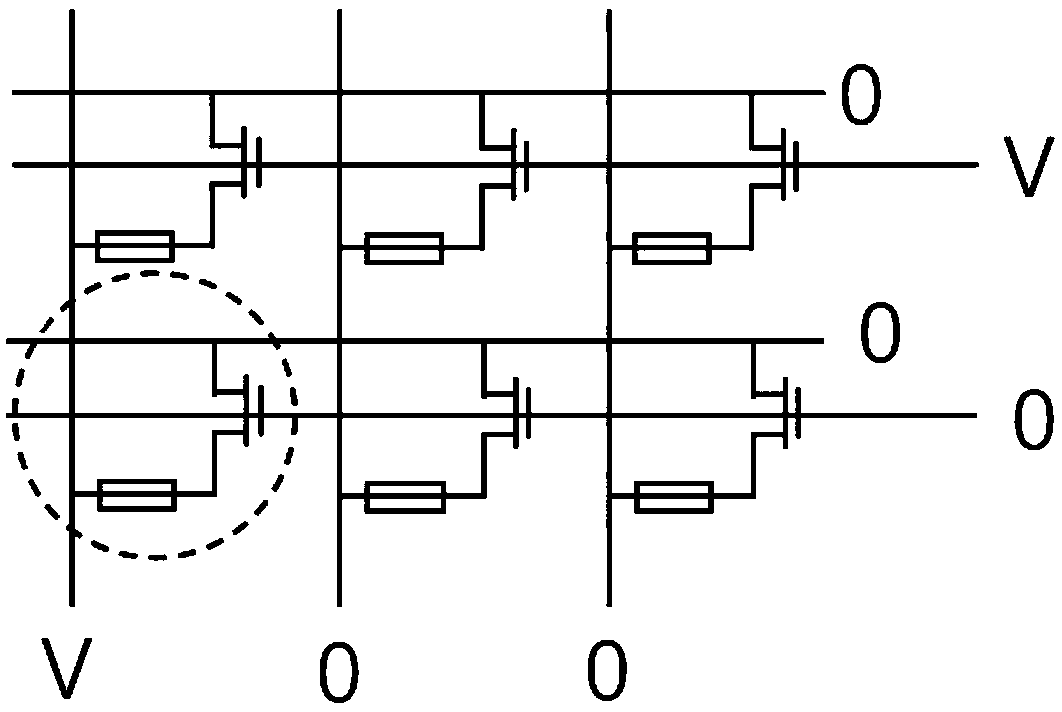

InactiveCN103106926ARead Crosstalk SuppressionEasy to integrateSolid-state devicesRead-only memoriesOne time programmableEngineering

The invention discloses a one time programmable memory and a preparation method thereof. The one time programmable memory provided by the invention comprises a lower electrode, a lower electrode and a resistive functional film formed between the upper electrode and the lower electrode. A Schottky barrier is formed between the upper electrode and the resistive functional film; and an ohmic contact is formed between the resistive functional film and the lower electrode. The invention utilizes rectification characteristic of the resistive functional film at a low resistance state to effectively inhibit the read crosstalk in a cross array structure, so as to facilitate integration of the memory and a peripheral circuit, and simplify preparation process of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

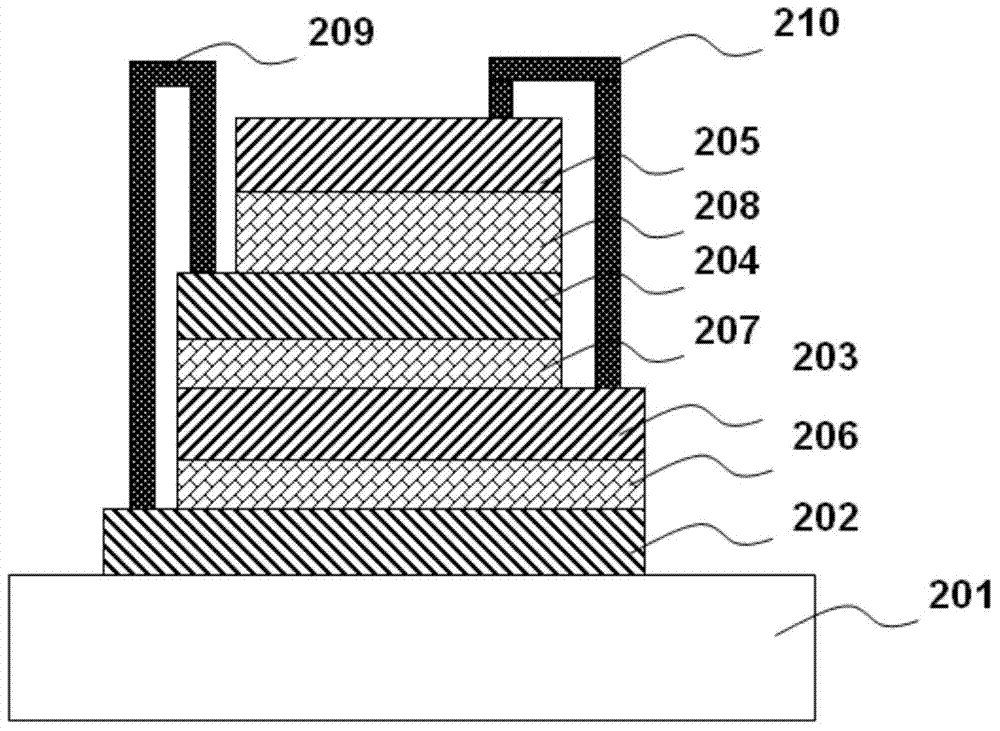

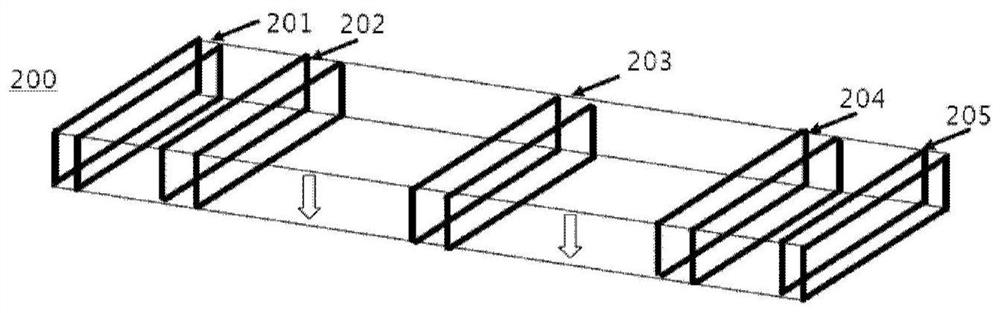

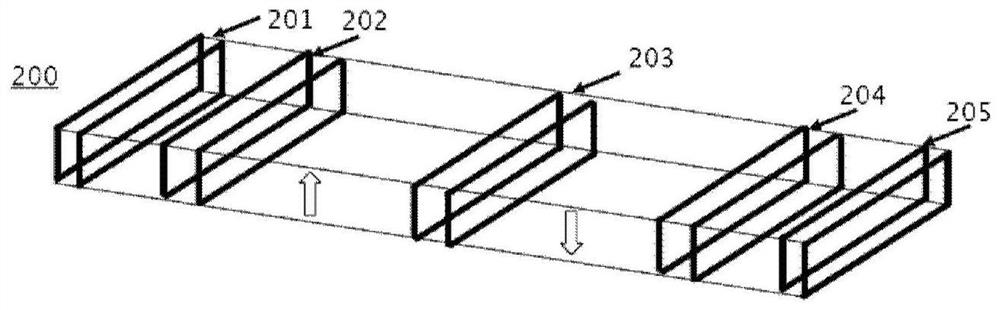

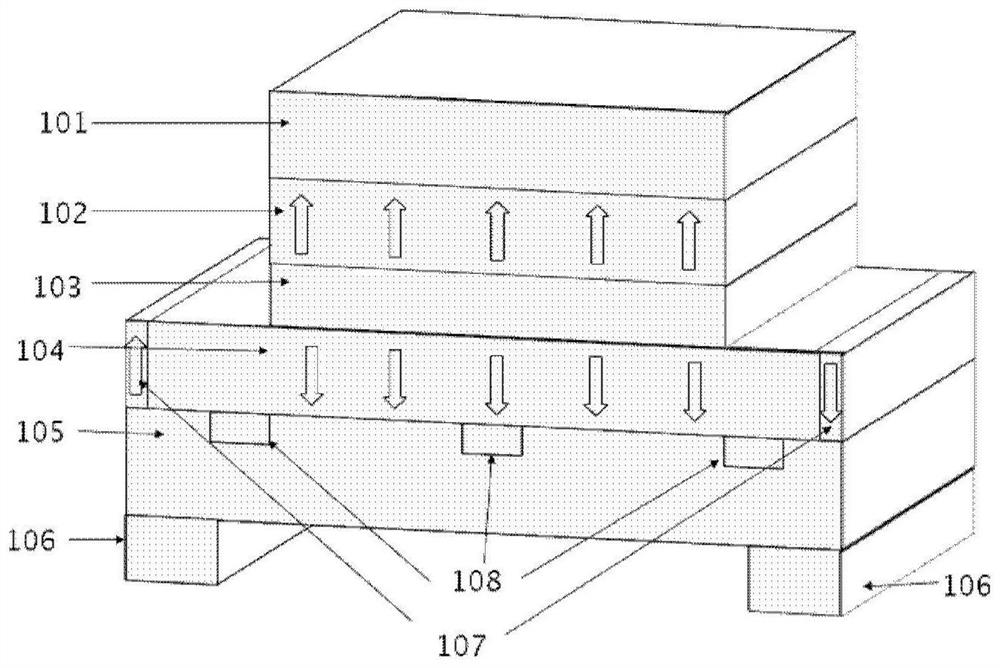

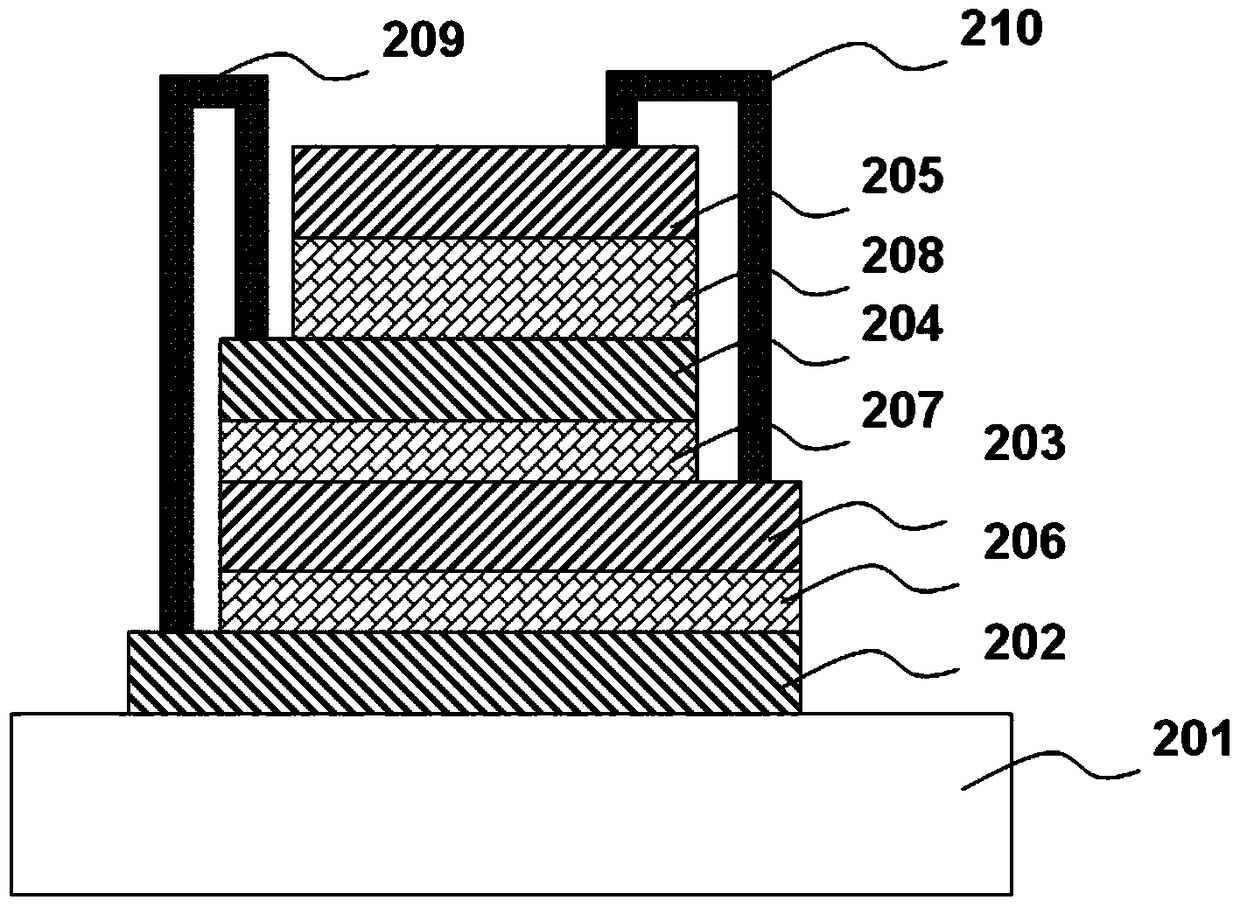

Resistive random access memory capable of realizing multilevel storage

ActiveCN103682096AImprove storage densityImplement multi-value storageElectrical apparatusStatic random-access memoryRandom access memory

The invention discloses a resistive random access memory capable of realizing multilevel storage. The resistive random access memory capable of realizing the multilevel storage comprises a semiconductor substrate, N-1 groups of double-layer structures and top electrodes on the N-1 groups of double-layer structures, wherein each N-1 group of double-layer structure consists of an electrode and one resistive layer positioned on the electrode; the N-1 groups of double-layer structures are positioned on the substrate and are successively overlaid from bottom to top, wherein N is a positive integer greater than or equal to 3; all odd-number electrodes from bottom to top are connected in parallel to serve as the lower electrode of the resistive random access memory; all even-number electrodes from bottom to top are connected in parallel to serve as the upper electrode of the resistive random access memory. Therefore, according to the resistive random access memory capable of realizing the multilevel storage, which is disclosed by the invention, in a mode that multiple electrodes and the resistive layers are alternatively overlaid, voltages required for each resistive layer to generate resistance change are different, resistance values after the resistance change happens are different, so that the multilevel storage of a memory unit structure is realized, and no additional area is occupied by the memory unit disclosed by the invention because of adopting a longitudinal-overlaying structure.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

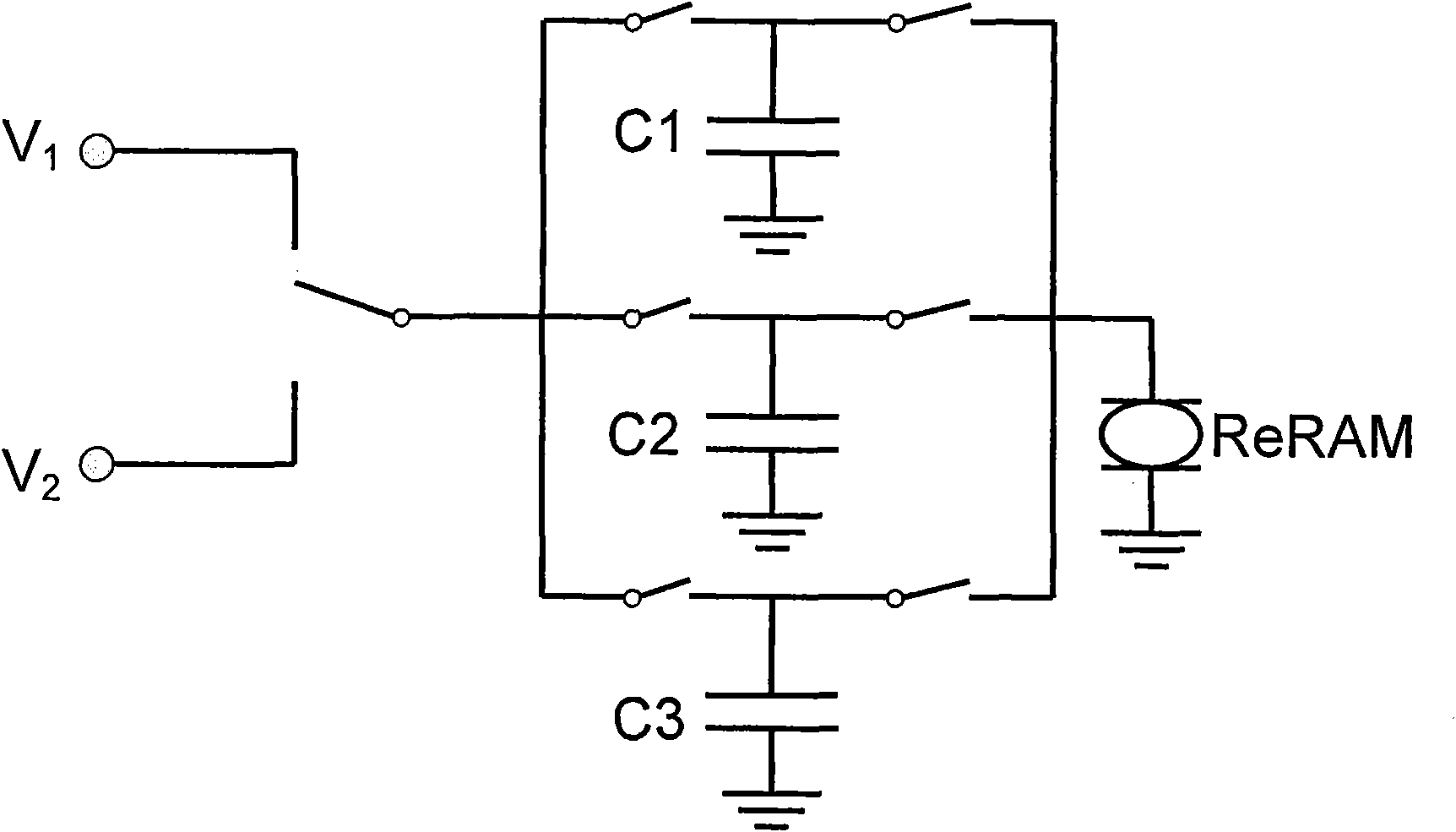

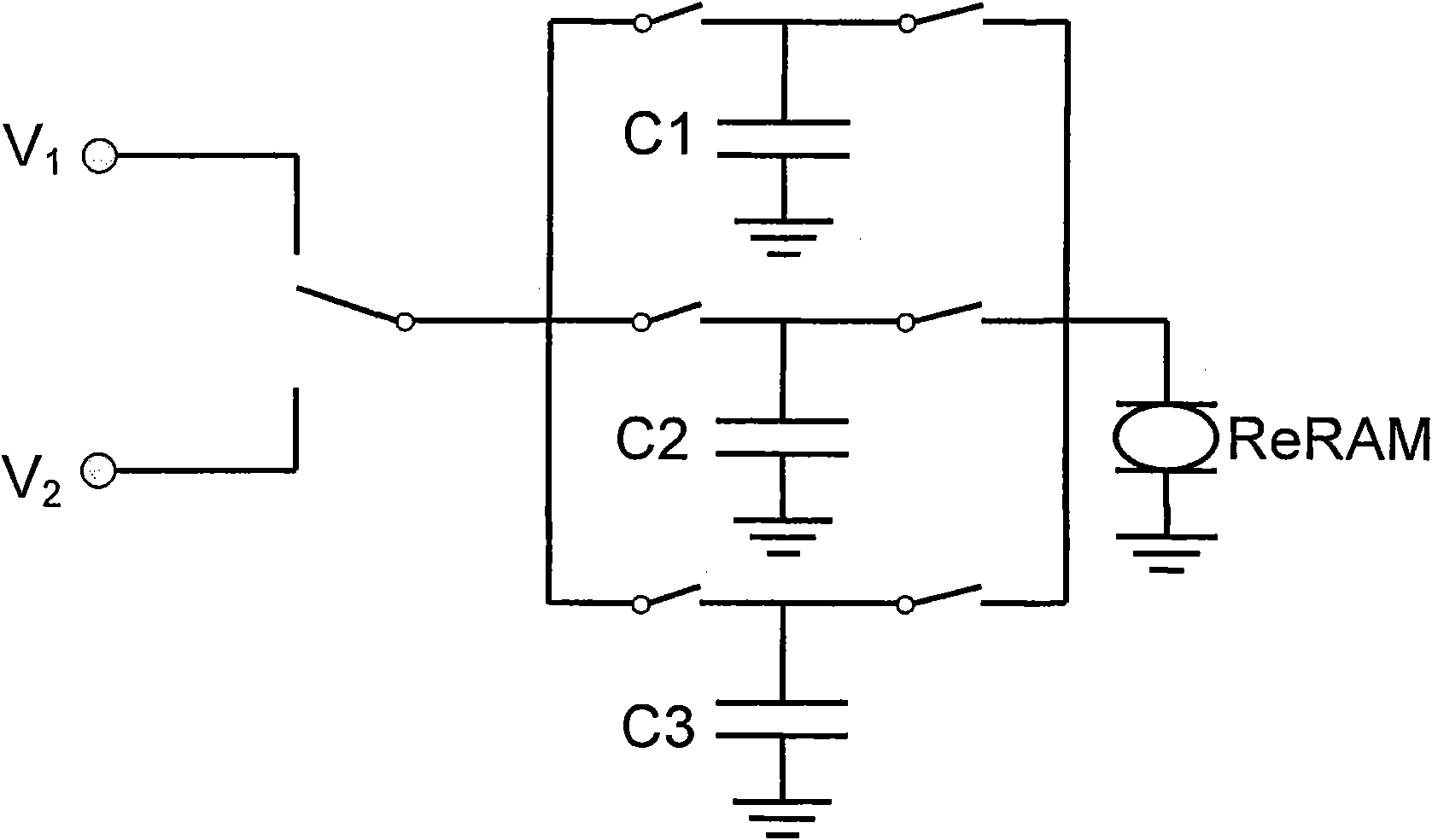

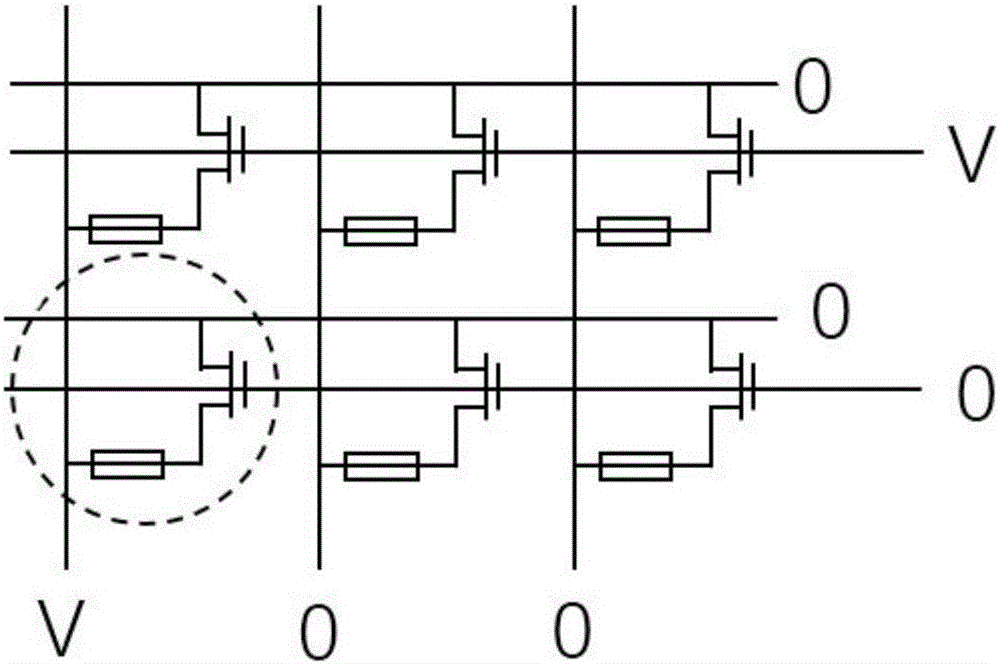

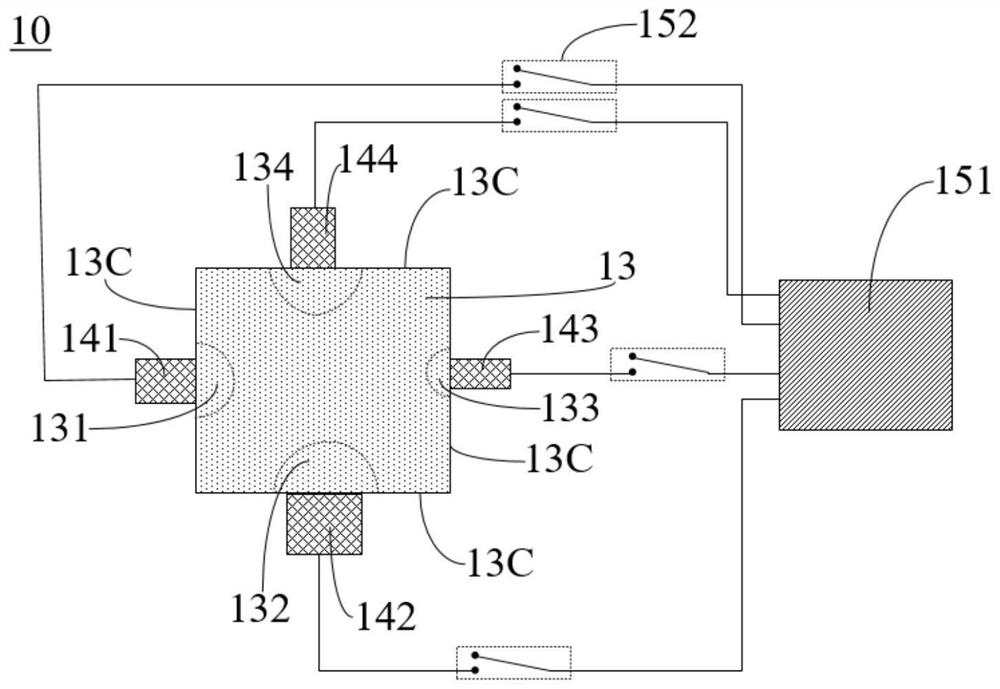

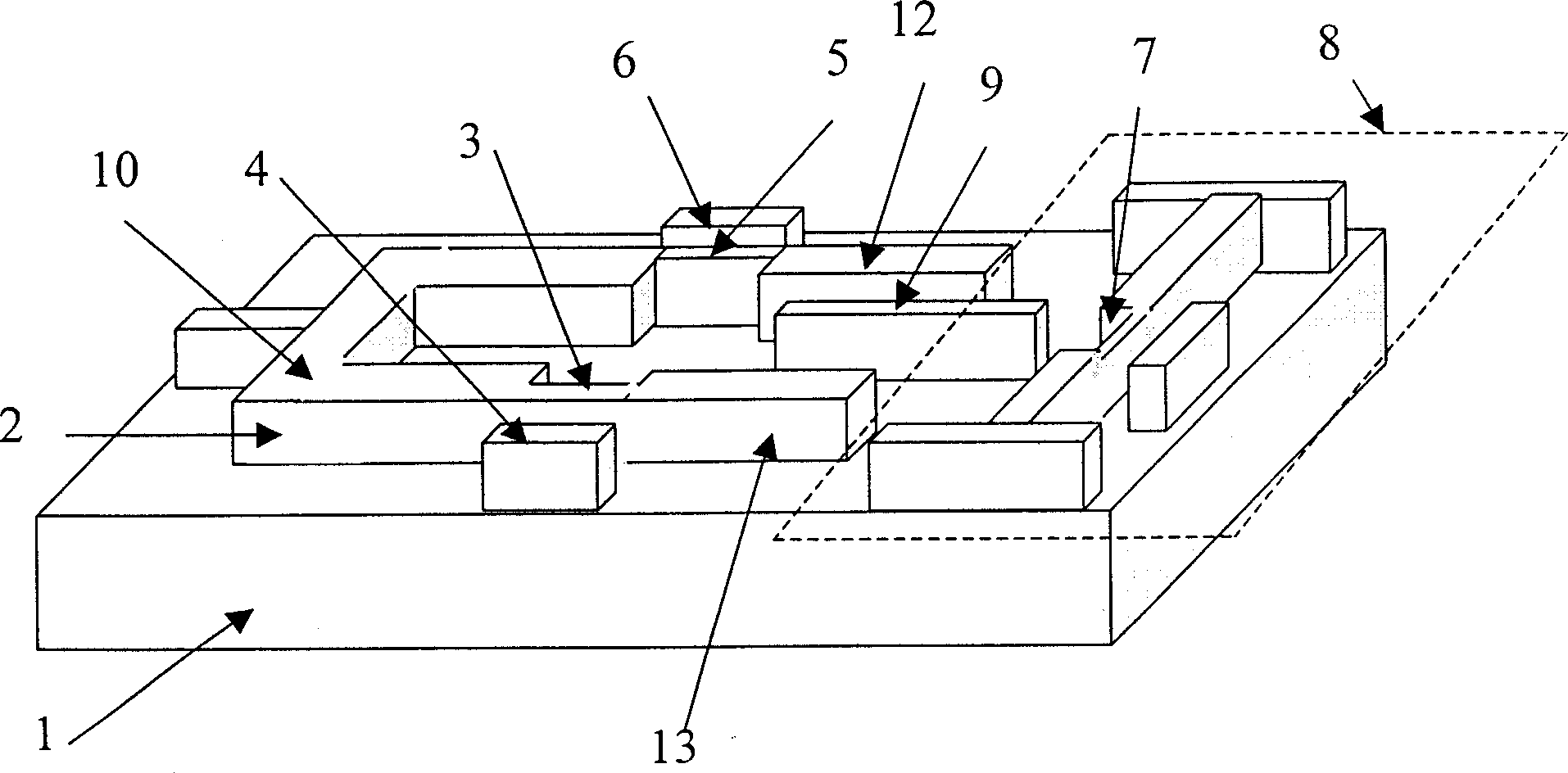

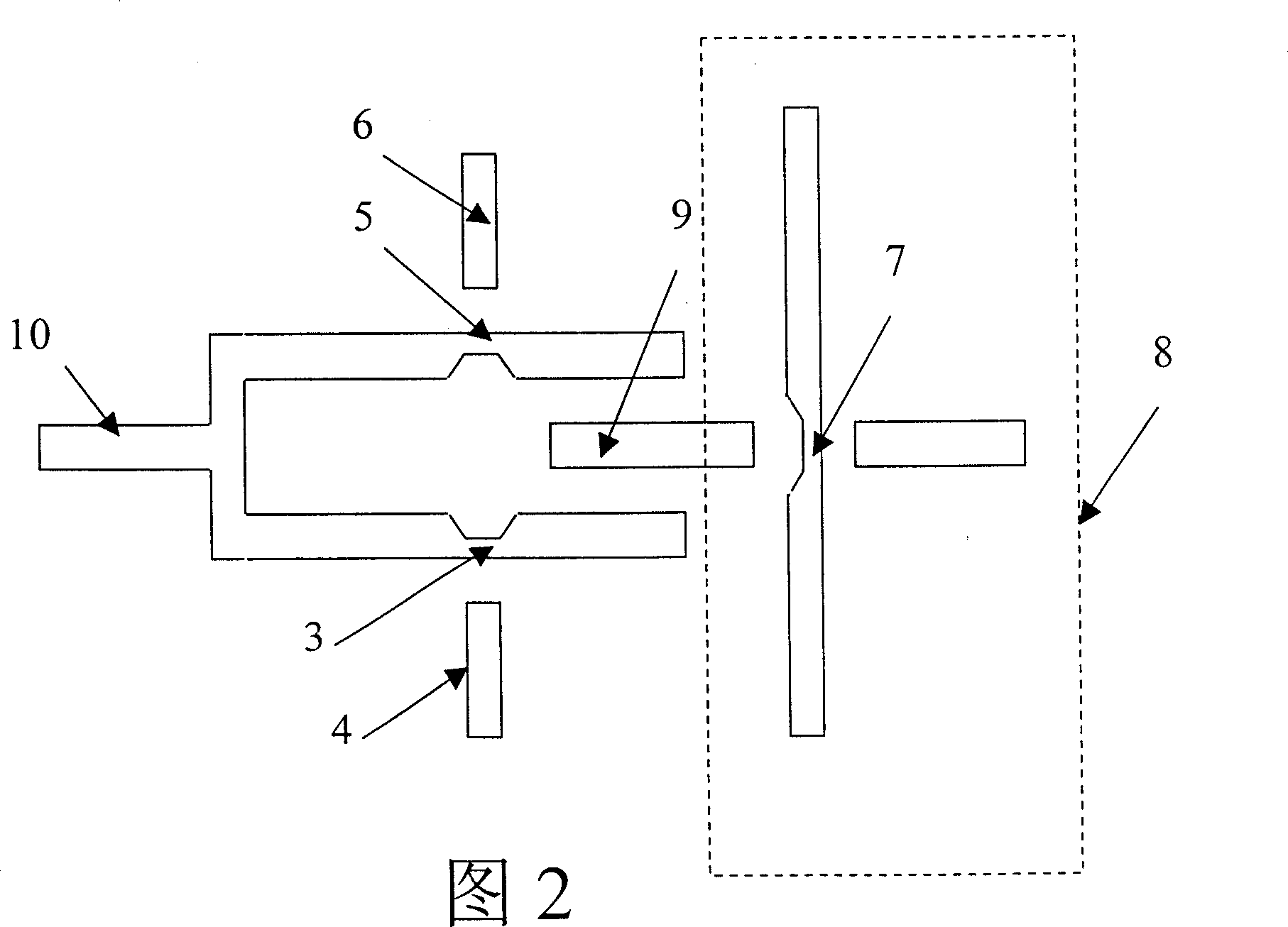

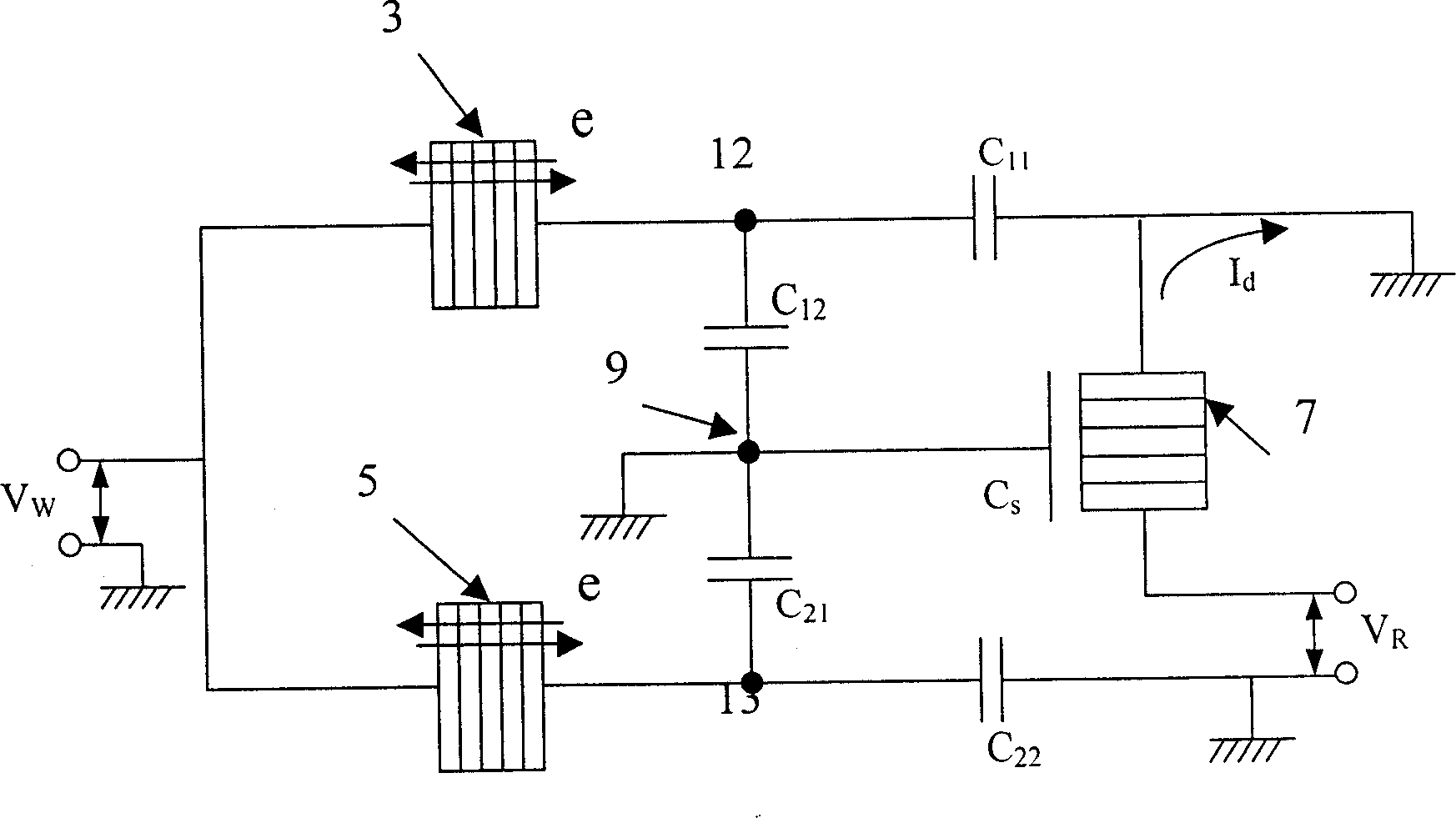

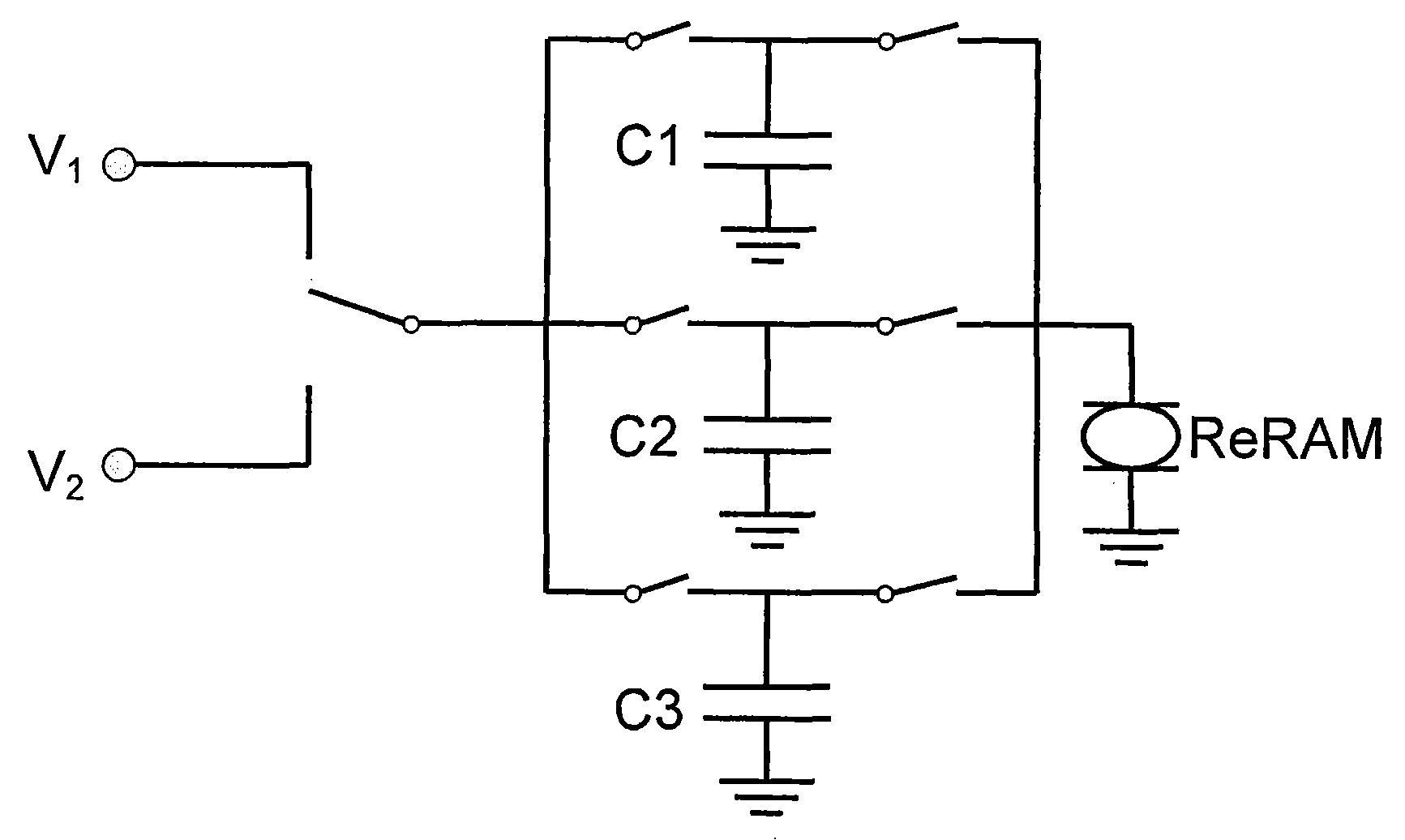

Circuit and method for driving resistive random access memory to realize multi-valued storage

ActiveCN101783170AImplement multi-value storageHigh densityDigital storageCapacitanceStatic random-access memory

The invention discloses a circuit and a method for driving a resistive random access memory to realize multi-valued storage by using a capacitor. The circuit consists of a plurality of capacitors which are used for storing electric energy and have different capacitances, a plurality of voltage sources, the resistive random access memory, and a switching circuit, wherein the capacitors are connected to the voltage sources and the resistive random access memory through the switching circuit. The method comprises the following steps of: charging the capacitors having different capacitances to make the capacitors have the same voltage, or charging the capacitors having the same capacitance to make the capacitors have different voltages so as to make the capacitors store different electric energy; and then driving the resistive random access memory by using the capacitors having different electrical energy as signal excitation sources, and changing the resistance state of the resistive random access memory so as to make the resistive random access memory have different resistance states and realize the multi-valued storage. By using the circuit and the method, the multi-valued storage is realized by using a simple circuit to drive the resistive random access memory, and storage with a higher density in the same area is realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

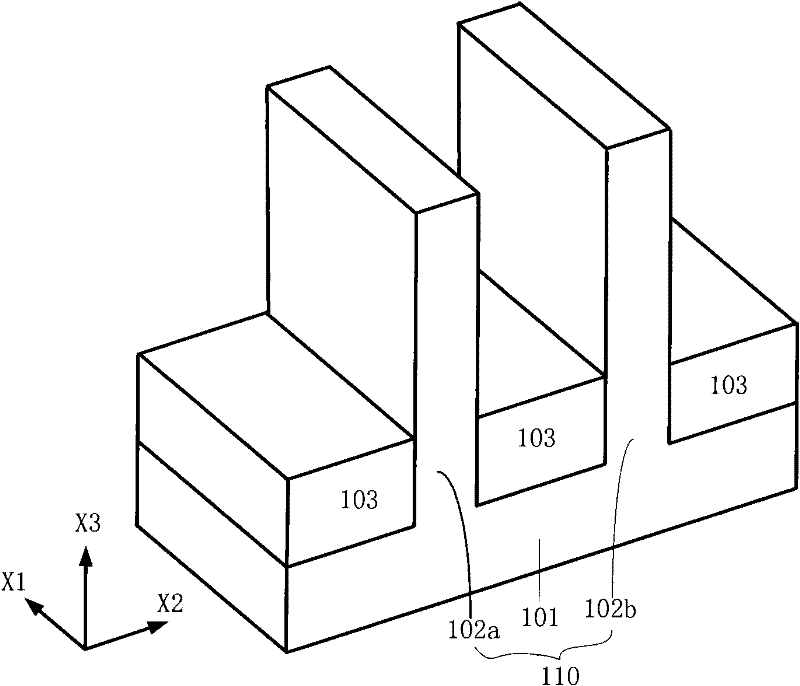

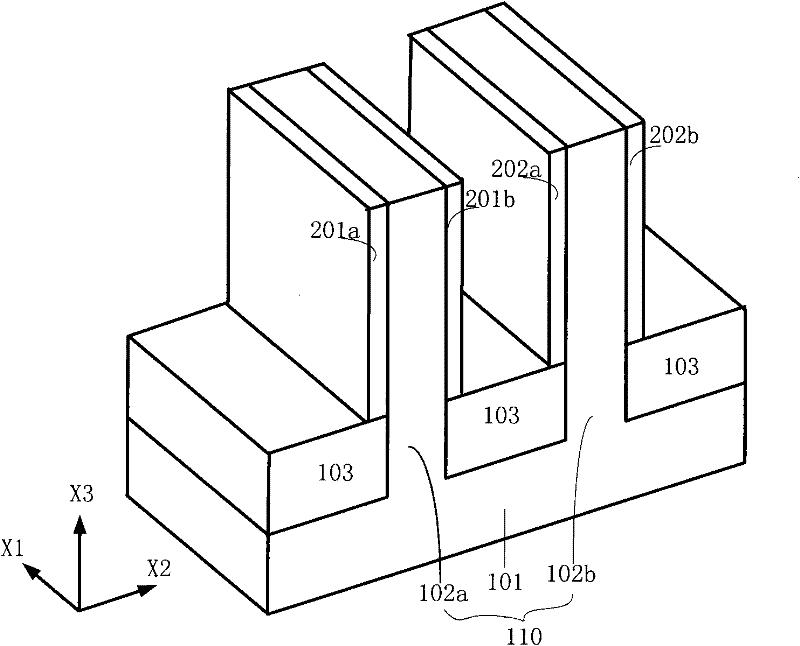

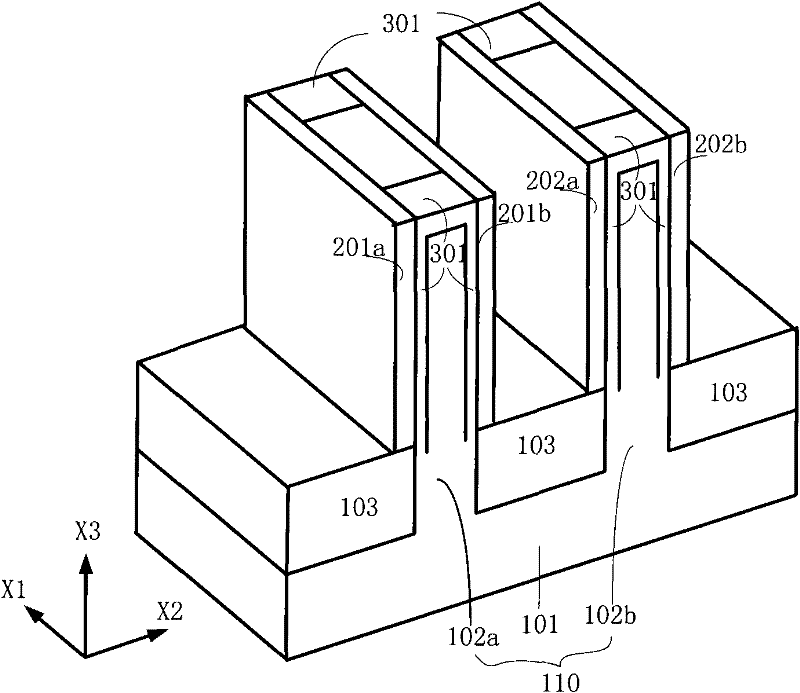

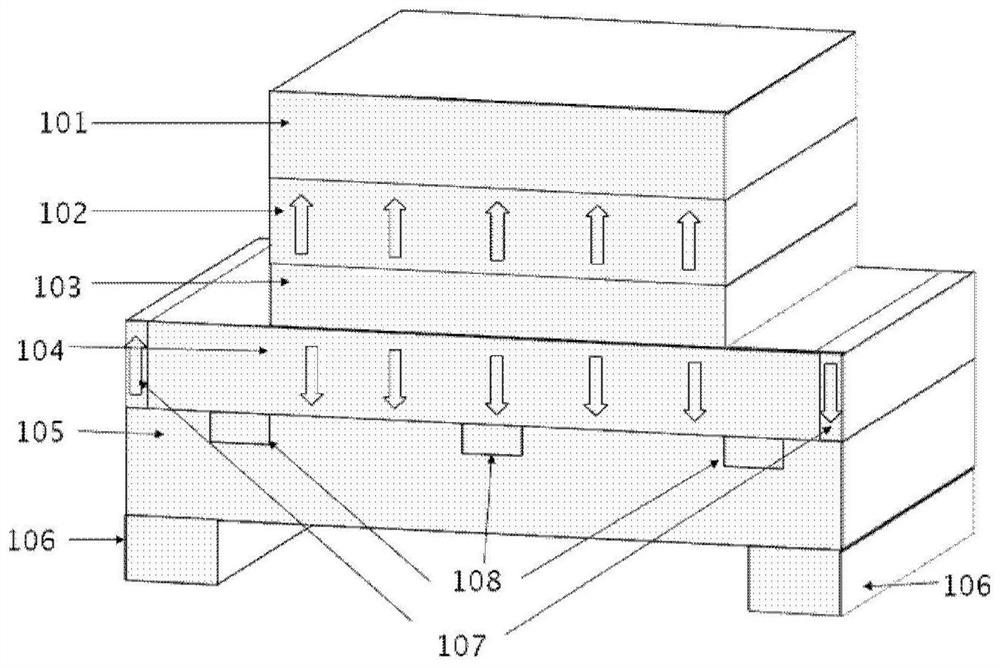

Three-dimensional multivalue nonvolatile memory structure

InactiveCN102347332AExcellent programmingExcellent erasureSolid-state devicesSemiconductor/solid-state device manufacturingConventional memoryThree dimensional integration

The invention discloses a three-dimensional multivalue nonvolatile memory structure, which comprises Fin structures, a tunneling dielectric layer, a charge capture layer and a charge barrier layer, and periodic source and drain regions, wherein the Fin structures are connected with a semiconductor substrate; the tunneling dielectric layer, the charge capture layer and the charge barrier layer are formed on the side walls of the Fin structures sequentially; the periodic source and drain regions are formed on the Fin structures; control grid electrodes are exported from a position between adjacent Fin structures; and the grid electrodes in a vertical direction are isolated by the dielectric layer, and sources and drains are exported from the tops of the Fin structures, so three-dimensional integration can be formed. The three-dimensional multivalue nonvolatile memory structure is high in density and easy to integrate and can be implemented by adopting the conventional memory manufacturing process; and popularization and application of the three-dimensional multivalue nonvolatile memory structure is facilitated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

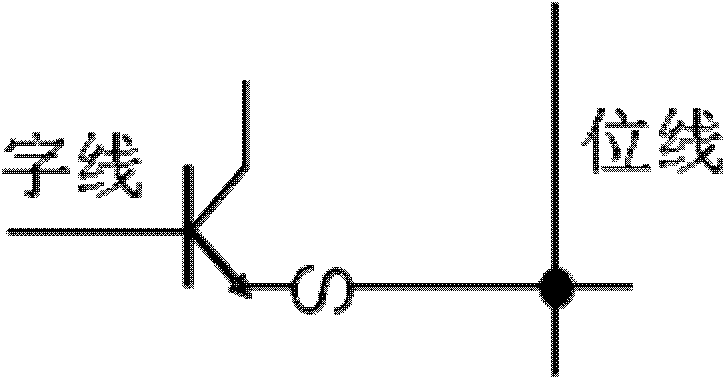

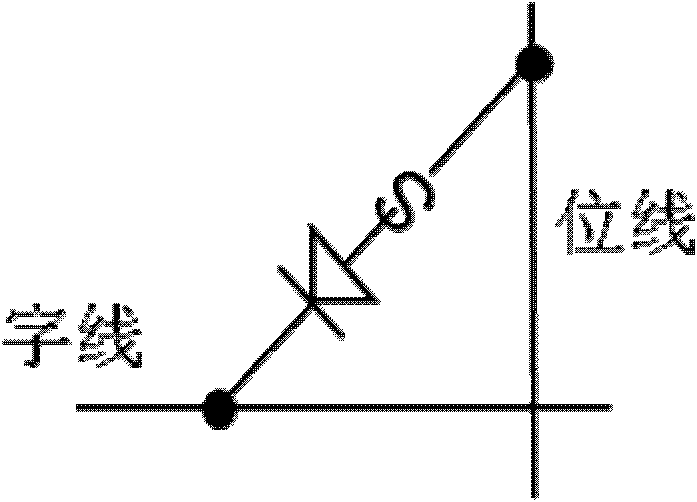

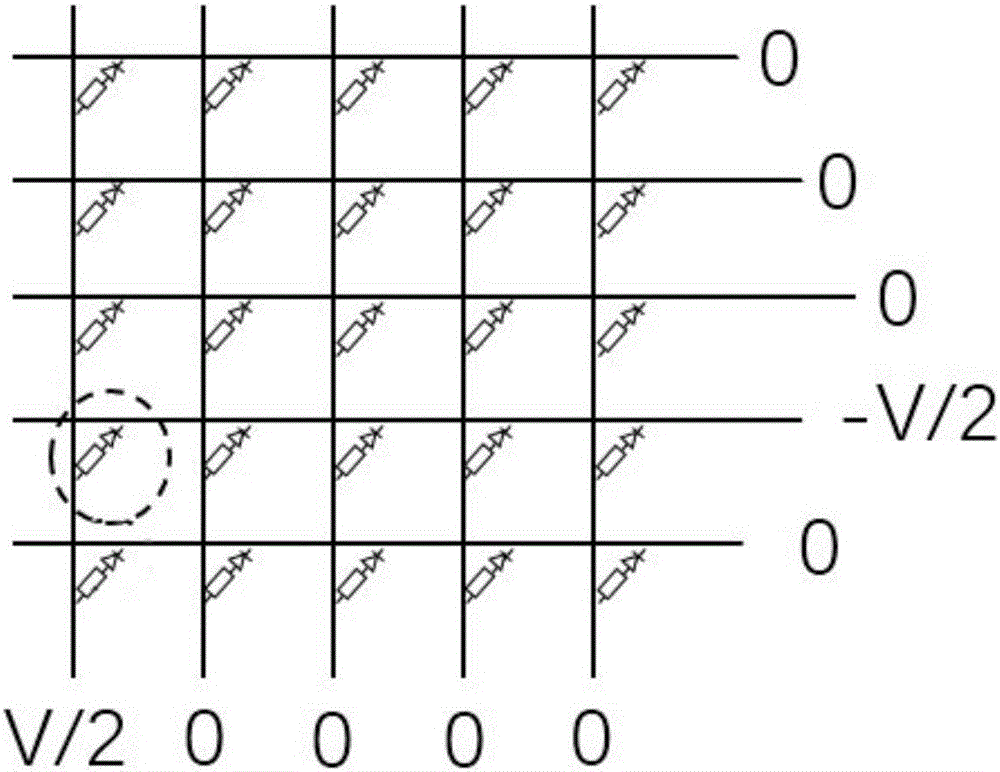

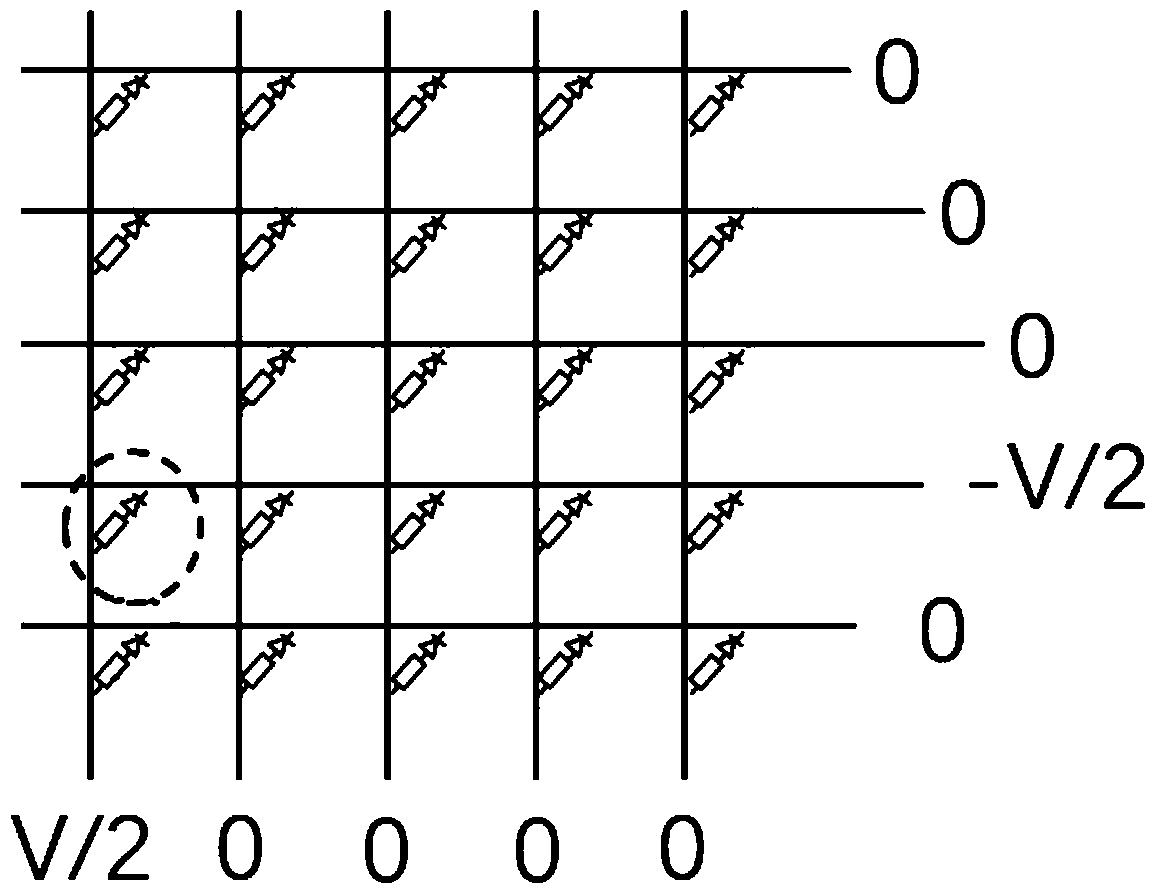

Memory array reading method based on unidirectionally-connected memory cells

The invention provides a memory array reading method based on unidirectionally-connected memory cells. A memory array comprises multiple word lines, multiple bit lines intersecting with the word lines, multiple unidirectionally-connected memory cells which are arranged at the intersection points of the word lines and the bit lines and connected with the word lines and the bit lines and peripheral reading circuits for reading and writing the corresponding memory cells connected to the same bit lines. The method comprises the steps that first voltage is applied to the word line to which the selected memory cell belongs, and second voltage is applied to the other word lines of the memory array; meanwhile, the second voltage is applied to the bit line to which the selected memory cell belongs, and the first voltage is applied to the other bit lines; the bit line where the memory cell is located is read and written through the corresponding peripheral circuit.

Owner:PEKING UNIV

Resistive memory unit preparing method

InactiveCN105185903AImplement multi-value storageImprove storage densitySolid-state devicesSemiconductor devicesNitrogen oxidesSpins

The invention provides a resistive memory unit preparing method, and relates to the technical field of non-volatile memory devices. The preparing method comprises the steps that a lower electrode layer is formed on a substrate through a conductive material; an insulating dielectric layer is deposited or spin-coated on the lower electrode layer; a trench is formed on the insulating dielectric layer through a photolithography process, and the bottom of the trench extends to the lower electrode layer; a function layer of a resistive memory unit is formed within the trench; the function layer is in an upper and lower layer laminated structure, and is formed by laminating an amorphous SnOx layer and a nitrogen oxide MnOxNy layer; the range of x in the amorphous SnOx is between 0 and 2; the range of x and the range of y in the nitrogen oxide MnOxNy are respectively between 1 and 2 and between 0.001 and 2; an upper electrode layer is formed on the function layer through a conductive material; and through a flattening process, the upper electrode layer is flush with the surface of the insulating dielectric layer. According to the resistive memory unit provided by the invention, stable multi-value memory is realized, and the memory density and stability of the memory unit can be improved.

Owner:HENAN UNIV OF SCI & TECH

Tri-state spinning electronic device, storage unit, storage array and read-write circuit

ActiveCN112802515AImprove compatibilityImprove reliabilityDigital storagePhysical realisationHemt circuitsEngineering

The invention provides a tri-state spinning electronic device, a storage unit, a storage array and a read-write circuit, and the tri-state spinning electronic device comprises a bottom electrode, a magnetic tunnel junction and a top electrode from bottom to top. The magnetic tunnel junction comprises a spin-orbit coupling layer, a ferromagnetic free layer, a barrier tunneling layer, a ferromagnetic reference layer, three local magnetic domain wall pinning centers and a magnetic domain wall nucleation center. For modulating an antisymmetric exchange effect, the magnetic domain wall pinning center is embedded into a heavy metal and ferromagnetic free layer interface; the magnetic domain wall nucleation centers are arranged at the two ends of the ferromagnetic free layer; current pulse flows through the spin-orbit coupling layer to generate spin current to be injected into the ferromagnetic free layer, a spin-orbit torque effective field drives a domain wall to move and displace under the regulation and control of a full electric field, the displacement can be modulated through the pulse number, pulse width and direction of the current, and the CMOS process compatibility and high reliability are achieved. The invention also provides a tri-state read-write circuit and a tri-valued network computing application scheme thereof, and high-performance GXNOR operation of a three-valued spinning electronic device is realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

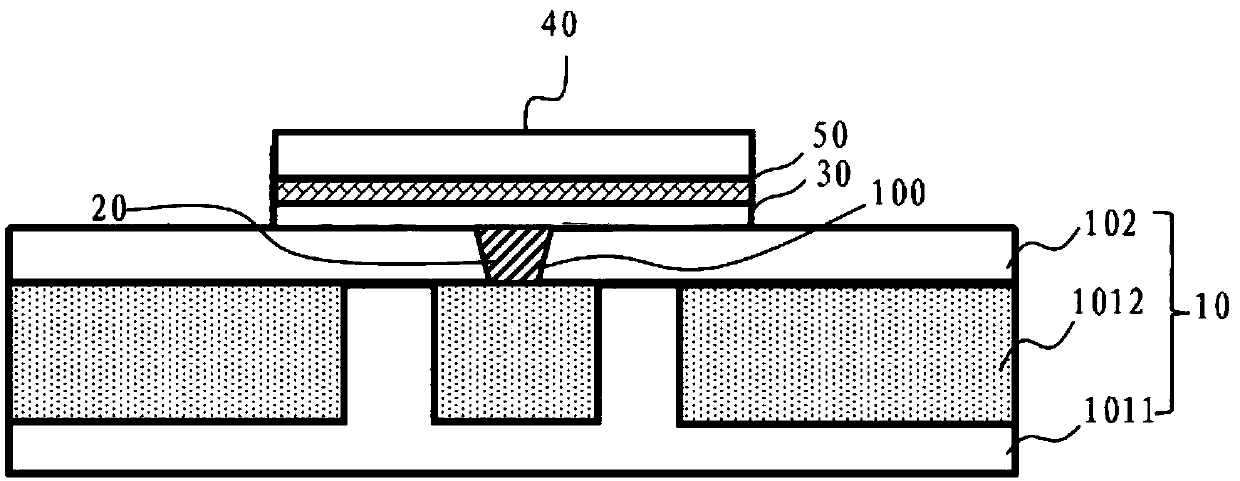

Resistive random access memory and preparation method thereof

PendingCN110739395ALarge storage capacityImplement multi-value storageElectrical apparatusMemory chipEngineering

The invention provides a preparation method of a resistive random access memory. The preparation method comprises the following steps: providing a substrate; forming a lower electrode on the substrate; forming a first resistive random material layer on the lower electrode and the upper surface of the substrate; forming a second resistive random material layer on the first resistive random materiallayer, wherein the resistive state of the second resistive random material layer is different from that of the first resistive random material layer; and forming an upper electrode on the second resistive random material layer. The second resistive random material layer is additionally arranged between the first resistive random material layer and the upper electrode so that the conversion undervarious resistance states (>2) of the resistive random access memory can be realized, and thus multi-value memory can be realized and the data storage amount can be increased on the premise that the memory chip area is unchanged.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

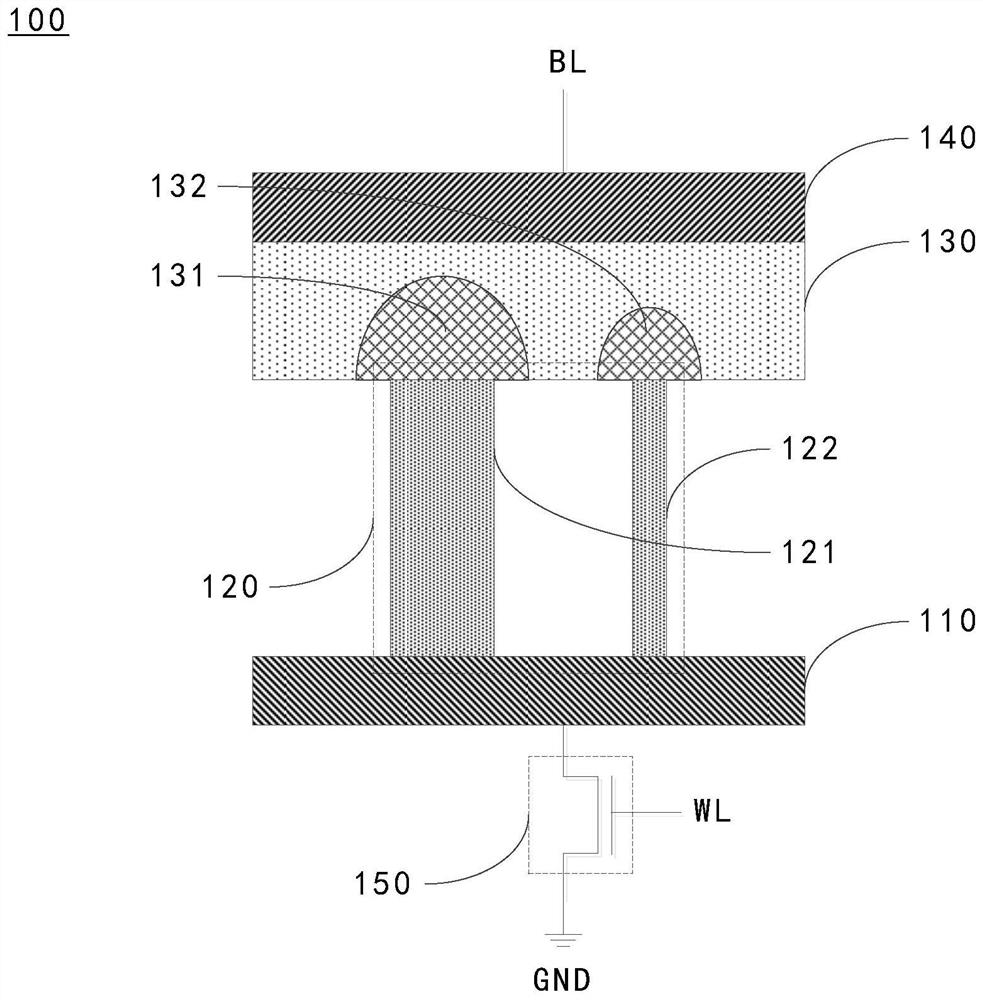

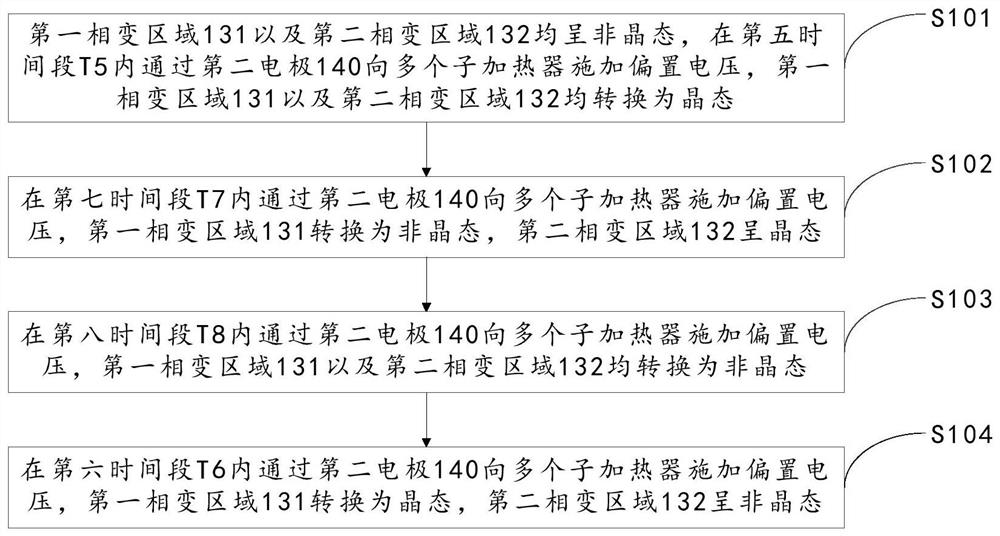

Phase change memory, memory control method and memory chip

PendingCN112086117AImprove storage densityImplement multi-value storageDigital storageMemory chipPhase-change memory

The invention relates to a phase change memory, a memory control method and a memory chip. The phase change memory comprises a first electrode, a second electrode, a phase change memory layer, a plurality of heaters and a control unit, wherein the phase change storage layer is positioned between the first electrode and the second electrode, and is electrically connected with the first electrode and the second electrode respectively; the control unit is electrically connected with the plurality of heaters and used for providing driving signals for the heaters. The plurality of heaters are respectively adjacent to different phase change regions of the phase change memory layer, and each heater is configured to be used for heating the adjacent phase change region under the driving of the driving signal, so that the multi-value storage of a single memory cell can be realized, and the storage density of the phase change memory is further improved.

Owner:YANGTZE MEMORY TECH CO LTD

Phase change film material of silicon-adulterated sulfur series for phase change memory

InactiveCN101101966AEasy transferLower write operation currentChalcogenide/metal/alloy compound compositionsElectrical apparatusPhase-change memoryGe element

The invention is concerned with a kind of phase change film material with chalcogenide in silicon series for phase change storage, belonging to micro-electronics technology field. Si element takes place of Ge element of TeaGebSb100-(a+b) alloy to form TeaGeb-cSicSb100-(a+b) alloy film, and a is from 48 to 60, b is from 8 to 40, the replace scalar c of Si is from 1 to 40 atom percent. This invention has higher crystal resistance than common Ge2Sb2Te5 phase change film, and more higher amorphous / crystalline state change ratio of resistance and more lower amorphous / crystalline state film thickness change ratio and lower melting point. This kind of storage has more higher open / close ratio and stability of piece to reduce writing current of storage and get storage multi-value with higher density.

Owner:SHANGHAI JIAO TONG UNIV +1

Resistive variable memory based on vanadium oxide/alumina stack structure and its preparation method

ActiveCN103311435BImplement multi-value storageImprove retentionElectrical apparatusDigital storageRandom access memoryThin membrane

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

Tri-state spintronic device, memory cell, memory array and read-write circuit

ActiveCN112802515BImprove compatibilityImprove reliabilityDigital storagePhysical realisationSoftware engineeringHemt circuits

The present disclosure provides a three-state spintronic device, a storage unit, an array and a read-write circuit. The three-state spintronic device includes from bottom to top: a bottom electrode, a magnetic tunnel junction and a top electrode; the magnetic tunnel junction includes : spin-orbit coupling layer, ferromagnetic free layer, barrier tunneling layer and ferromagnetic reference layer, three localized magnetic domain wall pinning centers and magnetic domain wall nucleation center; modulation of antisymmetric exchange, magnetic domain wall The pinning center is embedded at the interface between the heavy metal and the ferromagnetic free layer; the nucleation center of the magnetic domain wall is set at both ends of the ferromagnetic free layer; the current pulse flows through the spin-orbit coupling layer to generate spin current and inject into the ferromagnetic free layer. The effective field of the spin-orbit torque under the control of the electric field drives the displacement of the domain wall, and the displacement can be modulated by the number of pulses, the pulse width and the direction of the current, and has CMOS process compatibility and high reliability. The present disclosure also provides three-state read and write. The circuit and its ternary network computing application scheme realizes the high-performance GXNOR operation of ternary spintronic devices.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Single electron trivalue storage based on coulomb baffle principle design and its preparation method

InactiveCN1494150AAchieve ultra-high density storageExtended storage timeSolid-state devicesSemiconductor devicesCapacitanceConductive materials

The storage device possesses an insulative base plate with a conducting material layer on it. There are two structures of multiple tunneling junctions, one single electron transistor and one storage junction unit. One end of two tunneling junctions through lead wire connected to each other is as input end for writing in voltage, and the other end of each tunneling junction is connected to a storage junction. Middle capacitance in storage junction unit is coupled each other. Single electron transistor possesses source pole, drain pole, quantum point weak coupled to source / drain pole and grid pole for controlling static chemical potential energy of quantum point. Quantum point is connected to storage junction unit through mode of capacitance coupling. The part possesses three stable store statuses. Only controlling movement of minute electron can implement normal operation of the part so as to realize storing information in super high density under low power consumption.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

A memory array reading method based on single-phase conduction memory cells

ActiveCN105895152BAvoid misreadingWith one-way conduction characteristicsDigital storageComputer architectureStorage cell

The invention provides a memory array reading method based on unidirectionally-connected memory cells. A memory array comprises multiple word lines, multiple bit lines intersecting with the word lines, multiple unidirectionally-connected memory cells which are arranged at the intersection points of the word lines and the bit lines and connected with the word lines and the bit lines and peripheral reading circuits for reading and writing the corresponding memory cells connected to the same bit lines. The method comprises the steps that first voltage is applied to the word line to which the selected memory cell belongs, and second voltage is applied to the other word lines of the memory array; meanwhile, the second voltage is applied to the bit line to which the selected memory cell belongs, and the first voltage is applied to the other bit lines; the bit line where the memory cell is located is read and written through the corresponding peripheral circuit.

Owner:PEKING UNIV

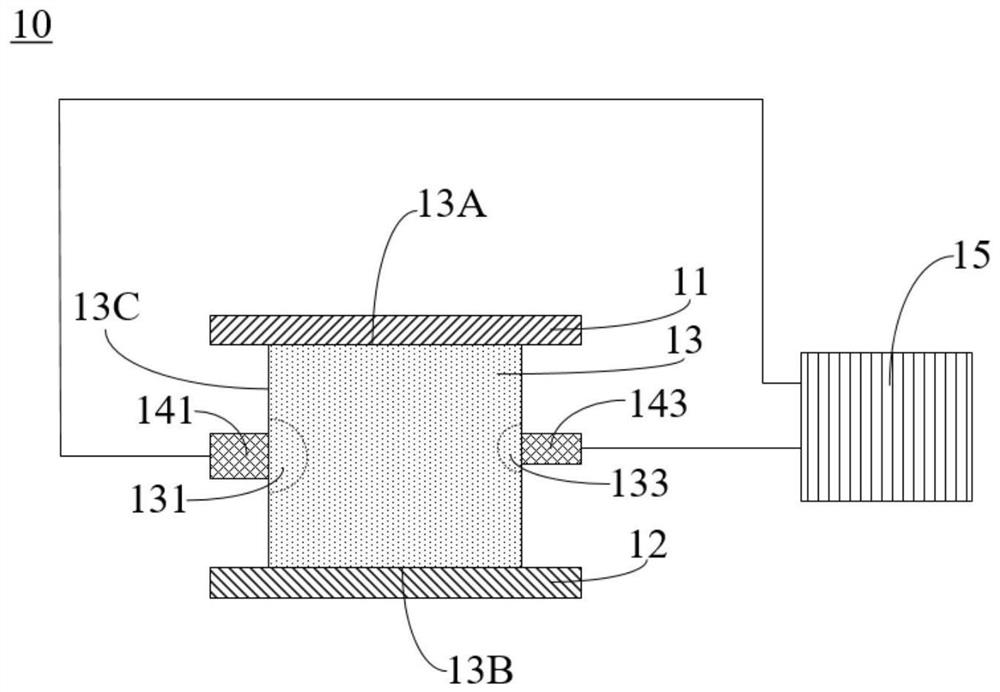

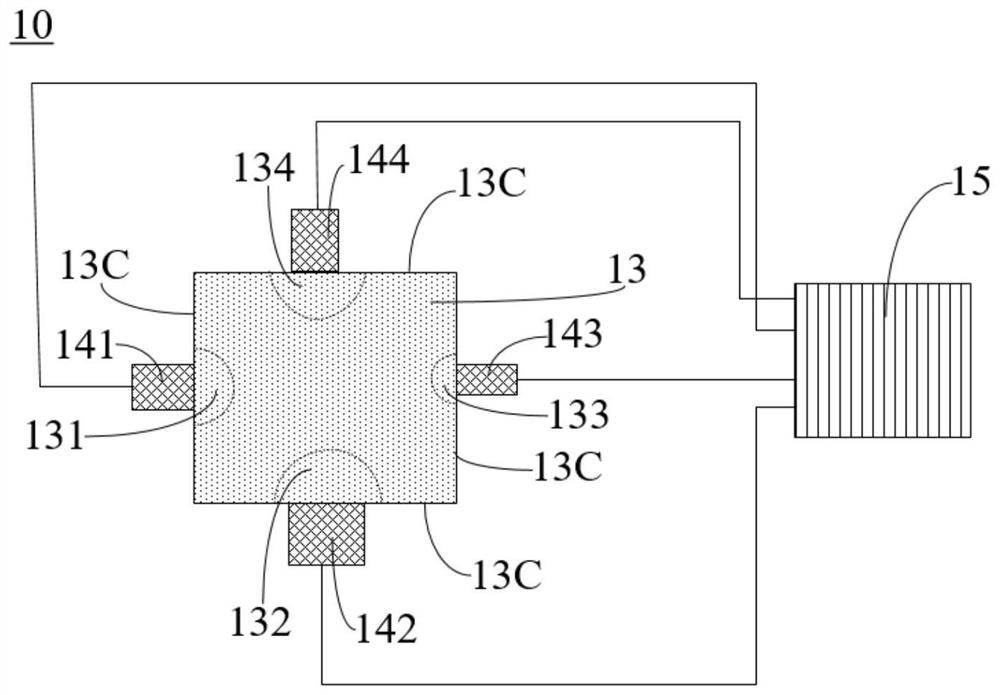

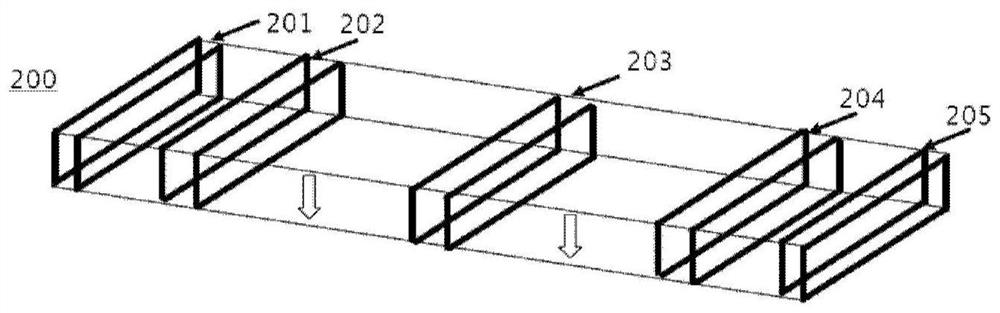

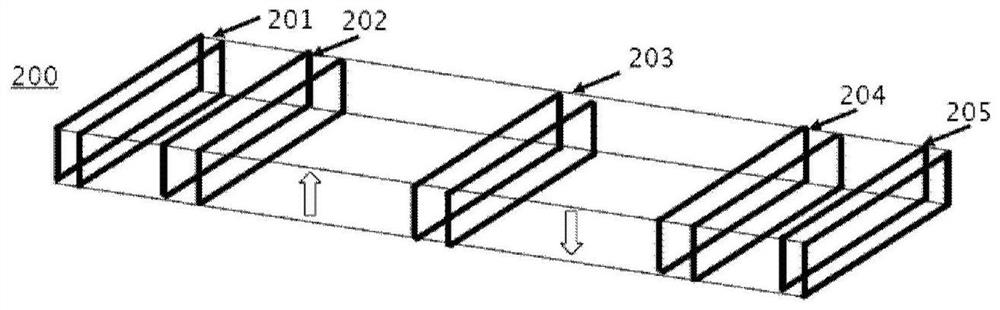

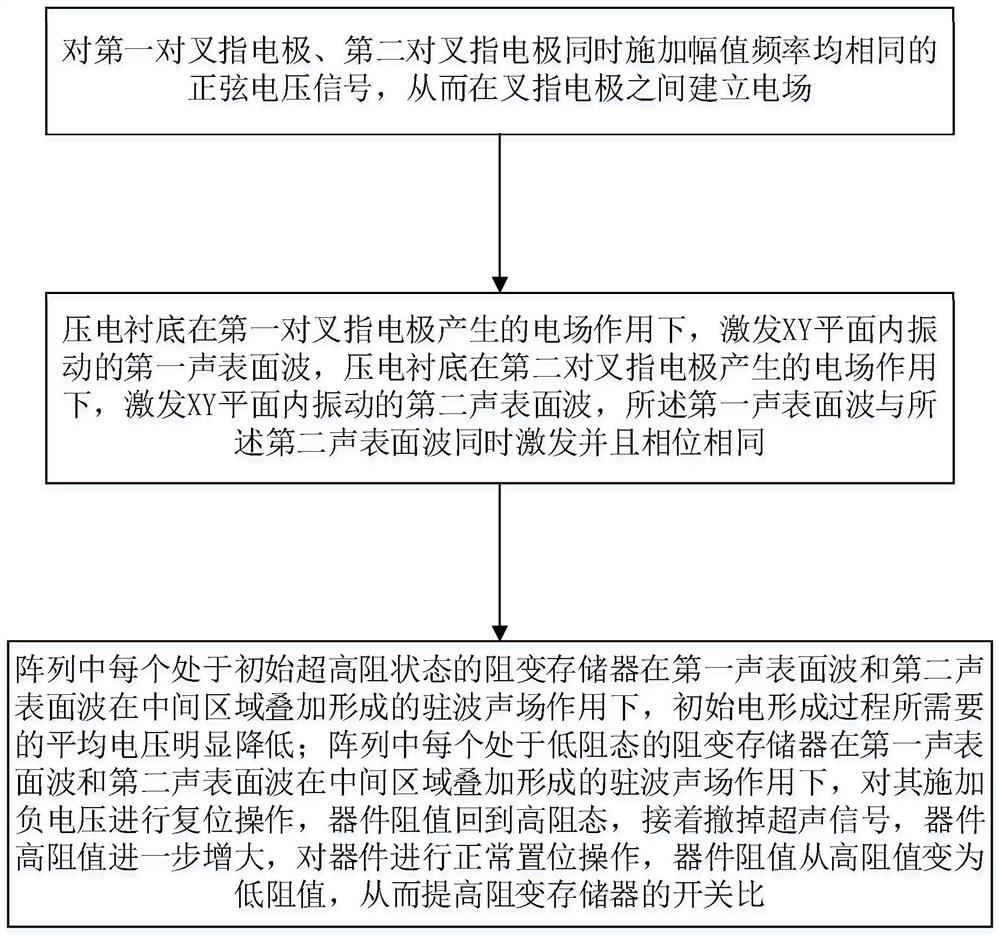

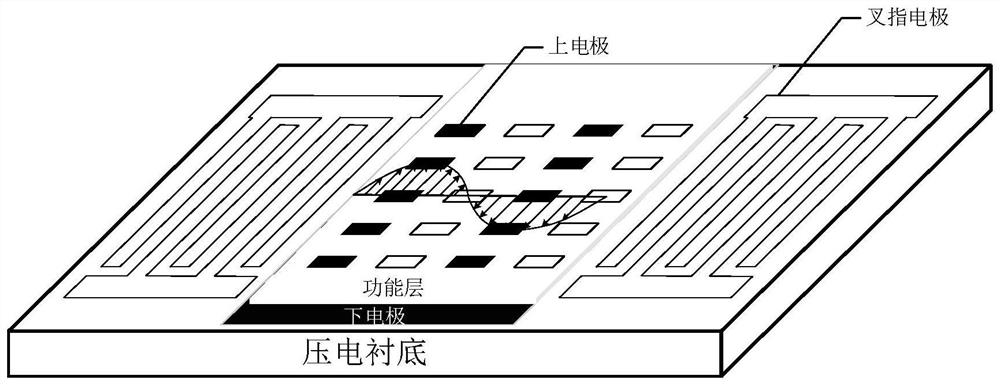

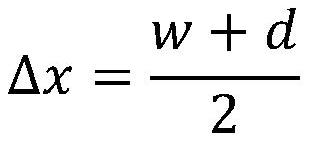

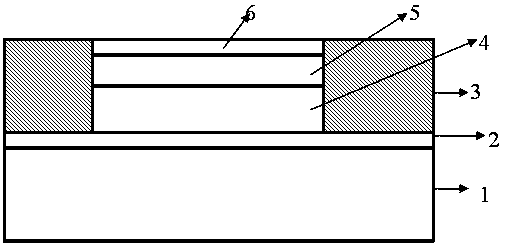

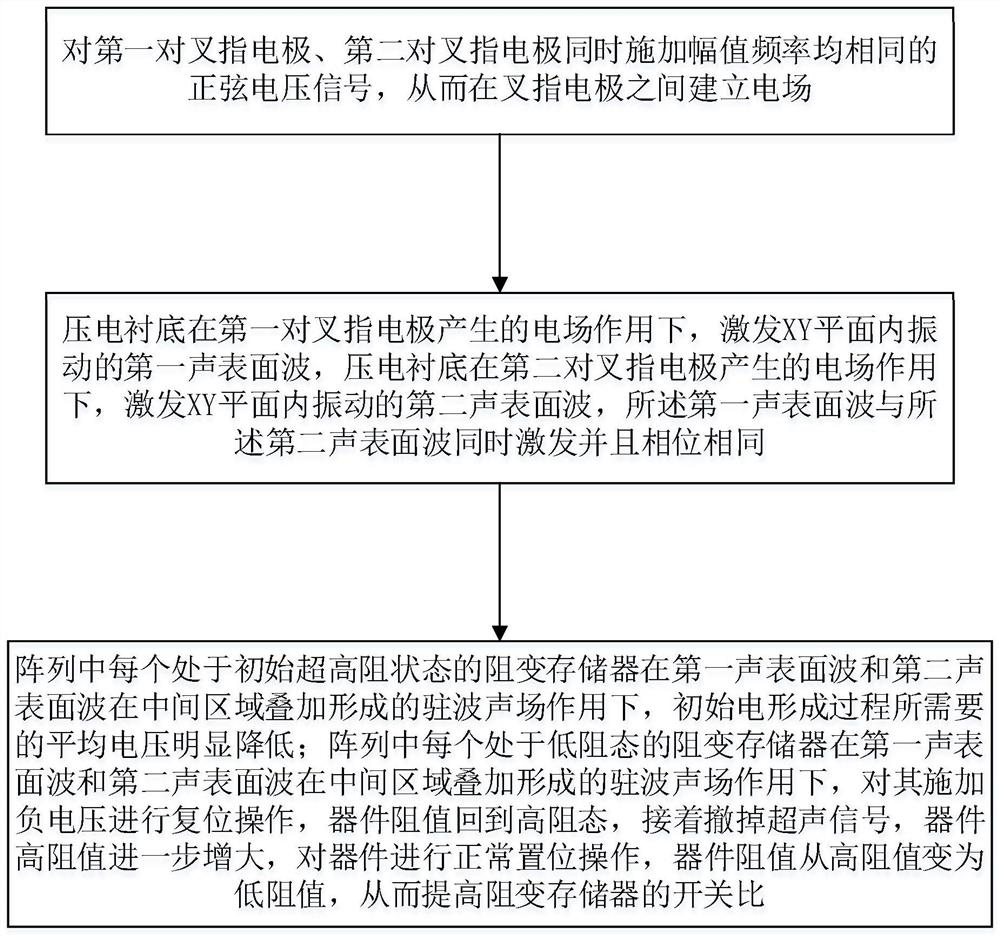

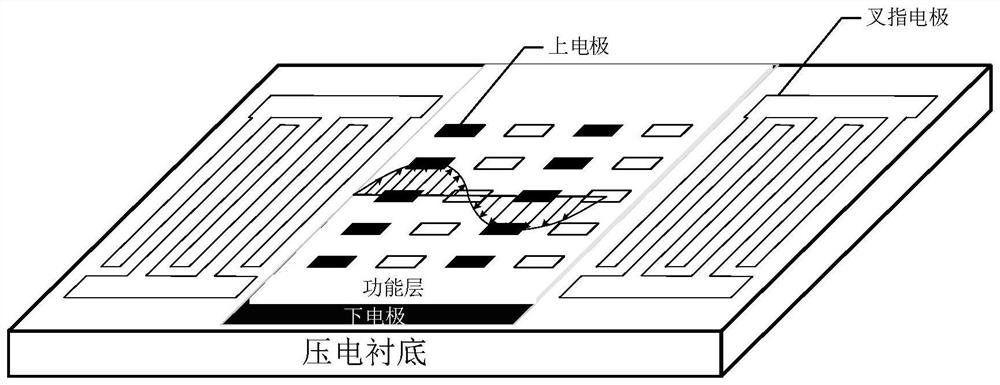

A Method of Ultrasonic Improving the Reliability and Capacity of RRAM

ActiveCN112467028BImprove reliabilityGood for soft dielectric breakdownElectrical apparatusEngineeringLow resistance

The invention discloses a method for ultrasonically improving the reliability and capacity of a resistive variable memory, which belongs to the field of ultrasonic application. In the present invention, under the action of the electric field generated by two pairs of interdigitated electrodes, the piezoelectric substrate simultaneously excites two surface acoustic waves that vibrate in the XY plane and have the same phase, and each resistive variable memory in the initial ultra-high resistance state in the array is Under the action of the standing wave sound field formed by the superposition of two surface acoustic waves in the middle area, the standing wave sound field stretches the functional layer of the resistive memory on the XY plane, which is conducive to soft dielectric breakdown, and the average voltage required for the "electrical formation" process is significantly reduced , improve storage array reliability. Under the action of the standing wave sound field formed by the superposition of the first surface acoustic wave and the second surface acoustic wave in the middle area, the resistive variable memory in the low resistance state applies a negative voltage to reset the device, and the device returns to the high resistance state, and the device is removed. Ultrasonic signal, the high resistance of the device is further increased, and the normal setting operation is performed on the device, thereby significantly improving the switching ratio of the resistive variable memory and increasing the storage capacity.

Owner:HUAZHONG UNIV OF SCI & TECH

A resistive memory cell

InactiveCN105185902BImplement multi-value storageImprove storage densityElectrical apparatusNitrogen oxideDielectric layer

The invention provides a resistive memory unit, and relates to the technical field of non-volatile memory devices. The resistive memory unit comprises a substrate, a lower electrode layer, a function layer, an upper electrode layer and an insulation dielectric layer. The lower electrode layer covers the substrate. The insulation dielectric layer covers the lower electrode layer. A trench is arranged on the insulation dielectric layer, wherein the bottom of the trench extends to the lower electrode layer. The upper electrode layer and the function layer are successively in the trench from top to bottom. The function layer directly contacts the lower electrode layer. The upper electrode layer is flush with the surface of the insulation dielectric layer. The function layer is a resistance variable memory layer, is in an upper and lower layer laminated structure, and is formed by laminating an amorphous SnOx layer and a nitrogen oxide MnOxNy layer. The range of x in the amorphous SnOx is between 0 and 2. The range of x and the range of y in the nitrogen oxide MnOxNy are respectively between 1 and 2 and between 0.001 and 2. According to the resistive memory unit provided by the invention, stable multi-value memory is realized, and the memory density and stability of the memory unit can be improved.

Owner:HENAN UNIV OF SCI & TECH

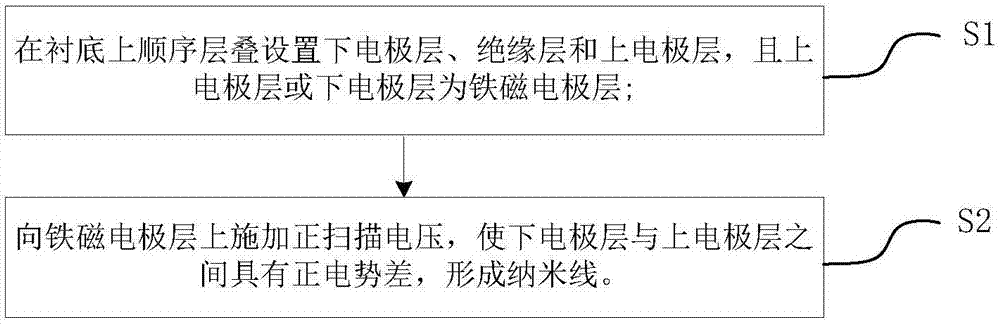

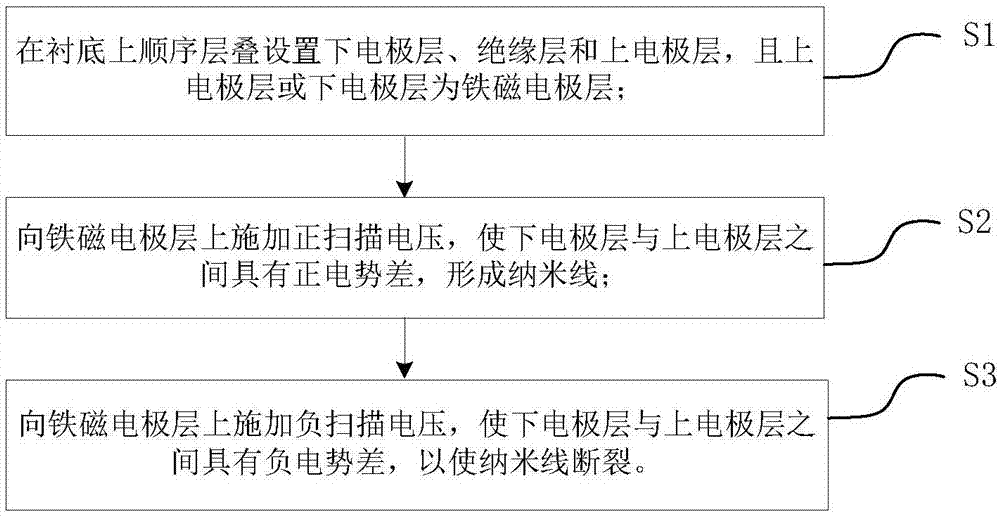

Construction method of nanowire and data storage method

InactiveCN107068857ASimple manufacturing processReduce manufacturing costNanomagnetismNanoinformaticsInsulation layerNanowire

The invention provides a construction method of a nanowire and a data storage method. The construction method of the nanowire comprises the following steps of S1, sequentially arranging a lower electrode layer, an insulation layer and an upper electrode layer on a substrate in a lamination way, wherein the upper electrode layer or the lower electrode layer is a ferromagnetic electrode layer; and S2, applying a positive scanning voltage onto the ferromagnetic electrode layer so that positive potential difference exists between the lower electrode layer and the upper electrode layer to form the nanowire. Compared with the construction method of the nanowire in the prior art, the construction method provided by the invention has the advantages that the preparation process is simplified, the preparation cost is reduced, the process stability and the preparation efficiency are improved, and the construction method can be widely applied and promoted; and moreover, after the construction method of the nanowire is applied to a storage structure of M / I / M, a resistance random access effect and a spin correlation effect can be simultaneously achieved, so that multi-state operation and multi-value storage in a simple structure are achieved, and a carrier is provided for a multi-stage storage device by a magnetoelectric coupling effect.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Phase change film material of silicon-adulterated sulfur series for phase change memory

InactiveCN100477318CAchieve reversible transformationImplement multi-value storageChalcogenide/metal/alloy compound compositionsElectrical apparatusElectrical resistance and conductancePhase-change memory

The invention is concerned with the phase change film material containing silicon series cluster subject, that is the silicon group subject alloy TeaSibSb100-(a+b) with the a no lesser than 48 but no more than 60, and the b no less than 8 but no more than 40. The invention has the higher crystalline state resistance and non / crystalline resistance change ratio compare to the Ge2Sb2Te5 phase change film, the lower change ratio of the non / crystalline film thickness and melting point. The memorizer including the Si series sulfur group subject phase change film is with the higher ratio sum of the switch stability and it helps the writing operation current.

Owner:SHANGHAI JIAOTONG UNIV +1

Circuit and method for driving resistive random access memory to realize multi-valued storage

ActiveCN101783170BImplement multi-value storageHigh densityDigital storageCapacitanceStatic random-access memory

The invention discloses a circuit and a method for driving a resistive random access memory to realize multi-valued storage by using a capacitor. The circuit consists of a plurality of capacitors which are used for storing electric energy and have different capacitances, a plurality of voltage sources, the resistive random access memory, and a switching circuit, wherein the capacitors are connected to the voltage sources and the resistive random access memory through the switching circuit. The method comprises the following steps of: charging the capacitors having different capacitances to make the capacitors have the same voltage, or charging the capacitors having the same capacitance to make the capacitors have different voltages so as to make the capacitors store different electric energy; and then driving the resistive random access memory by using the capacitors having different electrical energy as signal excitation sources, and changing the resistance state of the resistive random access memory so as to make the resistive random access memory have different resistance states and realize the multi-valued storage. By using the circuit and the method, the multi-valued storage is realized by using a simple circuit to drive the resistive random access memory, and storage with a higher density in the same area is realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for ultrasonically improving reliability and capacity of resistive random access memory

ActiveCN112467028AImprove reliabilityGood for soft dielectric breakdownElectrical apparatusEngineeringElectrical breakdown

The invention discloses a method for ultrasonically improving reliability and capacity of a resistive random access memory, which belongs to the field of ultrasonic application. Under the action of anelectric field generated by the two pairs of interdigital electrodes, the piezoelectric substrate excites the two surface acoustic waves which vibrate in the XY plane and have the same phase at the same time, and each resistive random access memory in an initial ultrahigh resistance state in the array is under the action of a standing wave sound field formed by superposing the two surface acoustic waves in the middle area, the standing wave sound field stretches the resistive random access memory functional layer on the XY plane, soft dielectric breakdown is facilitated, the average voltage required in the electrical forming process is obviously reduced, and the reliability of the memory array is improved. The resistive random access memory in the low impedance state applies negative voltage for reset operation under the action of a standing wave sound field formed by superposing the first surface acoustic wave and the second surface acoustic wave in the middle area, the device returns to the high impedance state, the ultrasonic signal is removed, the high resistance of the device is further increased, and normal setting operation is performed on the device. Therefore, the switching ratio of the resistive random access memory is remarkably improved and the storage capacity is improved.

Owner:HUAZHONG UNIV OF SCI & TECH

Memory cell, control method of memory cell, and memory chip

InactiveCN112086116AImprove storage densityImplement multi-value storageDigital storagePhysicsHeat output

The invention provides a memory cell including a first electrode, a heater including a plurality of sub-heaters, a phase-change material layer, and a second electrode; wherein the phase-change material layer is located between the second electrode and the first electrode and is electrically connected with the second electrode, one end of each sub-heater is electrically connected with the first electrode, and the other end of each sub-heater is electrically connected with different areas of the phase-change material layer. At least two sub-heaters in the plurality of sub-heaters are different in heat output to the phase-change material layer within the same time, so that the memory cell can present at least three different resistance states, and each resistance state of the memory cell canrepresent binary data respectively. Therefore, multi-valued storage is realized on the premise of not changing the size of the memory cell, and the storage density of the memory cell is increased.

Owner:YANGTZE MEMORY TECH CO LTD

A kind of preparation method of resistance type memory cell

InactiveCN105185903BImplement multi-value storageImprove storage densitySolid-state devicesSemiconductor devicesConductive materialsNitrogen oxide

A method for preparing a resistive memory unit, which relates to the technical field of nonvolatile memory devices. First, a lower electrode layer is formed on a substrate with a conductive material, and an insulating dielectric layer is deposited or spin-coated on the lower electrode layer. The process forms a trench on the insulating dielectric layer, and the bottom of the trench is connected to the lower electrode layer; then, the functional layer of the resistive memory unit is formed in the trench, and the functional layer is a stacked structure of upper and lower layers. It is composed of an amorphous SnOx layer and a oxynitride MnOxNy layer, and the range of x in the amorphous SnOx is 0

Owner:HENAN UNIV OF SCI & TECH

Phase change film material of silicon-adulterated sulfur series for phase change memory

InactiveCN100511749CAchieve reversible transformationImplement multi-value storageChalcogenide/metal/alloy compound compositionsElectrical apparatusPhase-change memoryGe element

Owner:SHANGHAI JIAOTONG UNIV +1

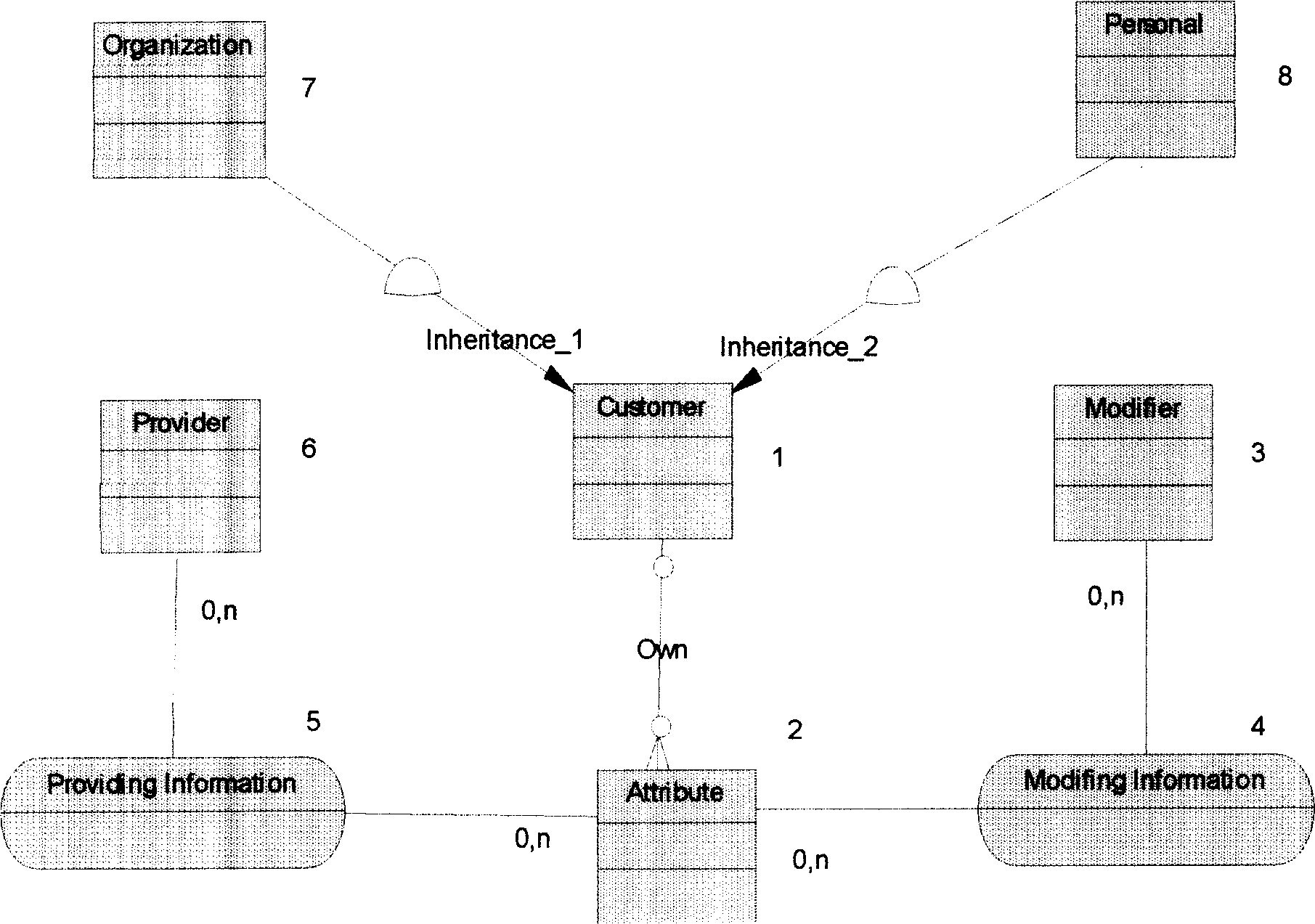

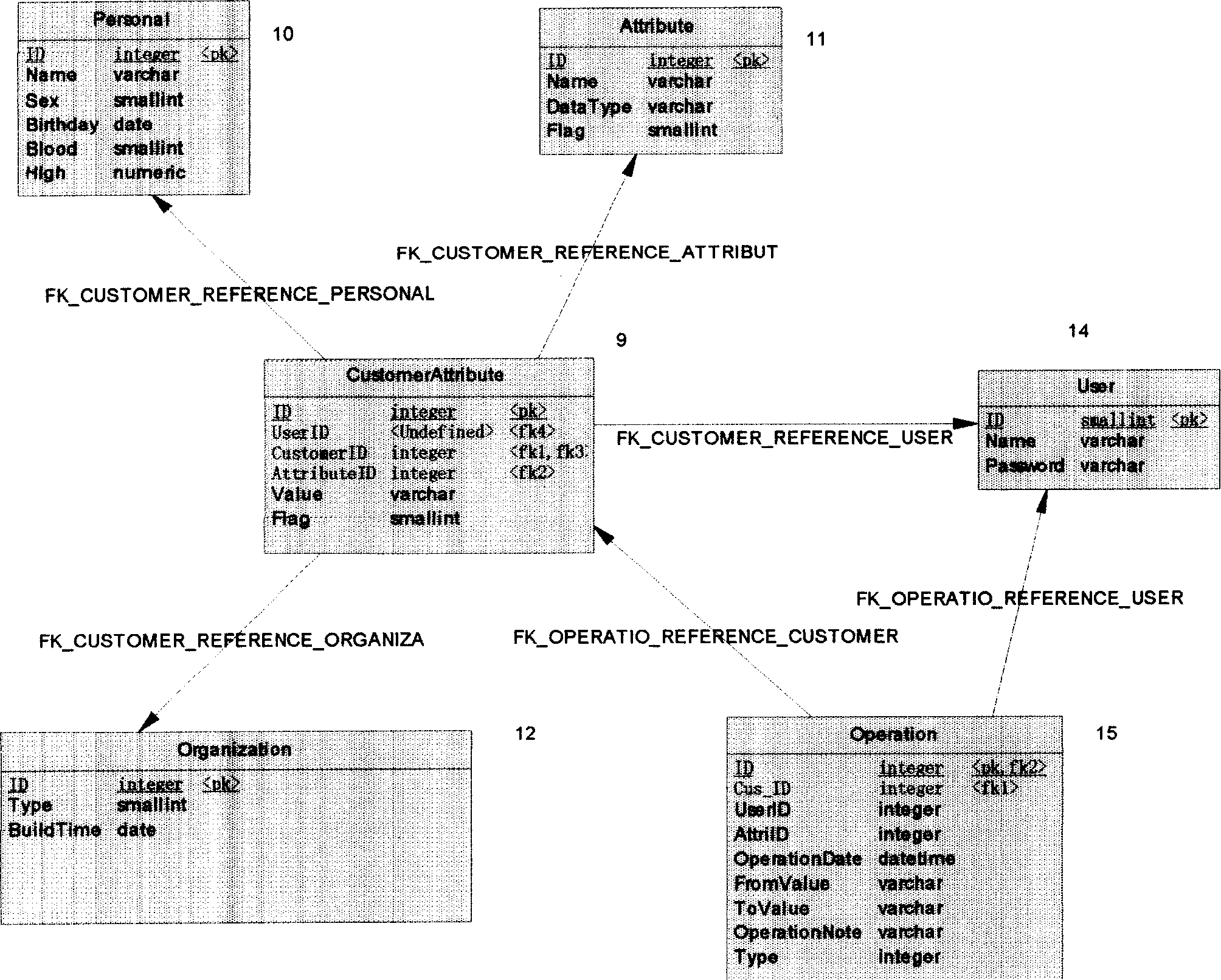

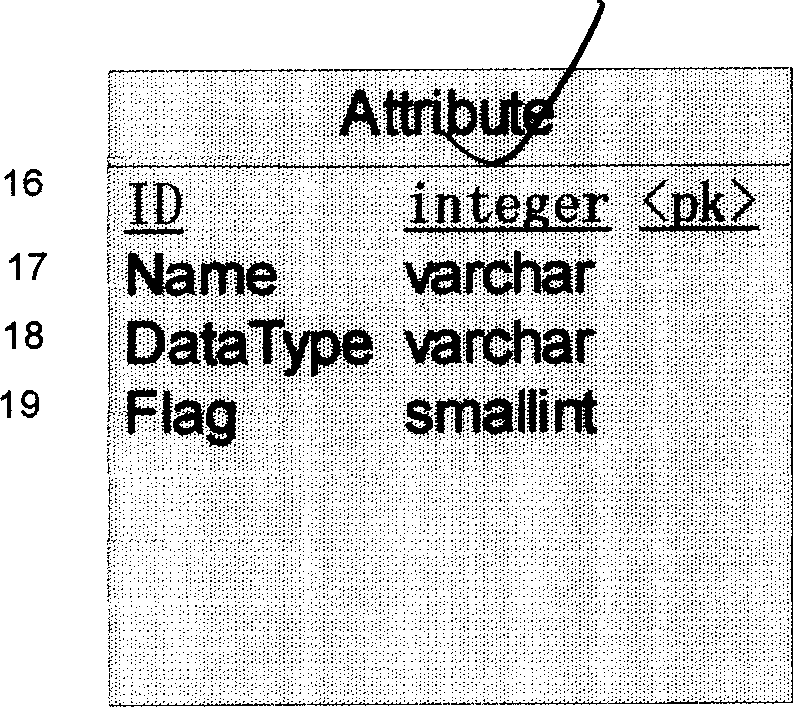

Realizing method of integratiy of customer data

InactiveCN1680948AAccurate and complete storageImplement multi-value storageSpecial data processing applicationsData providerClient data

A method for realizing completeness of client data includes distinguishing personal client data and unit client data, distinguishing unit value basic attribute and multivalue self - defined attribute of client data and recording information of data provider, data reviser, data value prior to revision, data value after revision, etc in detail way.

Owner:丁力

A Resistive Variable Memory Capable of Realizing Multi-value Storage

ActiveCN103682096BImprove storage densityImplement multi-value storageElectrical apparatusEngineeringUnit structure

The invention discloses a resistive random access memory capable of realizing multilevel storage. The resistive random access memory capable of realizing the multilevel storage comprises a semiconductor substrate, N-1 groups of double-layer structures and top electrodes on the N-1 groups of double-layer structures, wherein each N-1 group of double-layer structure consists of an electrode and one resistive layer positioned on the electrode; the N-1 groups of double-layer structures are positioned on the substrate and are successively overlaid from bottom to top, wherein N is a positive integer greater than or equal to 3; all odd-number electrodes from bottom to top are connected in parallel to serve as the lower electrode of the resistive random access memory; all even-number electrodes from bottom to top are connected in parallel to serve as the upper electrode of the resistive random access memory. Therefore, according to the resistive random access memory capable of realizing the multilevel storage, which is disclosed by the invention, in a mode that multiple electrodes and the resistive layers are alternatively overlaid, voltages required for each resistive layer to generate resistance change are different, resistance values after the resistance change happens are different, so that the multilevel storage of a memory unit structure is realized, and no additional area is occupied by the memory unit disclosed by the invention because of adopting a longitudinal-overlaying structure.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT