A high reliability parameter configuration method based on asic

A parameter configuration method and parameter configuration module technology, which are applied in general-purpose stored program computers and other directions, can solve problems such as threshold voltage reduction and single event effect threat, and achieve the effects of ensuring correctness, reliability, and flexible reading.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

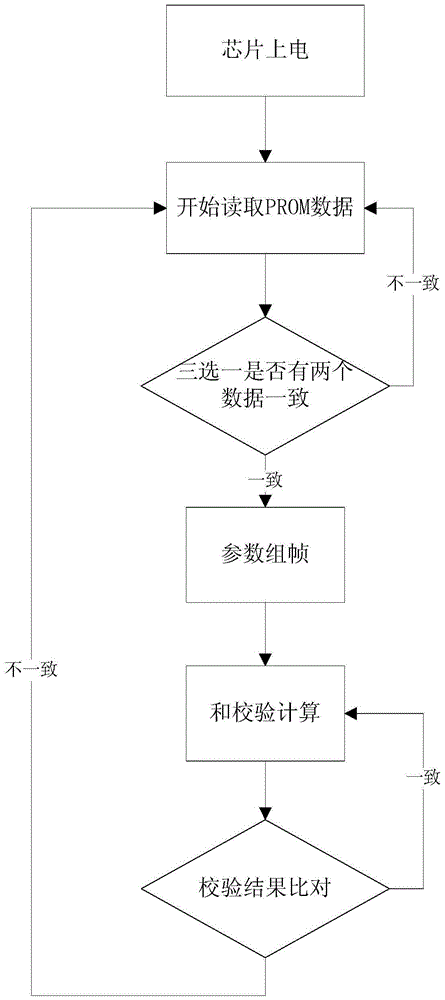

[0054] Such as figure 1 As shown, the ASIC-based high reliability parameter configuration method of the present invention, the steps are:

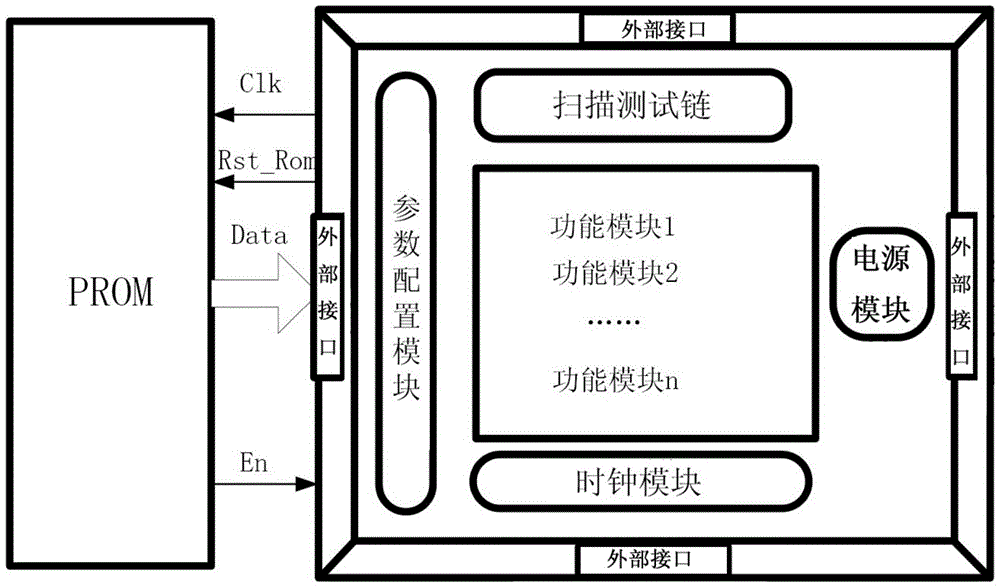

[0055] S1: Hardware structure of ASIC configuration;

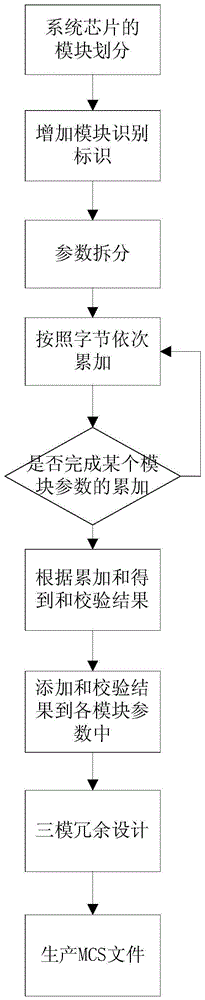

[0056] S2: Reinforce the chip configuration parameters, perform redundancy according to the function division of the system chip, and add module parameter identification marks to distinguish the parameters of each module;

[0057] S3: Store the parameters to be configured in a programmable read-only memory (hereinafter referred to as PROM Programmable Read-Only Memory) outside the system chip;

[0058] S4: After the system chip is powered on, after determining that the internal clock of the system chip is stable, open the parameter configuration module;

[0059] S5: Through the parameter configuration module inside the system chip, start to r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More