A kind of multi-chip side glue removal method

A multi-chip and edge glue technology, which is applied in the direction of equipment, photoplate making process of pattern surface, optics, etc., can solve the problems of wasting chip area and difficult to realize edge washing method, so as to improve production efficiency, avoid chip area waste, The effect of avoiding damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The specific implementation manner of the present invention will be described below in conjunction with the accompanying drawings.

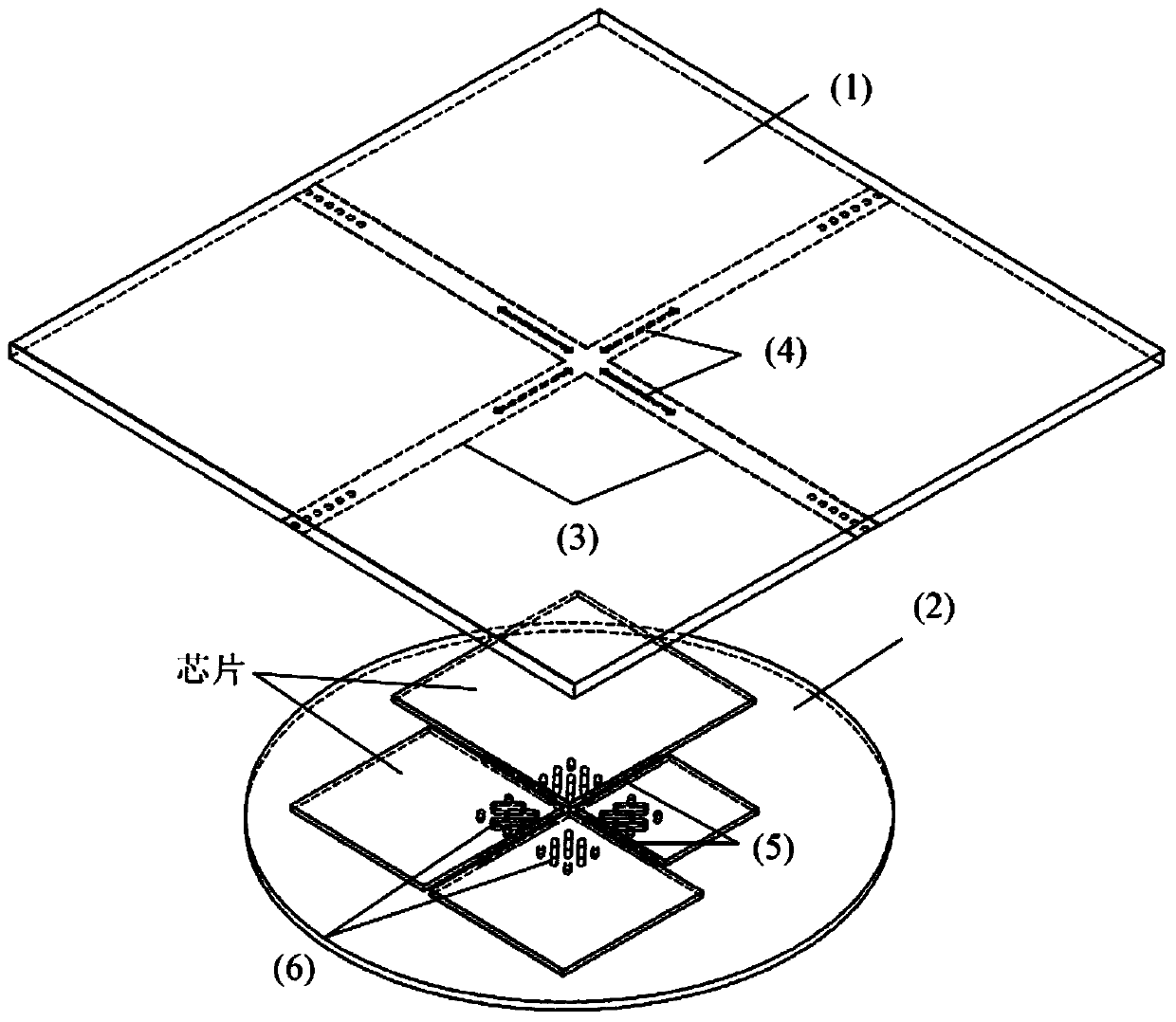

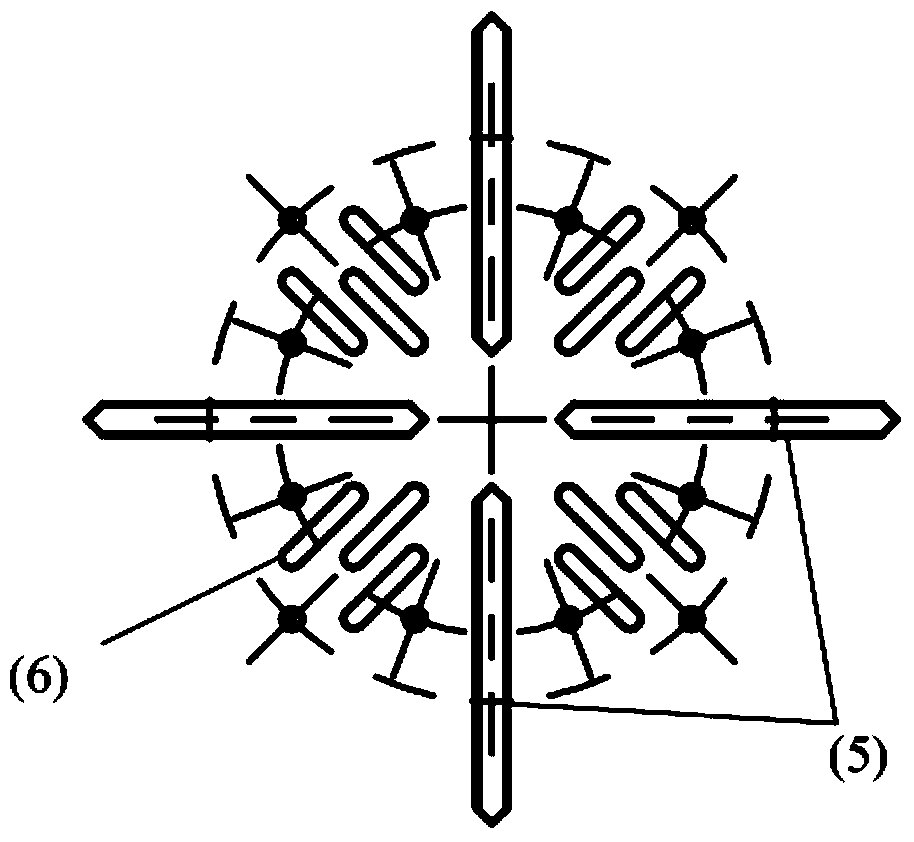

[0018] A method for removing multi-chip edge glue in this embodiment includes a 5-inch photolithography mask (1) for selectively exposing the chip edge glue and a sample suction cup (2) for carrying and positioning chips, the suction cup with a diameter of 4 inches, such as figure 1 shown.

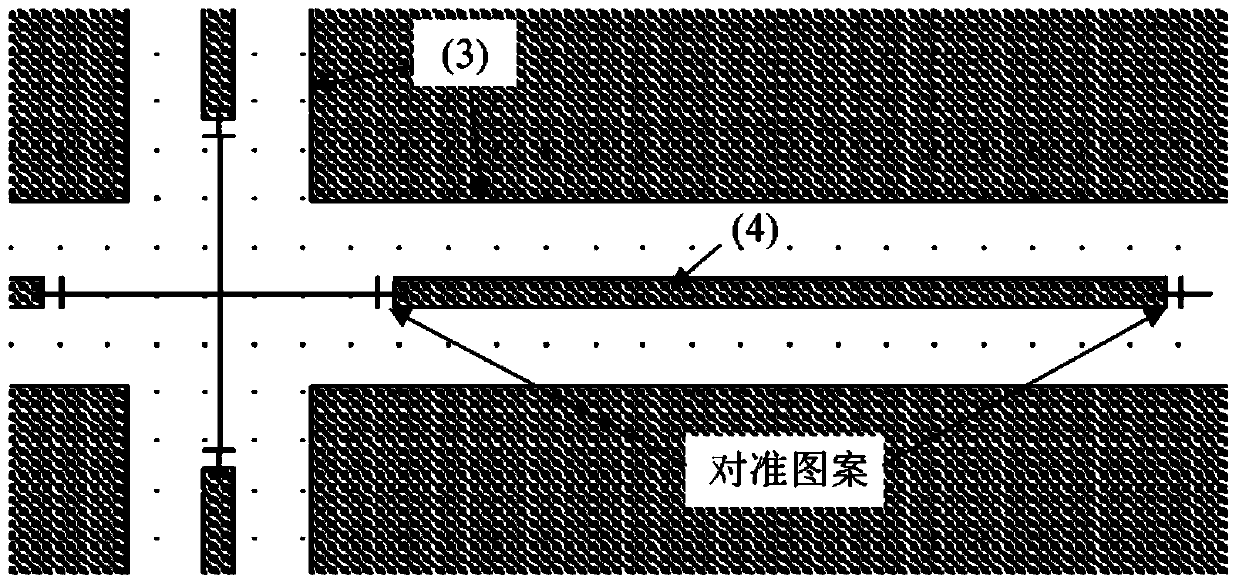

[0019] There is a cross figure (3) covering the whole photoresist plate on the photolithographic mask plate (1). The inside of the cross figure (3) is light-transmissive as a whole, and its outer area is opaque. There are four inside the cross figure (3). A strip-shaped registration mark (4); the registration marks (4) are opaque and arranged in a cross, and the center of symmetry is the center of the cross figure (3); the two ends of each registration mark are aligned pattern, the alignment pattern is a cross, such as figure 2 shown;

[0020] The...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More