Silicon gate graphene/black phosphorus transistor and preparation method

A graphene and transistor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of unfavorable semiconductor device integration and incompatibility, and achieve the effect of guaranteed performance, easy control, and good gate dielectric quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

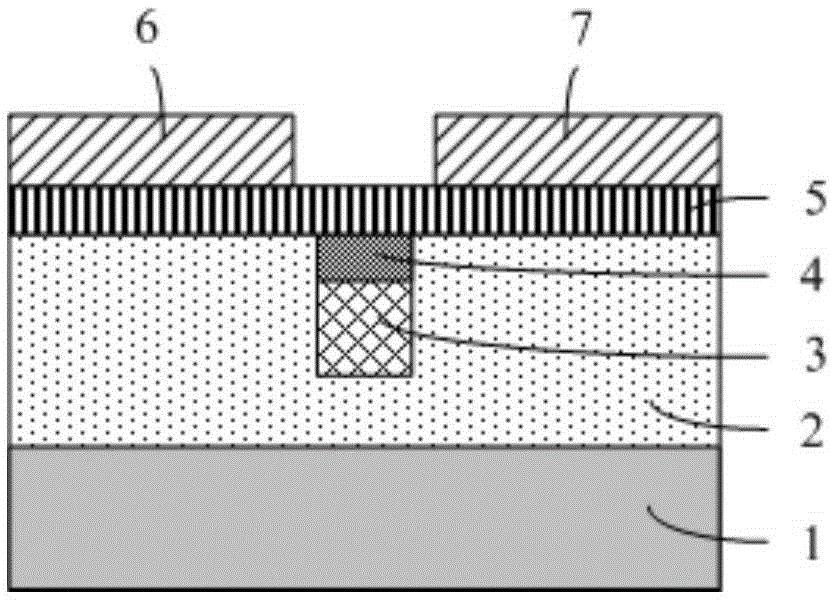

[0039] Embodiment 1: see figure 1 .

[0040] The transistor in this embodiment includes a substrate 1, 2 layers of isolating silicon oxide, 3 gate electrodes of polysilicon, a gate dielectric 4, a source electrode 6, and a drain electrode 7, and the substrate 1 is provided with 2 layers of isolating silicon oxide, and 2 layers of isolating silicon oxide A silicon oxide groove is arranged on the silicon oxide groove, and a polysilicon 3 gate electrode and a gate dielectric 4 are arranged in the silicon oxide groove, 2 layers of isolating silicon oxide and 5 layers of graphene / black phosphorus are arranged on the silicon oxide groove, and 5 layers of graphene / black phosphorus are arranged on the graphene / black phosphorus 5 A source electrode 6 and a drain electrode 7 are arranged above the layer. The gate electrode is polysilicon 3, and the gate dielectric 4 is silicon oxide.

Embodiment 2

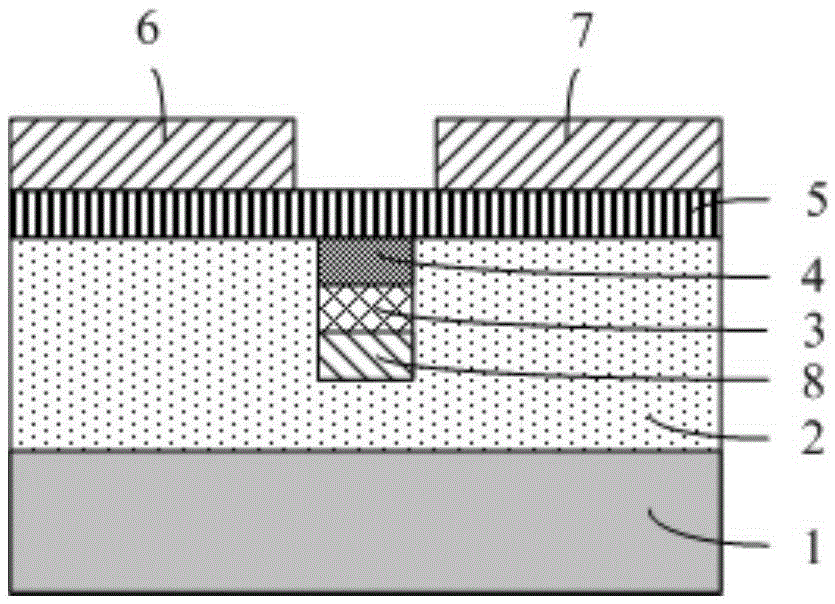

[0041] Example 2: see figure 2 .

[0042] The difference between this embodiment and Embodiment 1 is that the gate electrode of this embodiment is an overlapping combination of refractory metal 8 and polysilicon 3 , refractory metal 8 is at the bottom of the silicon oxide tank, and polysilicon 3 is above the refractory metal.

Embodiment 3

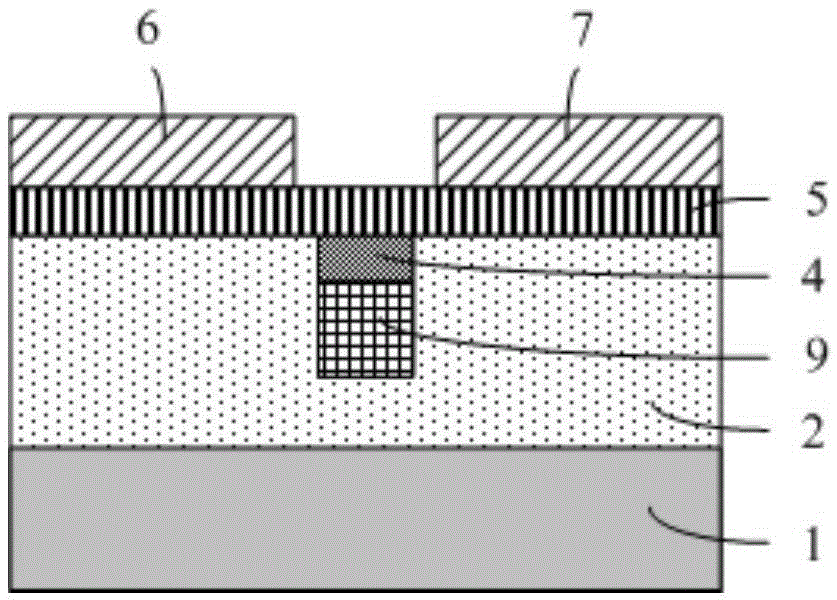

[0043] Embodiment 3: see image 3 .

[0044] The difference between this embodiment and Embodiment 1 is that the gate electrode of this embodiment is a refractory metal silicide 9 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More