Fabrication method for test element group (TEG) test key on a thin film transistor (TFT) array substrate

A technology of an array substrate and a manufacturing method, which is applied in the field of manufacturing TEG test keys on a TFT array substrate, can solve the problems of large photoresist pattern area and difficulty in removing the photoresist, so as to achieve increased area, easy photoresist stripping process, and The effect of reducing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to further illustrate the technical means adopted by the present invention and its effects, the following describes in detail in conjunction with preferred embodiments of the present invention and accompanying drawings.

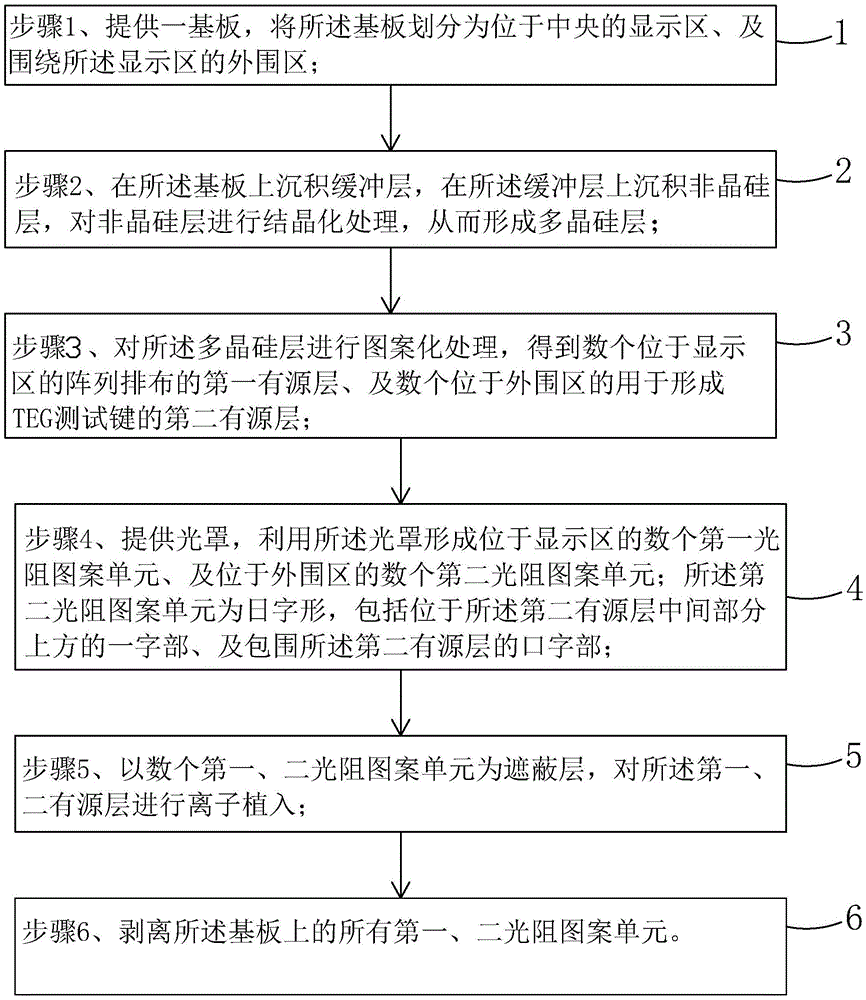

[0038] see figure 2, the manufacture method of TEG test key on a kind of TFT array substrate provided by the invention, comprises the following steps:

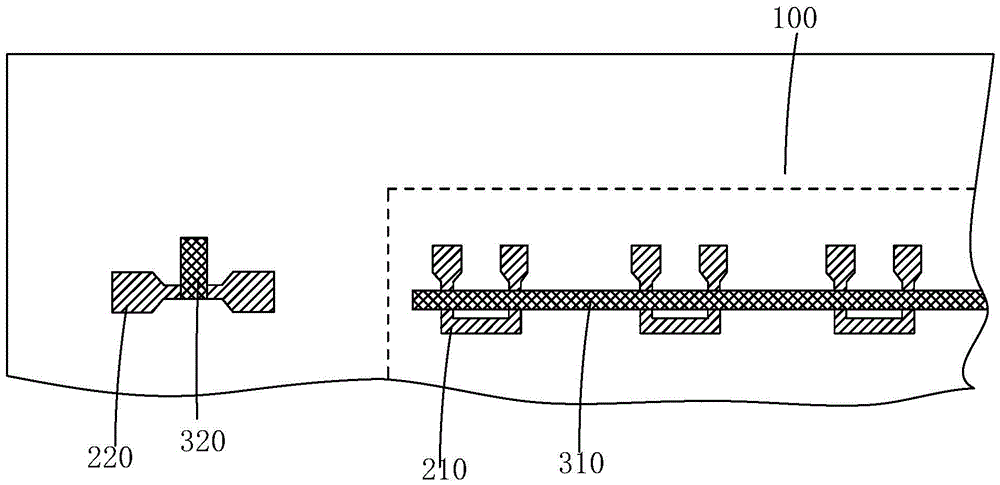

[0039] Step 1. Provide a substrate 10 , and divide the substrate 10 into a central display area 11 and a peripheral area 12 surrounding the display area 11 .

[0040] Preferably, the substrate 10 is a glass substrate.

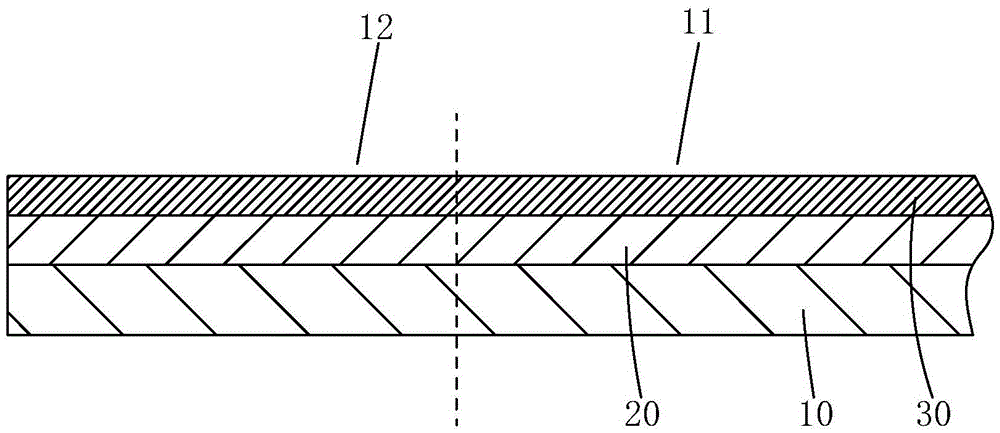

[0041] Step 2, such as image 3 As shown, a buffer layer 20 is deposited on the substrate 10 , an amorphous silicon layer is deposited on the buffer layer 20 , and the amorphous silicon layer is crystallized to form a polysilicon layer 30 .

[0042] Specifically, the amorphous silicon layer is crystallized through a rapid thermal annealing process.

[0043] Step 3, if Fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com