Circuit simulation method for fin edge roughness effect in fin type field effect transistor

A field effect transistor and circuit simulation technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as unpredictability, wrong estimation of circuit fluctuations, and inability to take into account changes in device fluctuations.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The circuit simulation method for the roughness of the fin edge in the fin field effect transistor provided by the present invention will be described in detail below by way of examples and in conjunction with the accompanying drawings.

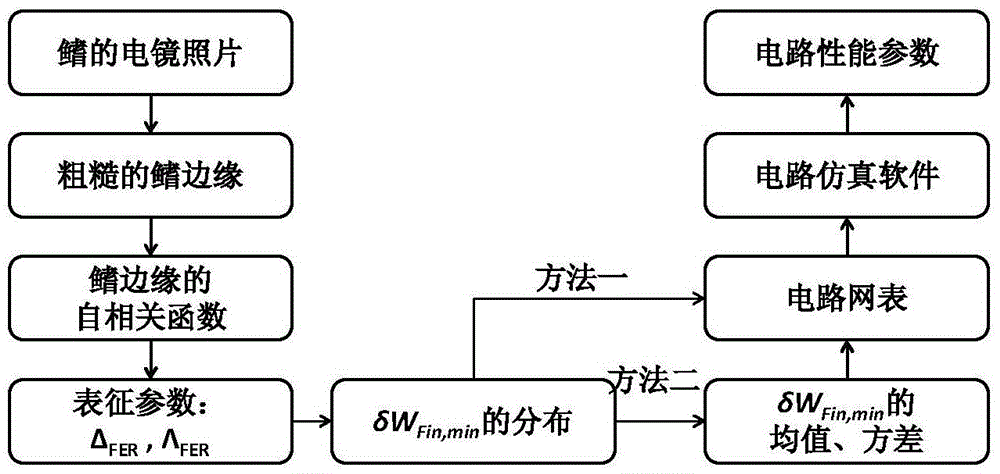

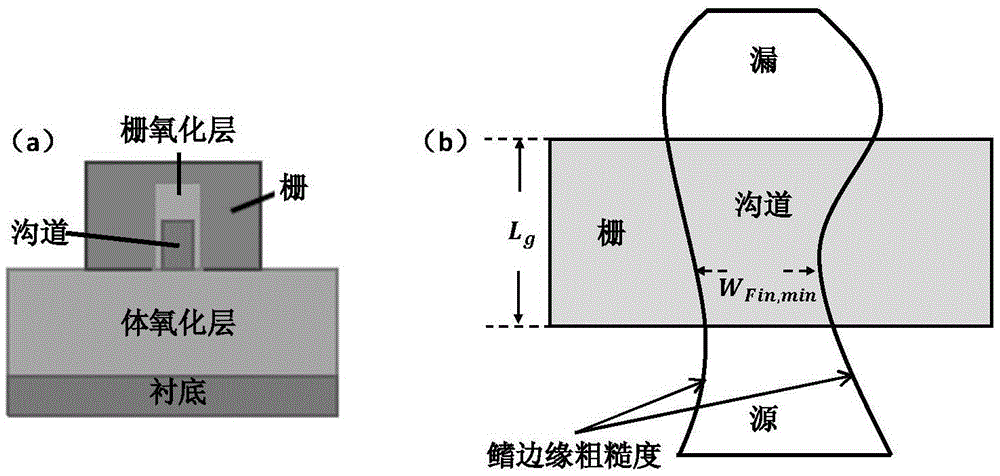

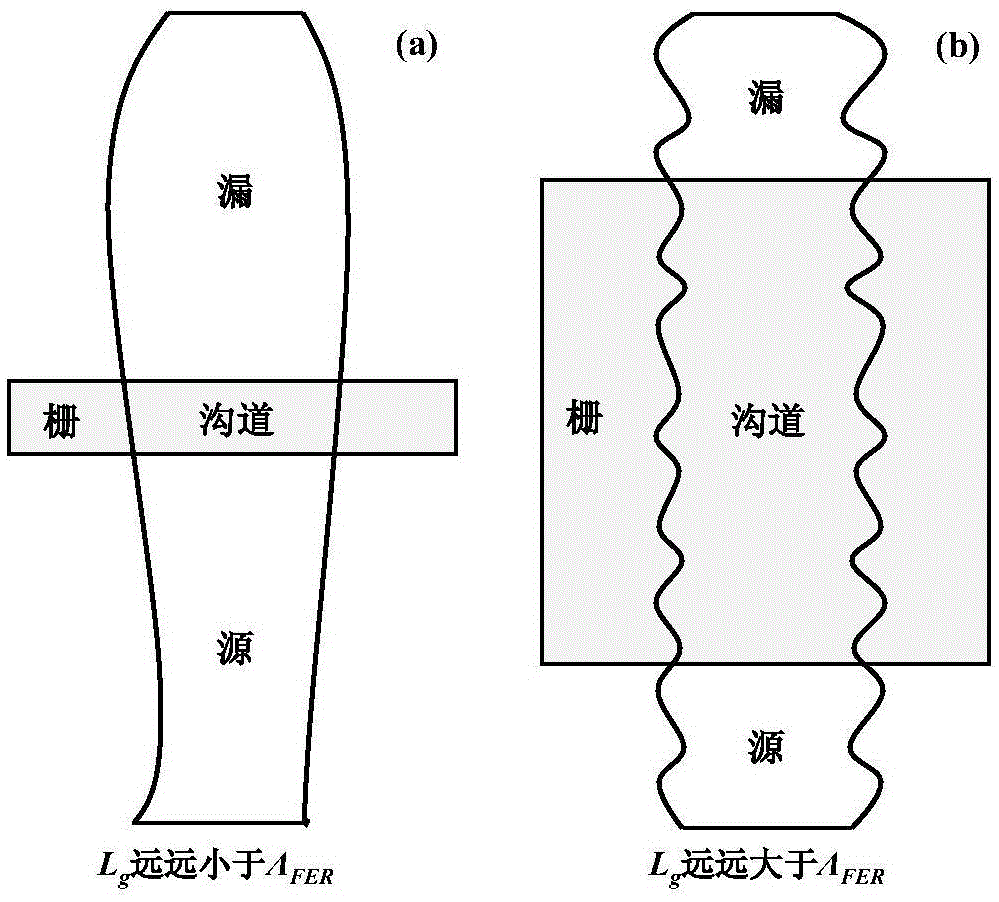

[0028] This example considers the influence of fin edge roughness on the performance parameter of static random access memory (SRAM) circuit - static noise margin (SNM) in dual-gate fin field effect transistor based on SOI substrate. The overall process is as follows figure 1 shown. The basic structure and parameters of the double-gate fin field effect transistor are defined as figure 2 shown. Among them, L g much smaller than Λ FER and L g much larger than Λ FER The schematic diagrams of fin edge roughness in these two extreme cases are shown in image 3 shown.

[0029] Specific steps:

[0030] 1) if Figure 4 As shown, according to the electron microscope photo of the grid, the rough grid edge is extracted, its autocorrelat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More