Manufacturing method of groove-type super junction device

A manufacturing method and super-junction technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as difficulty in improving epitaxial filling process, affecting production yield, and increasing reverse leakage current of devices, so as to achieve improvement The effect of EMI performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

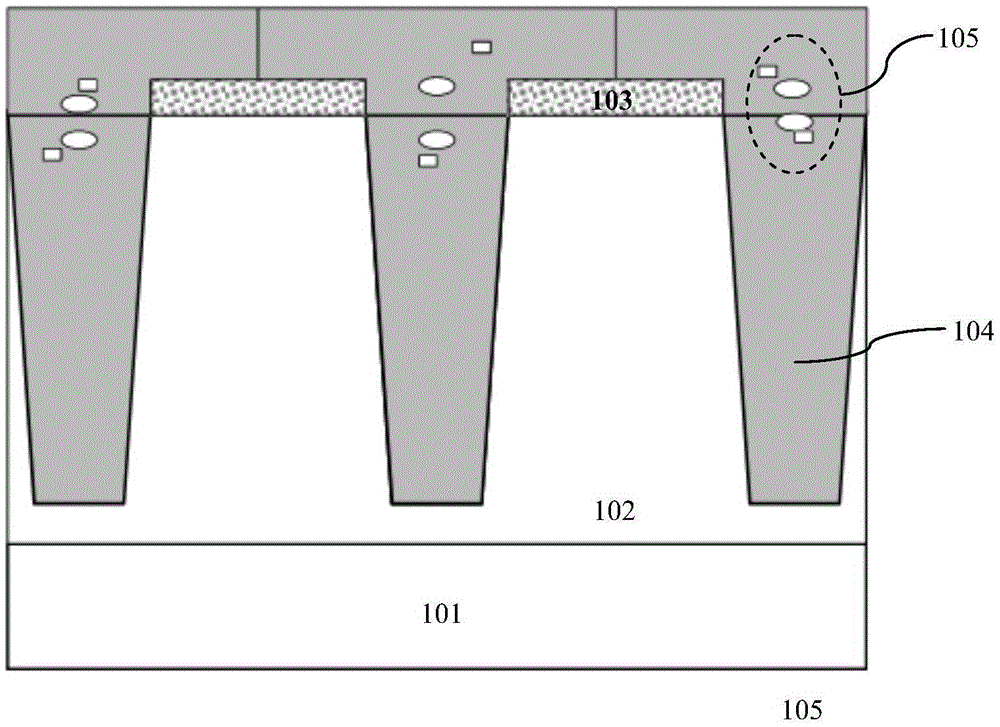

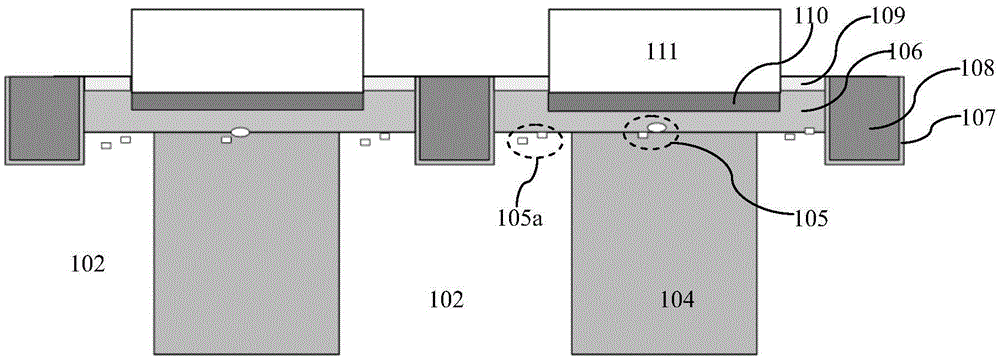

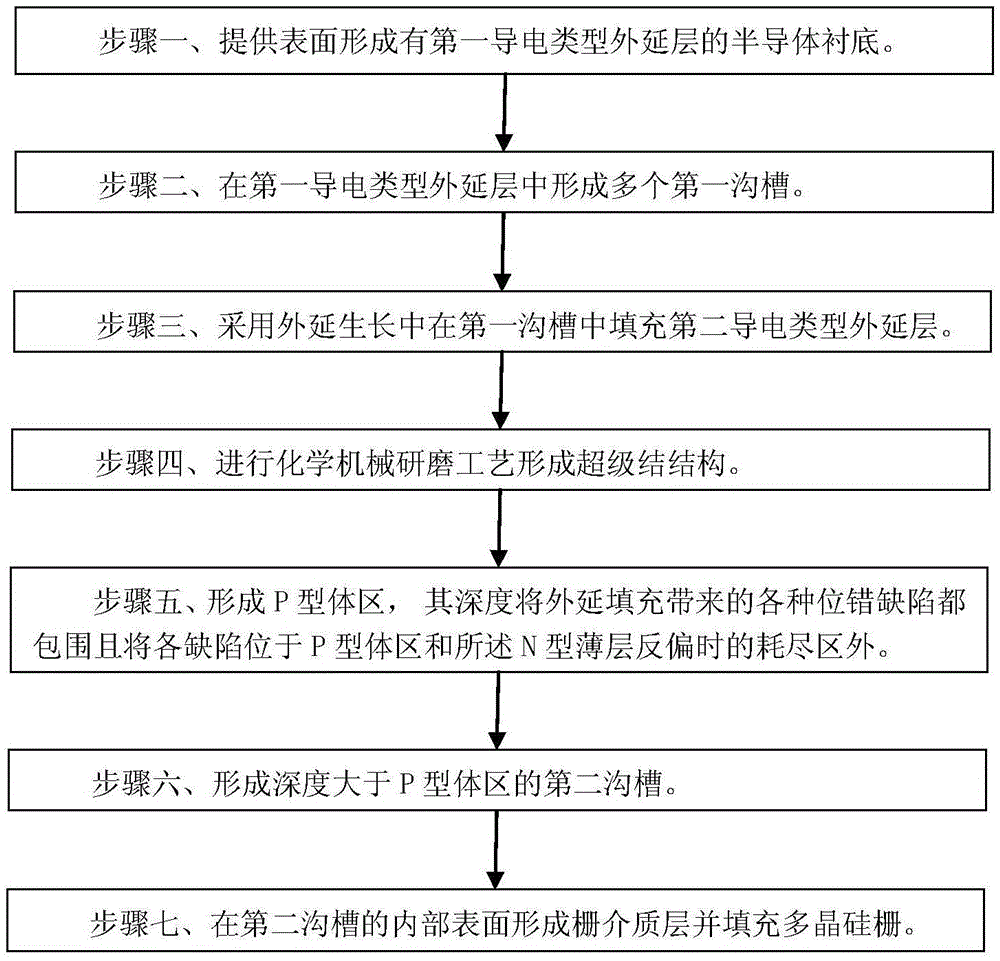

[0047] Firstly, the problems of existing trench superjunction manufacturing methods are introduced, such as figure 1 Shown is a schematic diagram of the structure of the super junction formed by the manufacturing method of the existing trench type super junction device; the existing method includes the following steps:

[0048] Step 1: Provide a semiconductor substrate such as a silicon substrate 101 , and an N-type epitaxial layer such as an N-type silicon epitaxial layer 102 is formed on the surface of the semiconductor substrate 101 .

[0049] Step 2: Forming a plurality of trenches in the N-type epitaxial layer 102 by photolithography. The hard mask layer 103 is used when etching the trench.

[0050] Step 3: filling the trench with a P-type epitaxial layer such as a P-type silicon epitaxial layer 104 during epitaxial growth, and the P-type epitaxial layer 104 will simultaneously extend to the surface of the N-type epitaxial layer 102 outside the trench.

[0051] Depend o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More