Patents

Literature

130results about How to "Reduce switching speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

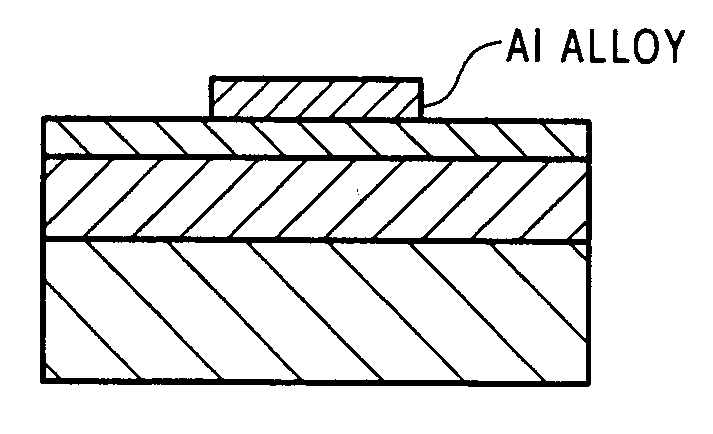

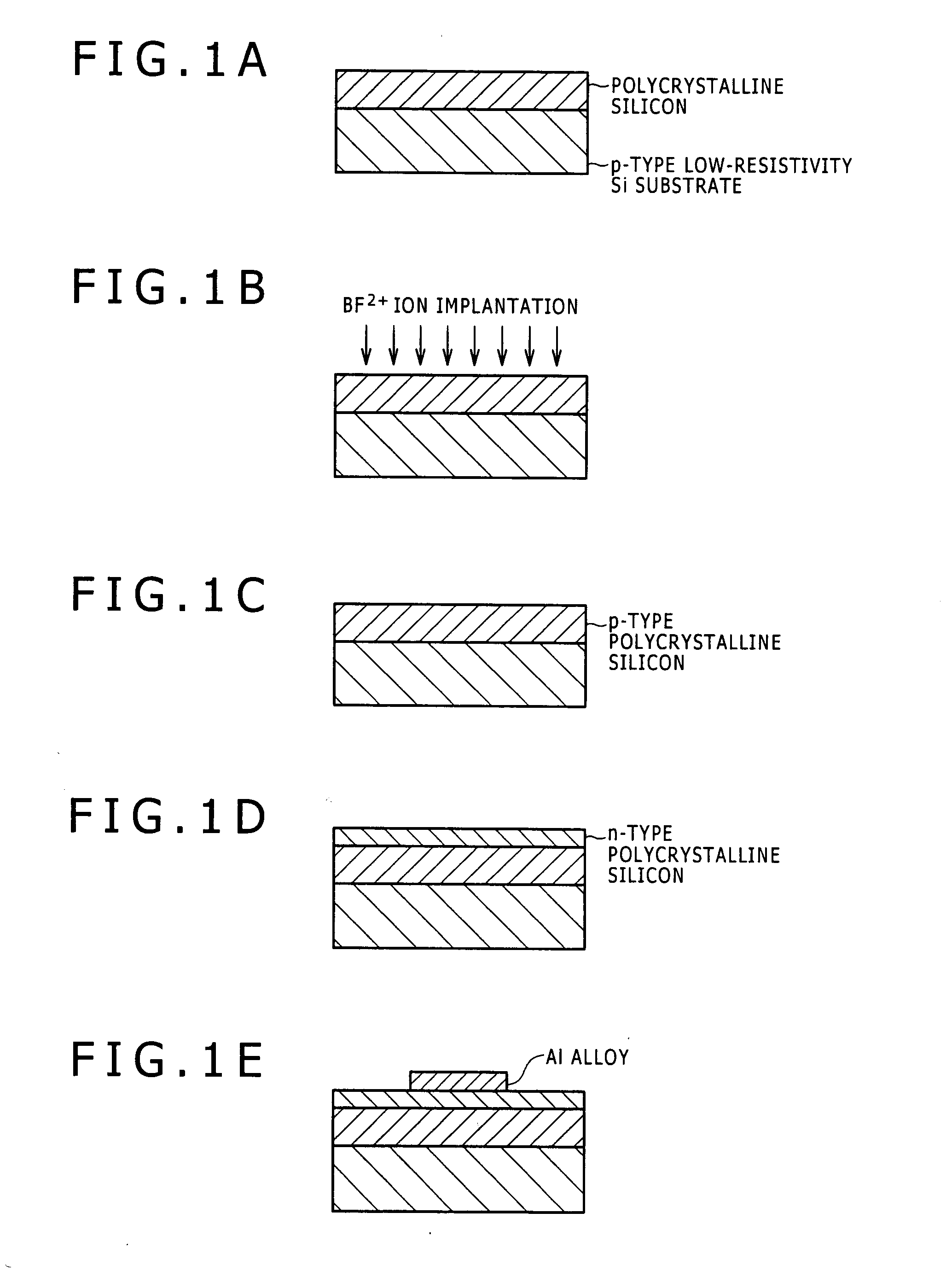

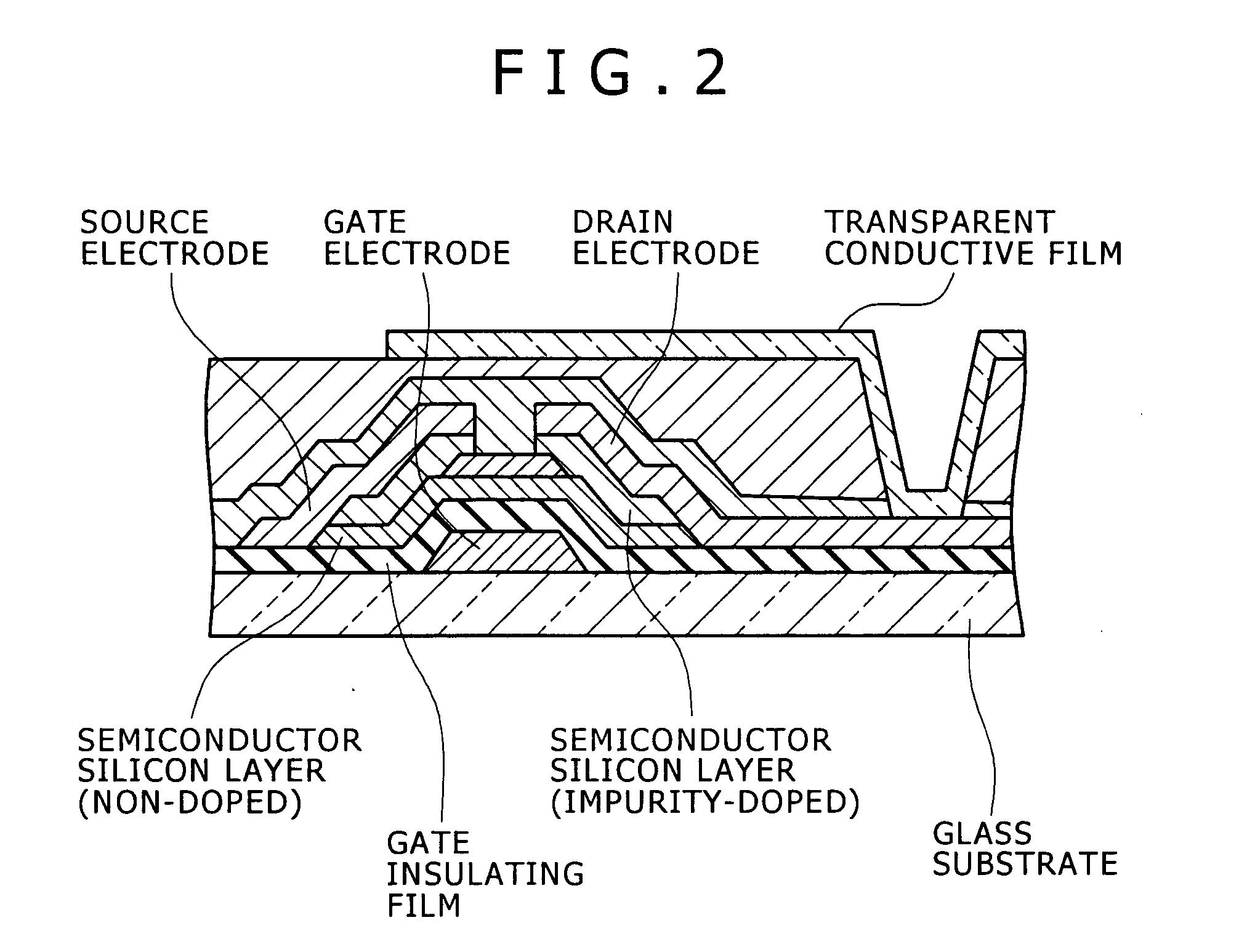

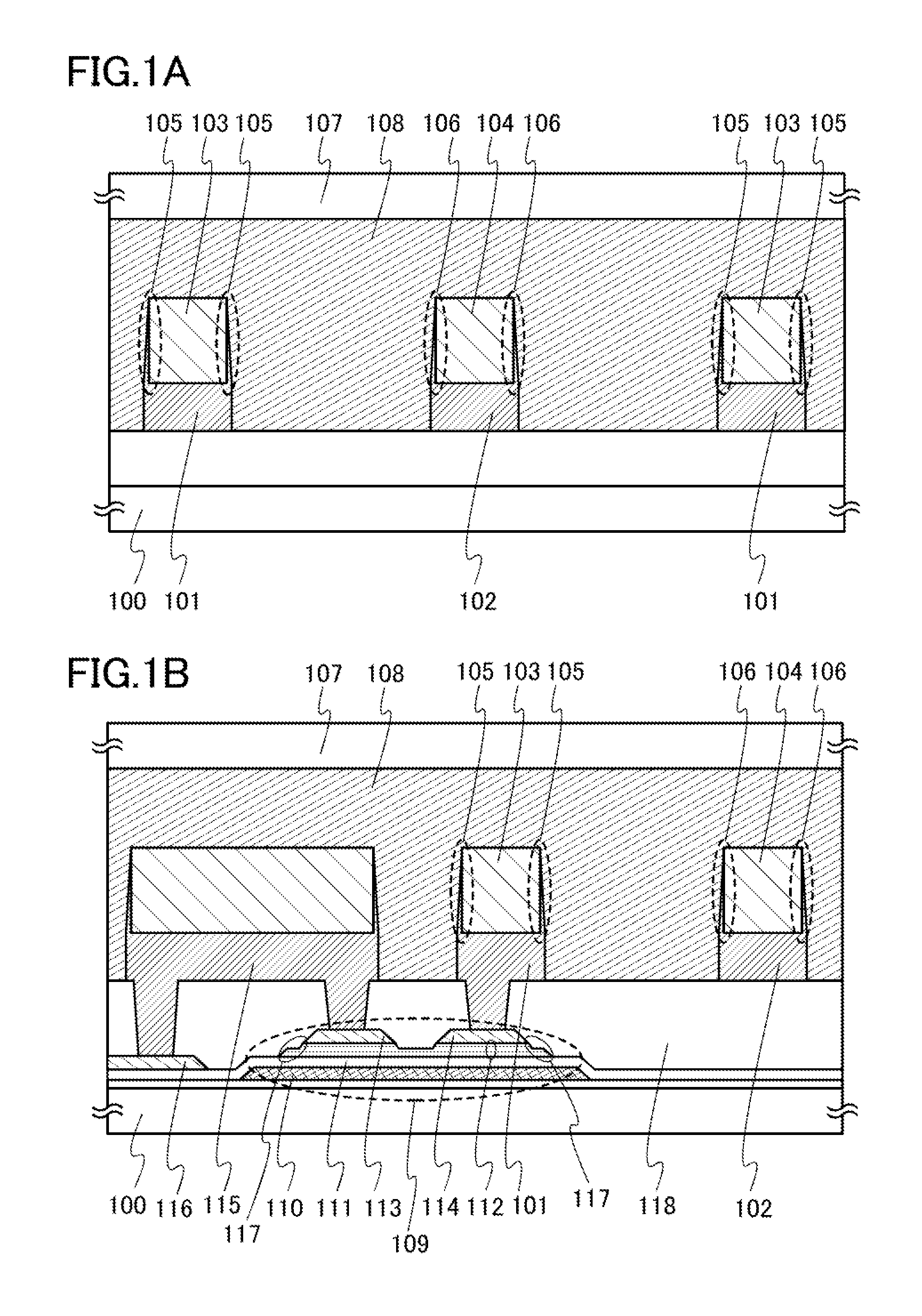

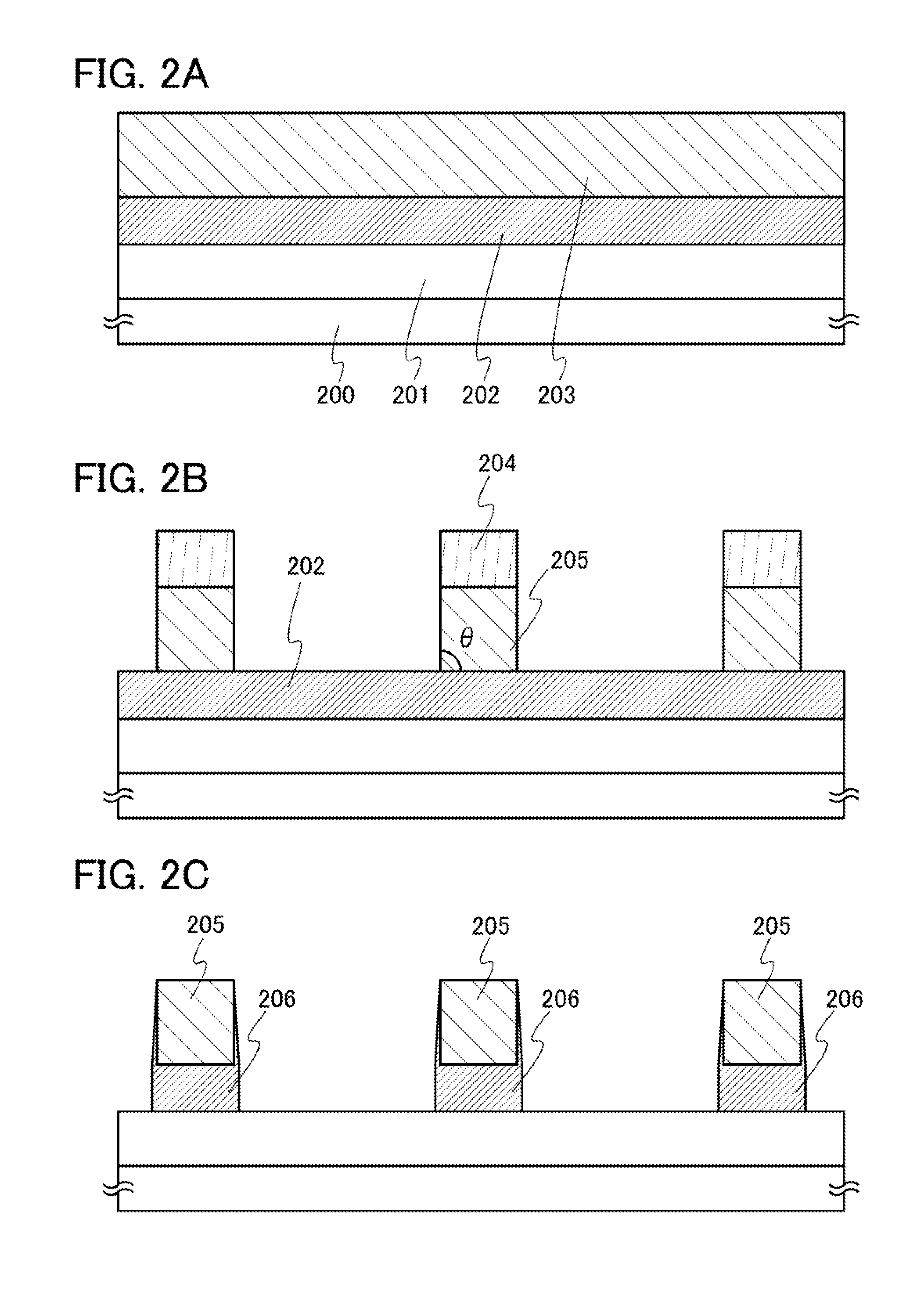

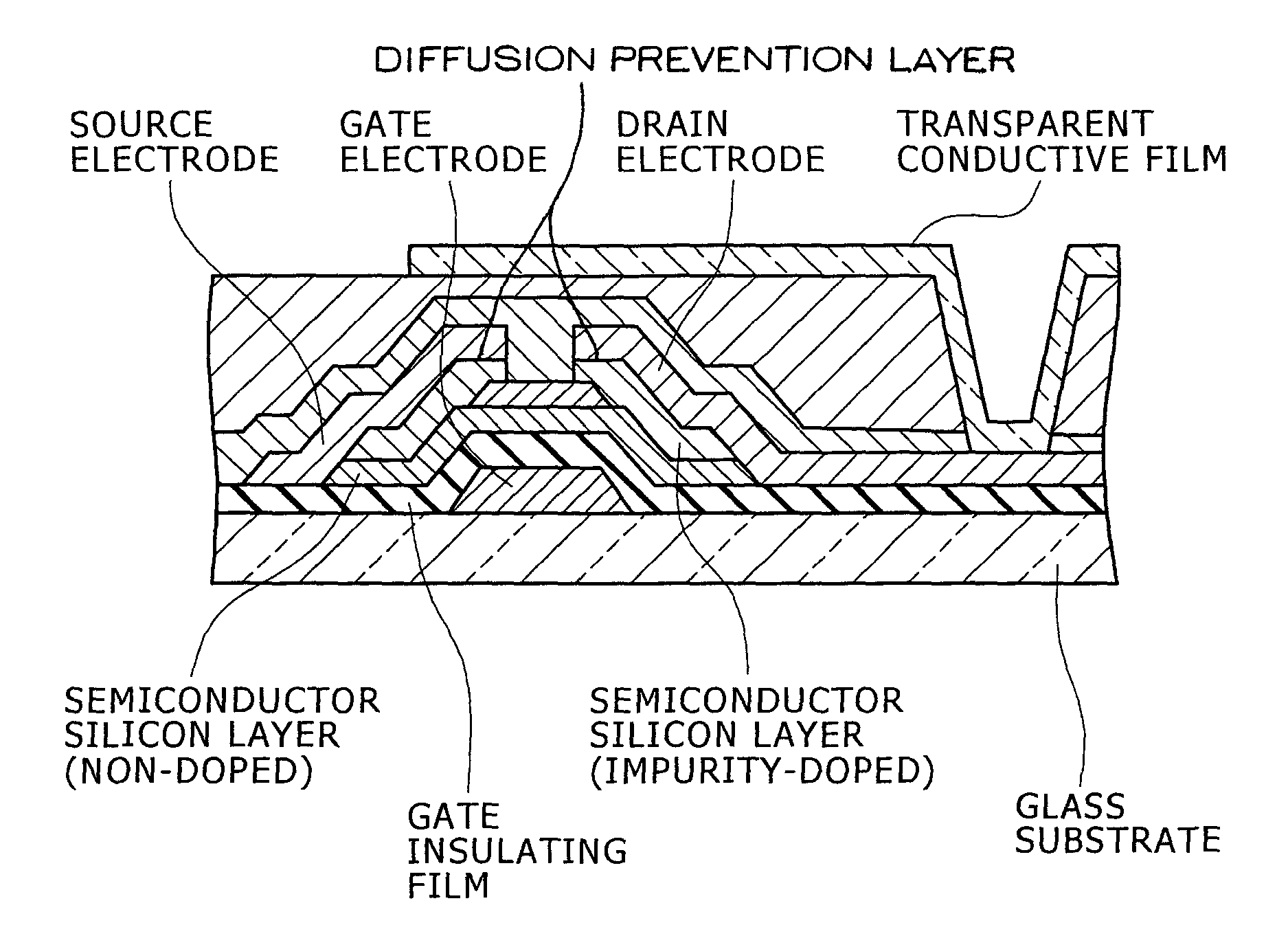

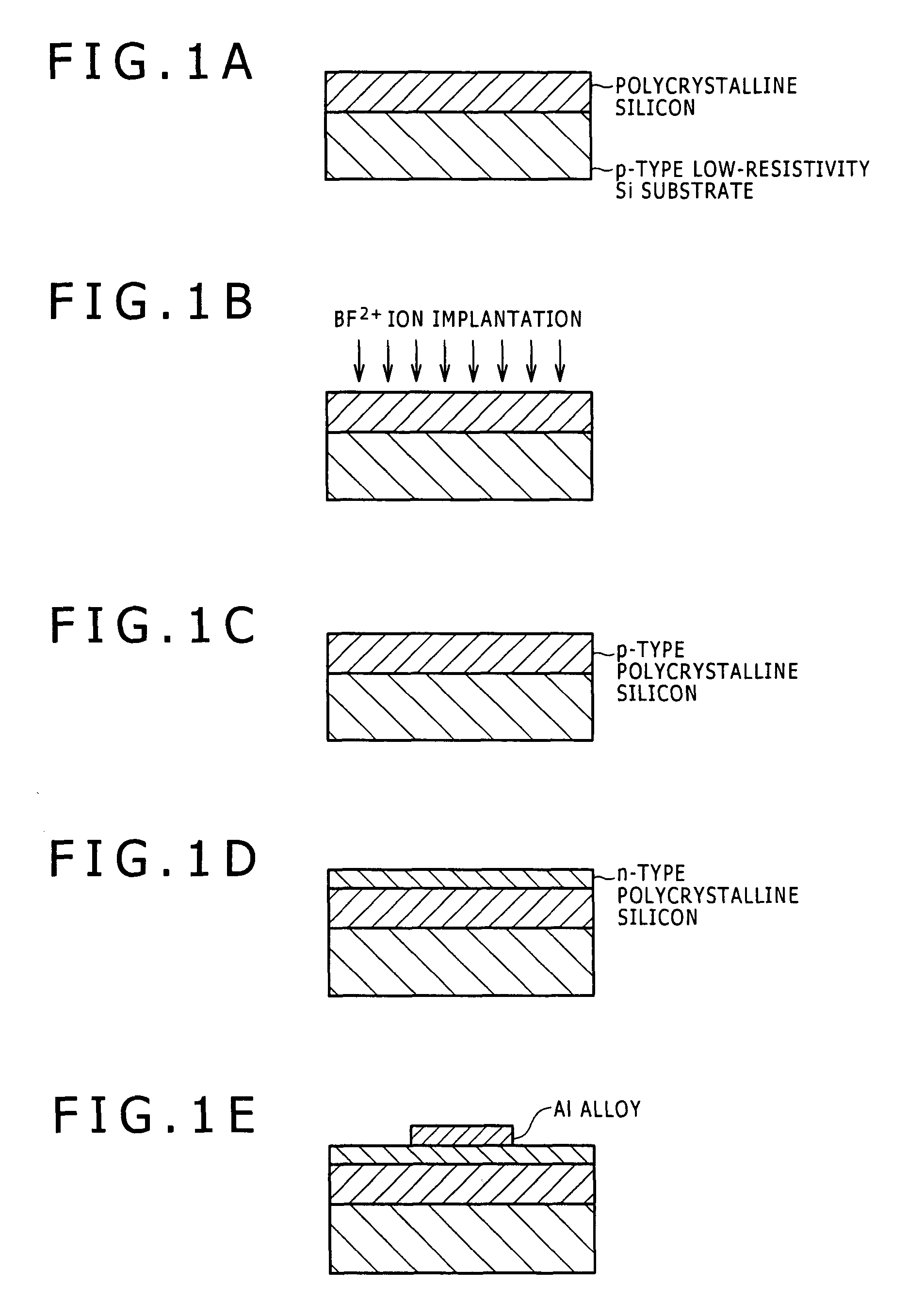

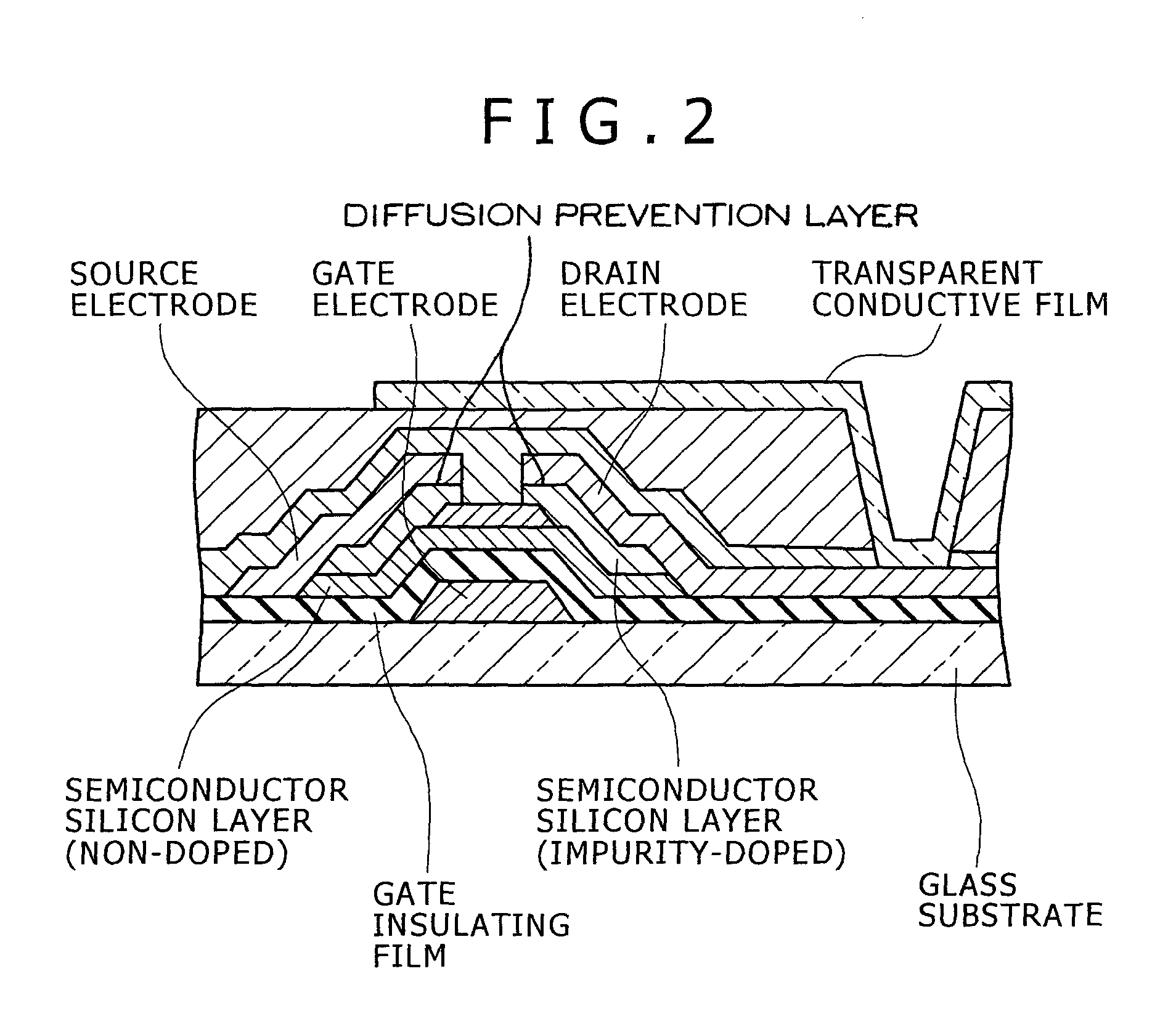

Thin film transistor substrate and display device

InactiveUS20070278497A1Reduce adverse effectsDesired switching performanceSemiconductor/solid-state device detailsSolid-state devicesDisplay deviceAlloy thin film

Disclosed are a thin film transistor substrate where barrier metal can be omitted to be formed between a semiconductor layer of a thin film transistor and source and drain electrodes (barrier metal need not be formed between the semiconductor layer of the thin film transistor and the source and drain electrodes), and a display device. (1) A thin film transistor substrate has a semiconductor layer of a thin film transistor, a source electrode, a drain electrode, and a transparent conductive film, wherein the substrate has a structure in which the source and drain electrodes are directly connected to the semiconductor layer of the thin film transistor, and the source and drain electrodes include an Al alloy thin film containing Ni of 0.1 to 6.0 atomic percent, La of 0.1 to 1.0 atomic percent, and Si of 0.1 to 1.5 atomic percent. (2) A display device has the thin film transistor substrate.

Owner:KOBE STEEL LTD

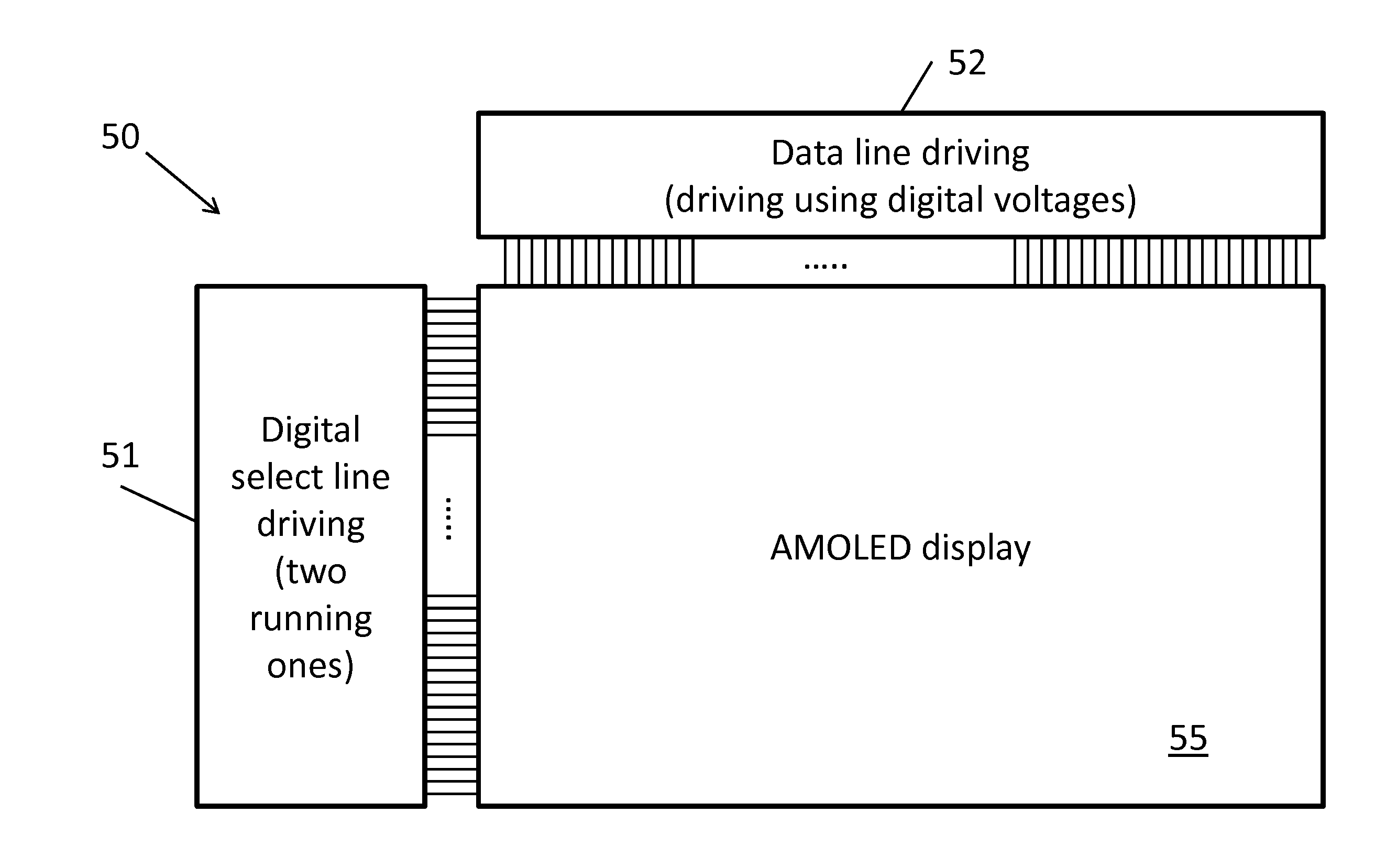

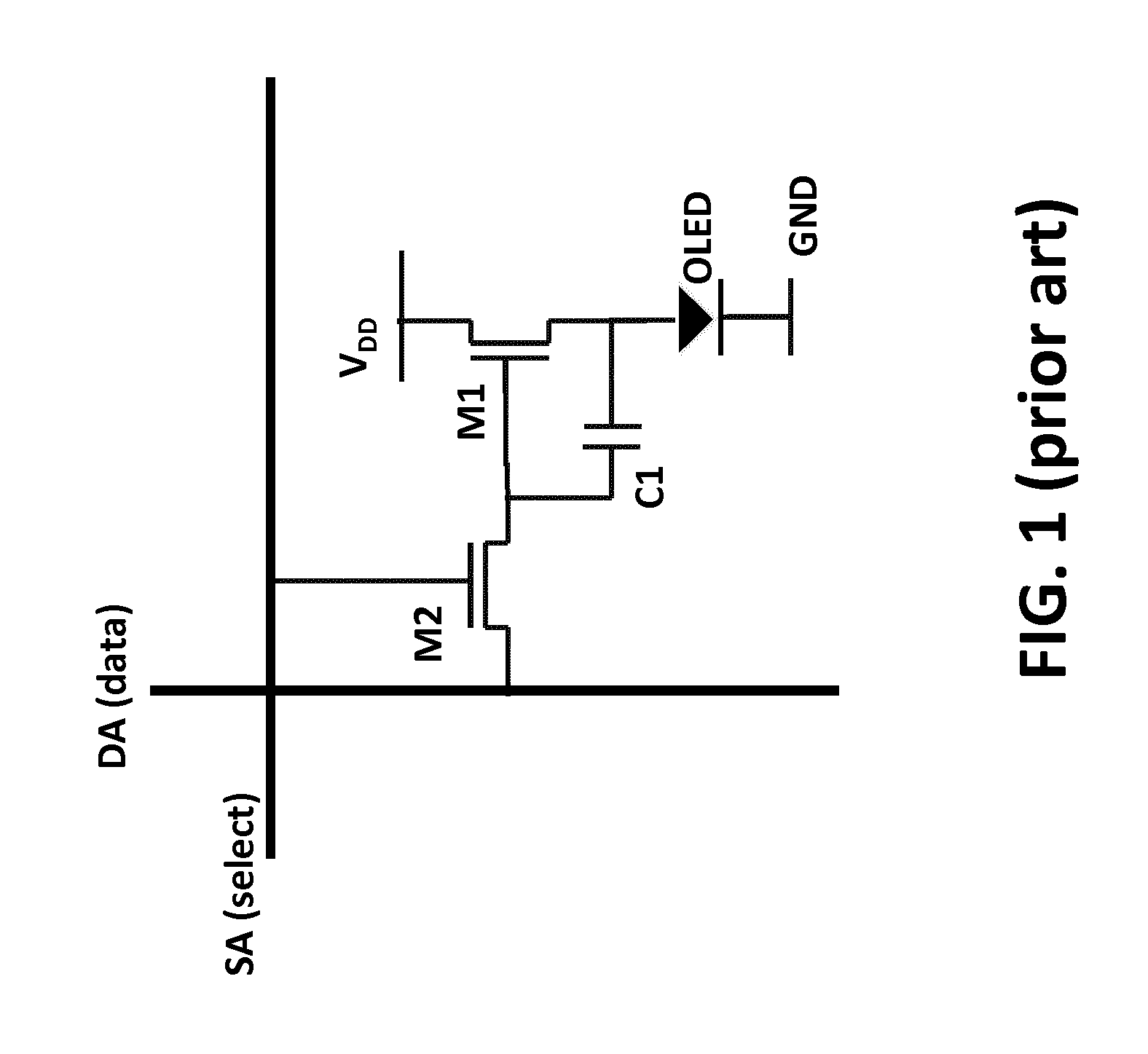

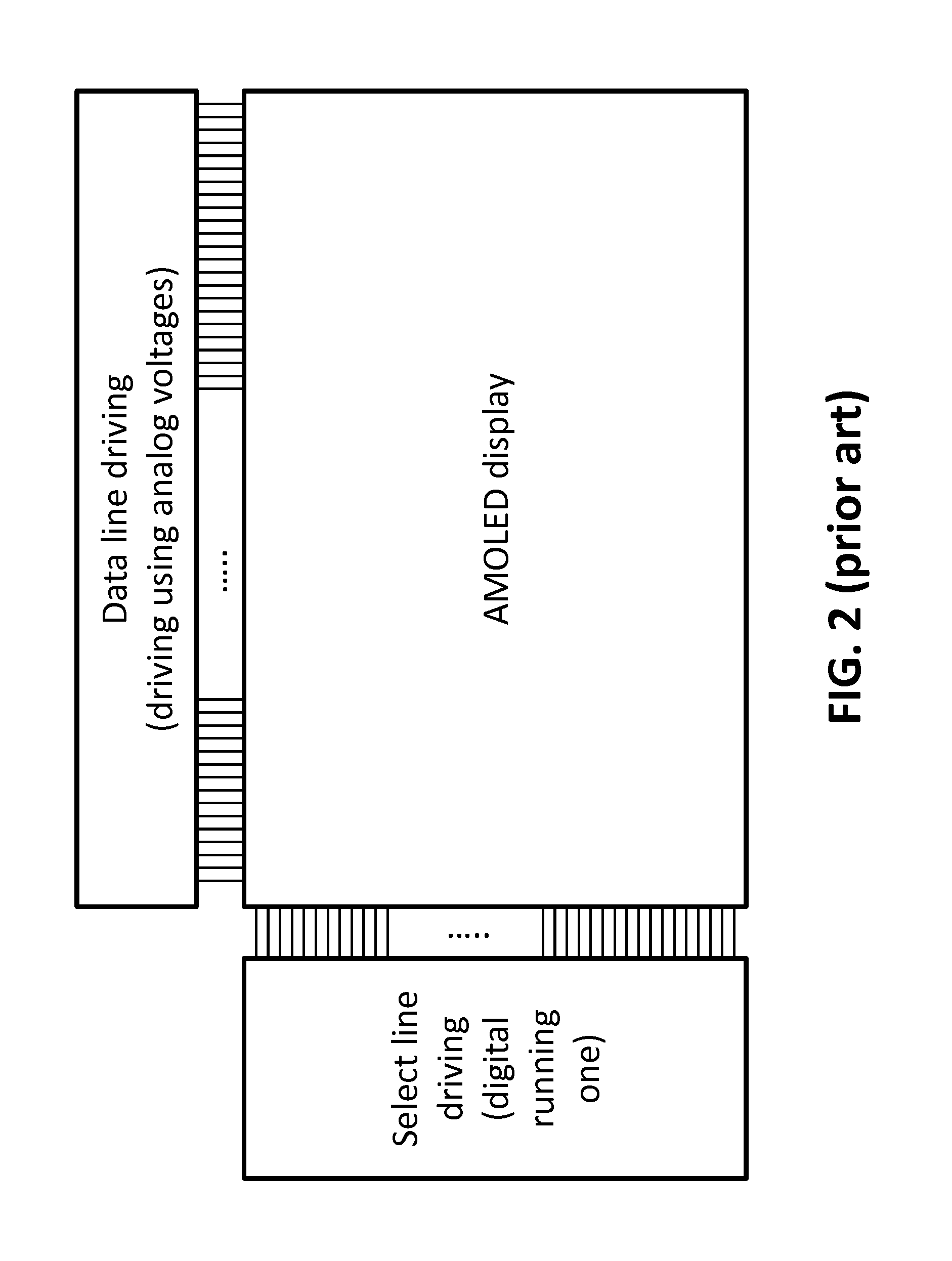

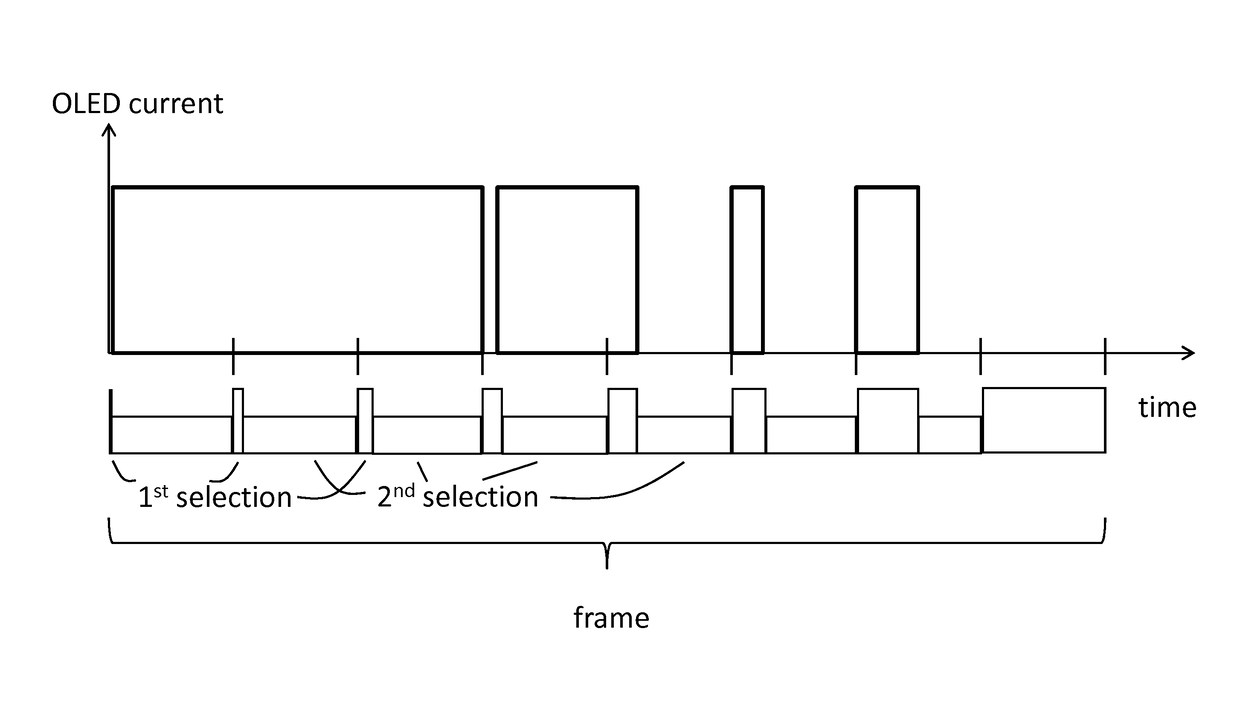

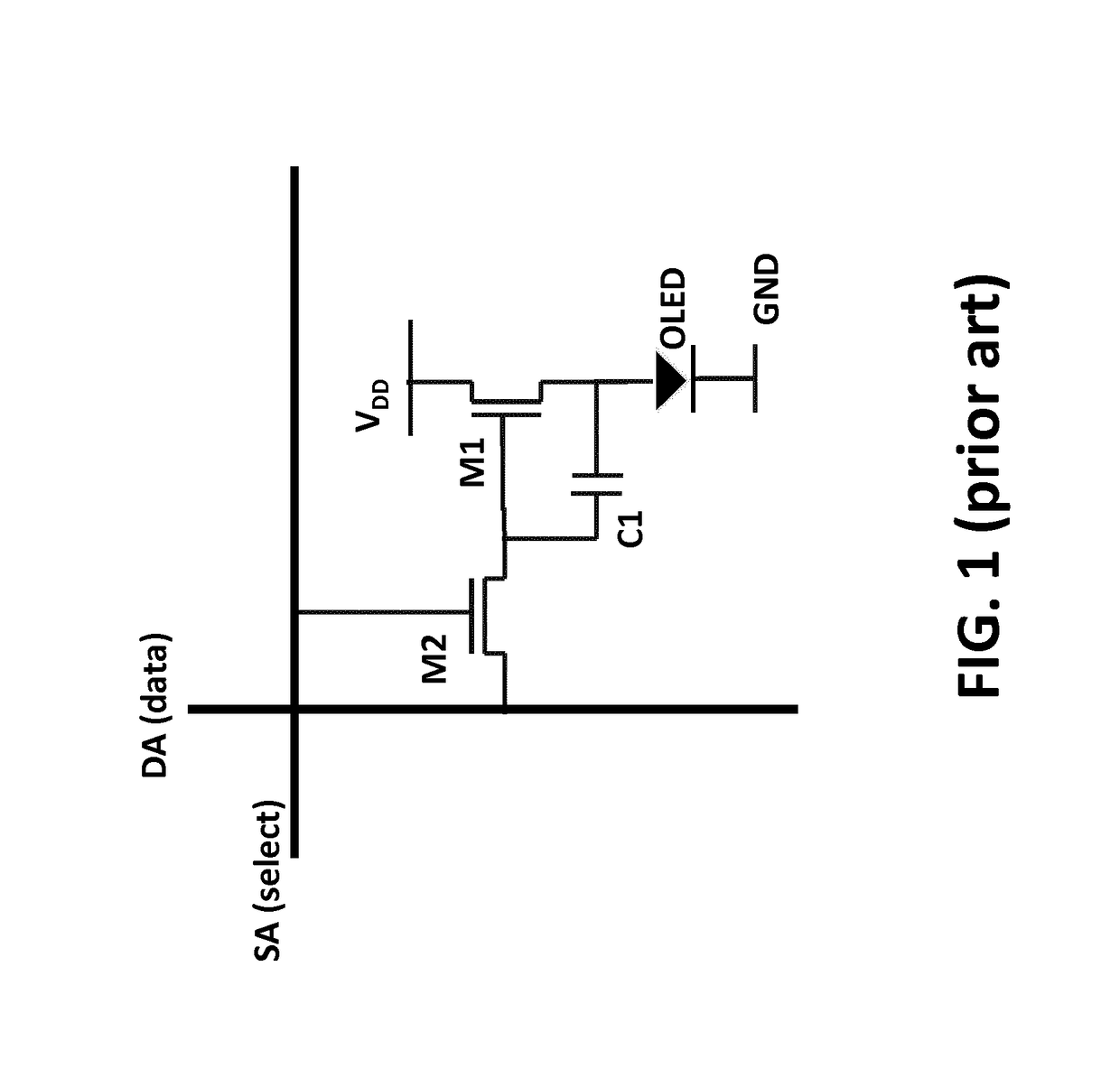

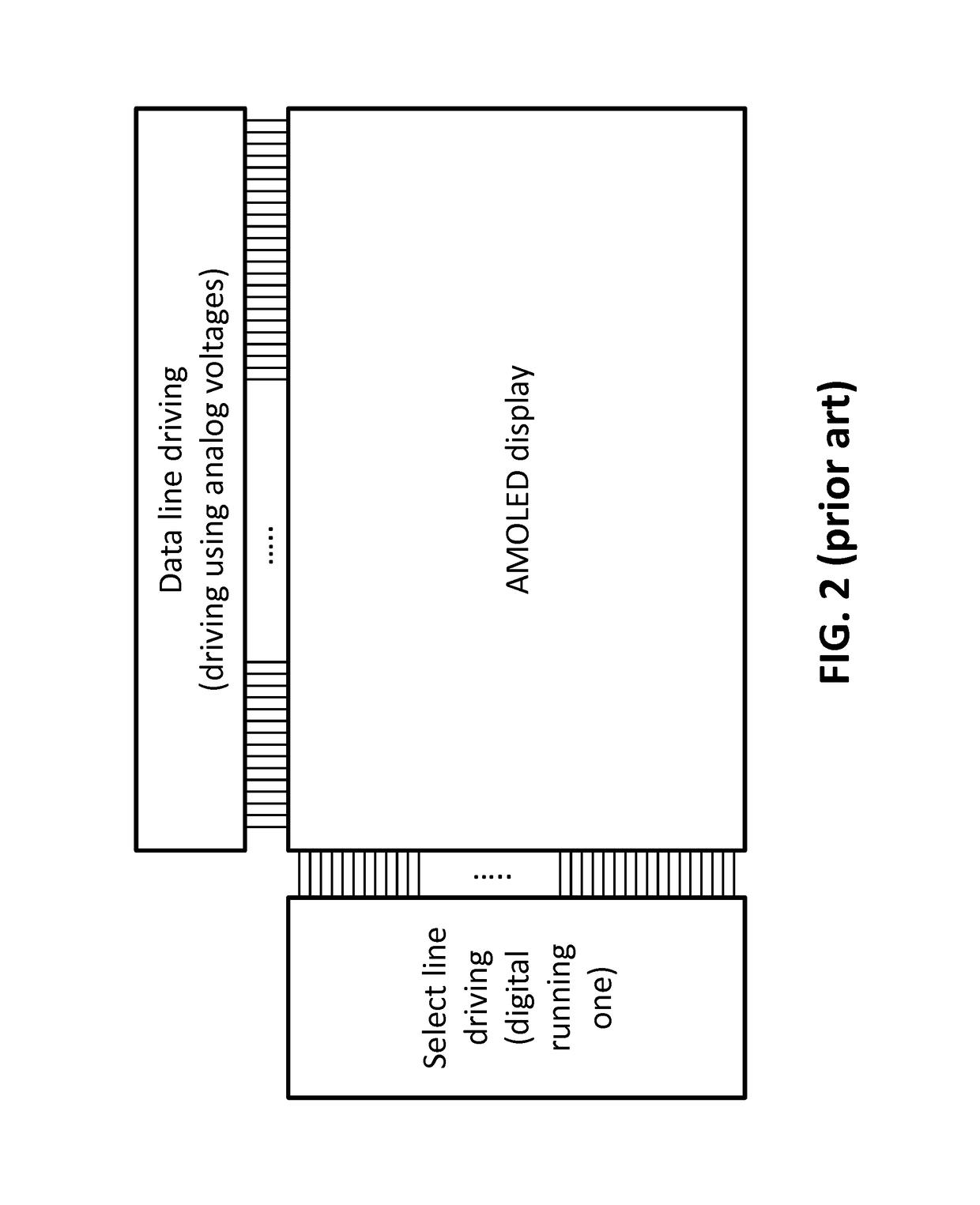

Digital Driving of Active Matrix Displays

ActiveUS20150302795A1Simple methodLess complexCathode-ray tube indicatorsNon-linear opticsActive matrixDisplay device

A method for digital driving of an active matrix display with a predetermined frame rate is described. The display contains a plurality of pixels organized in a plurality of rows and a plurality of columns. The method includes representing each of the plurality of pixels of an image to be displayed within a frame by an n-bit digital image code. The method also includes dividing the image frame into sub-frames, which may be of substantially equal duration. Within each sub-frame, the method includes sequentially selecting at least one of the plurality of rows twice. Upon a first selection, a first digital code is written to the selected row and upon a second selection a second digital code is written to the selected row. There is a predetermined time delay between the second selection and the first selection. Digital driving circuitry is also described.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

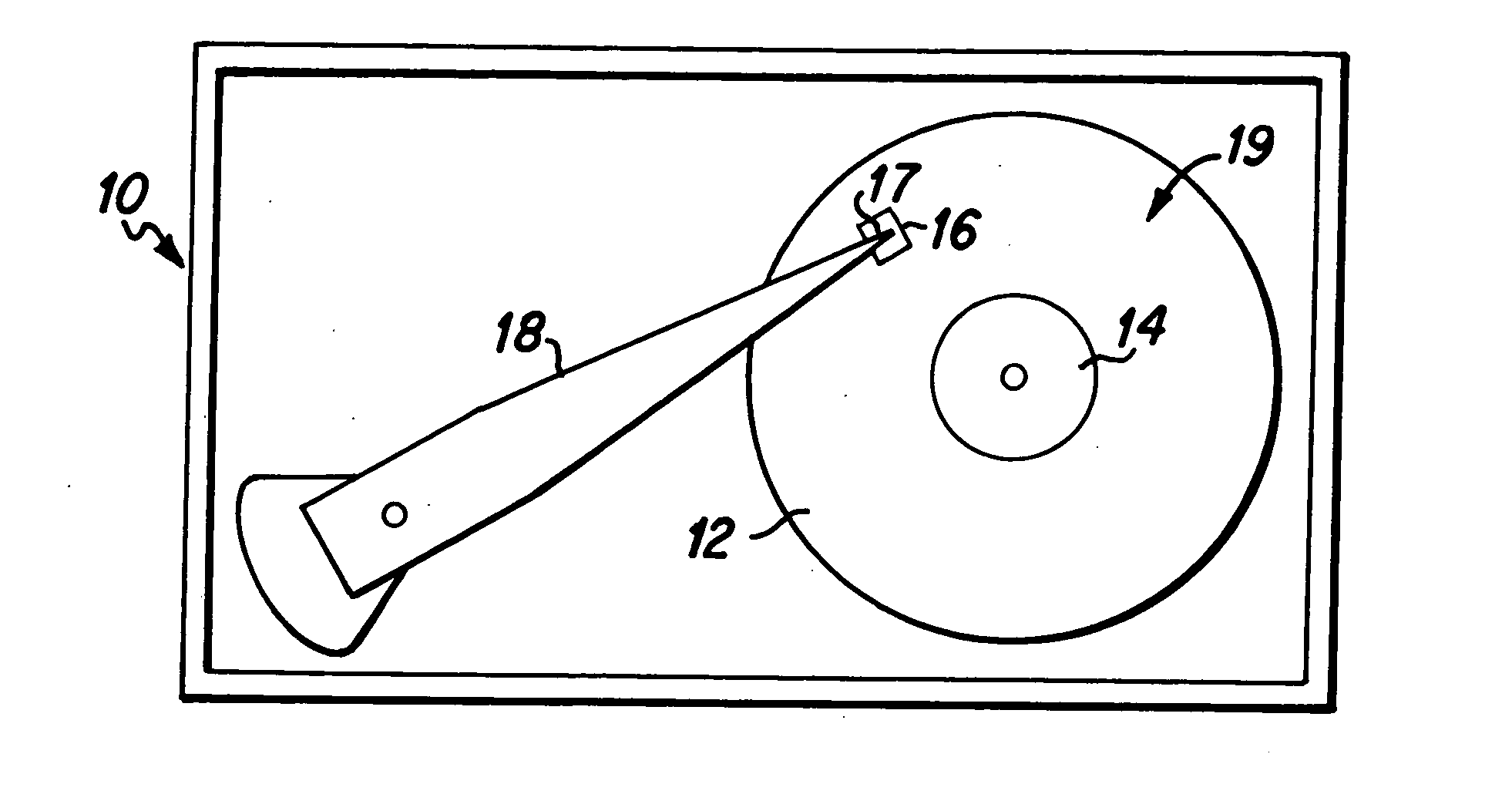

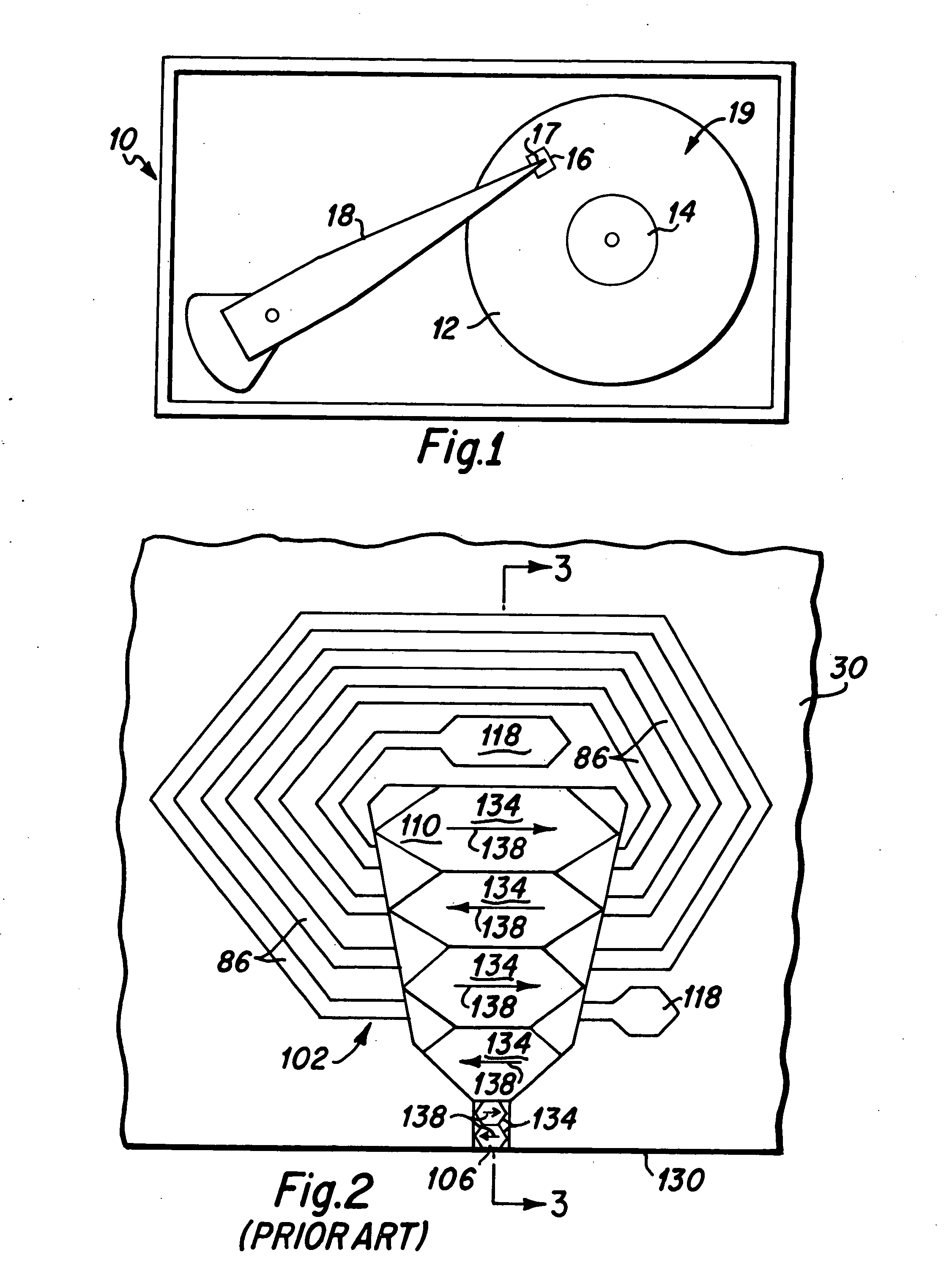

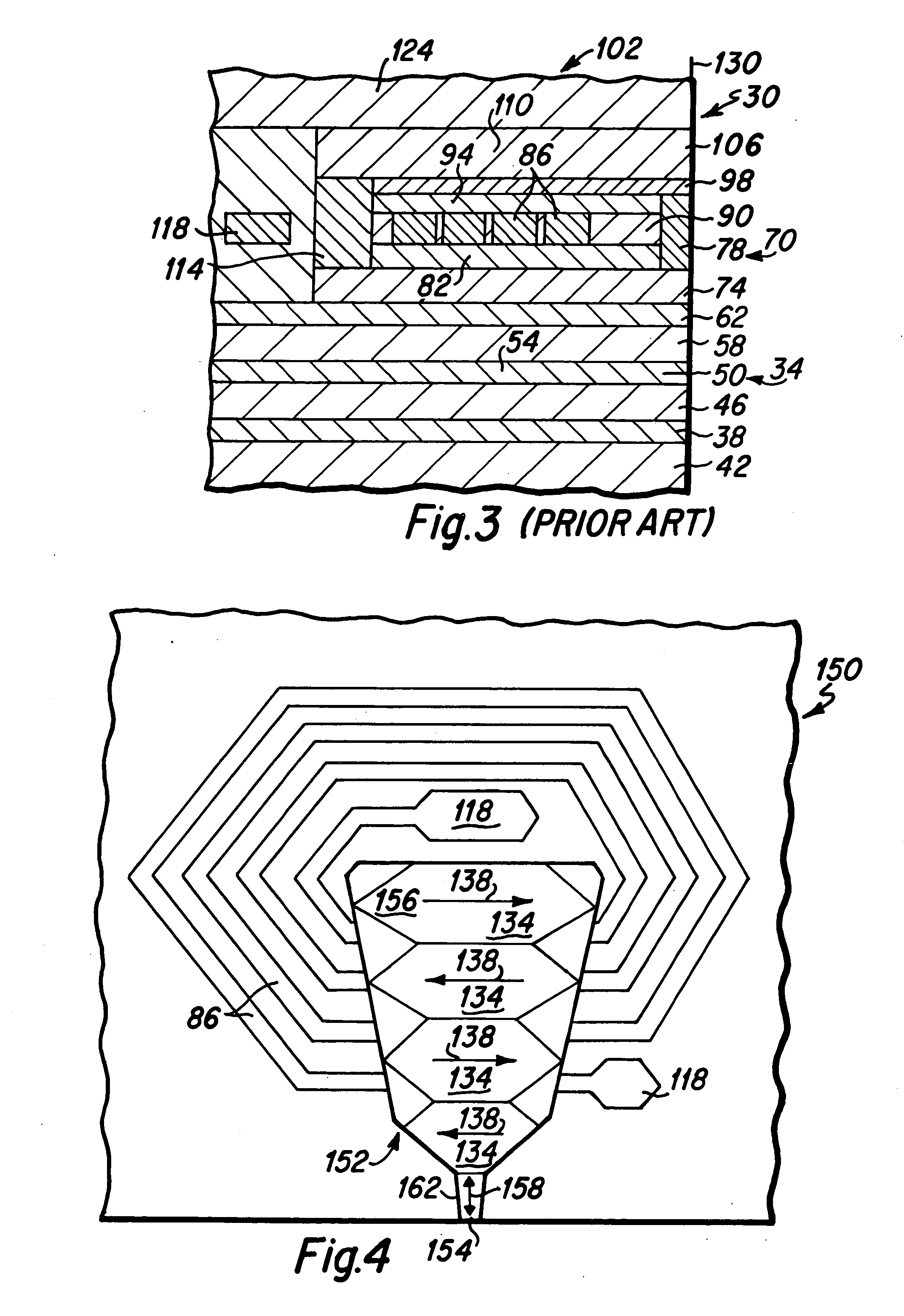

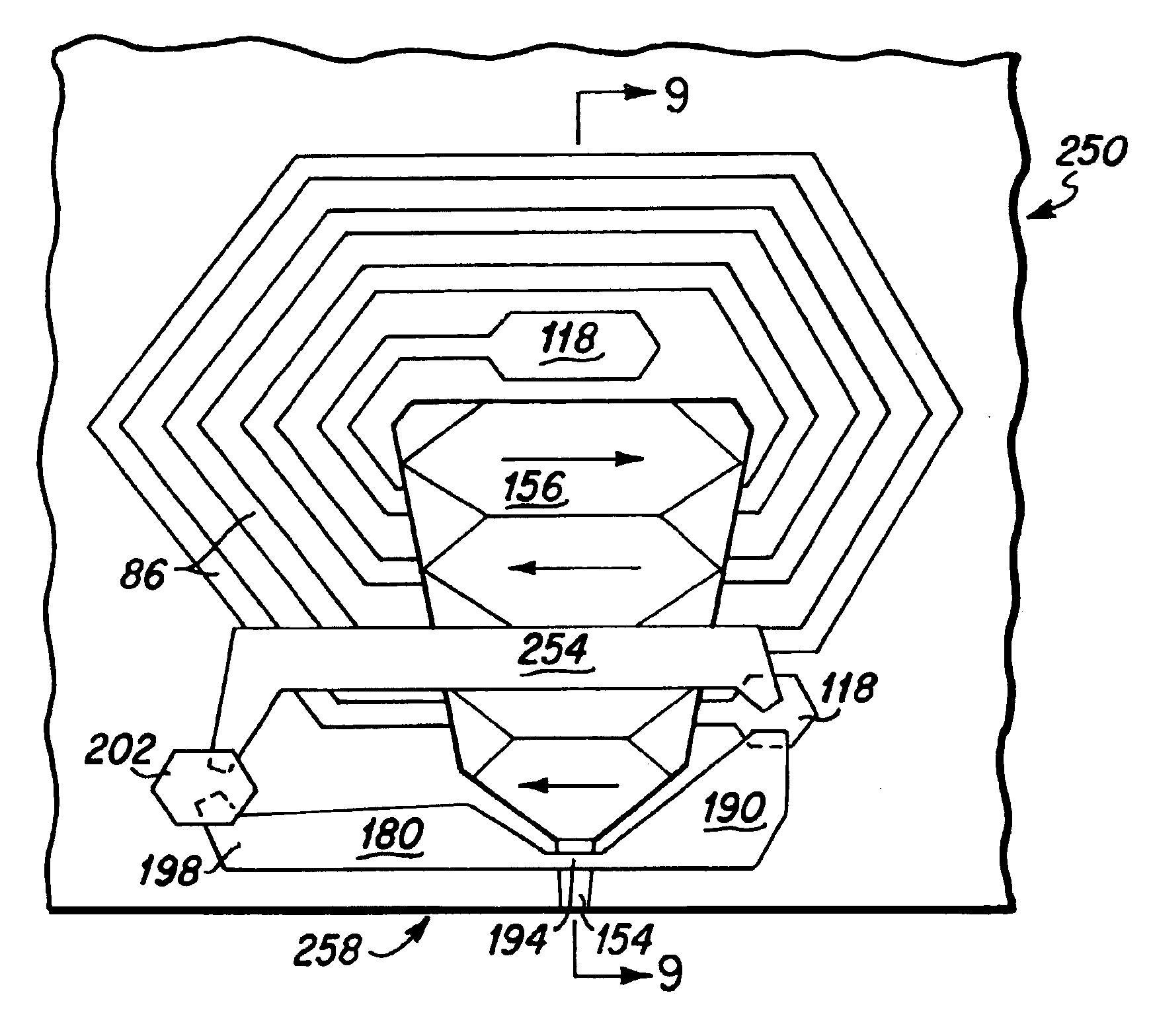

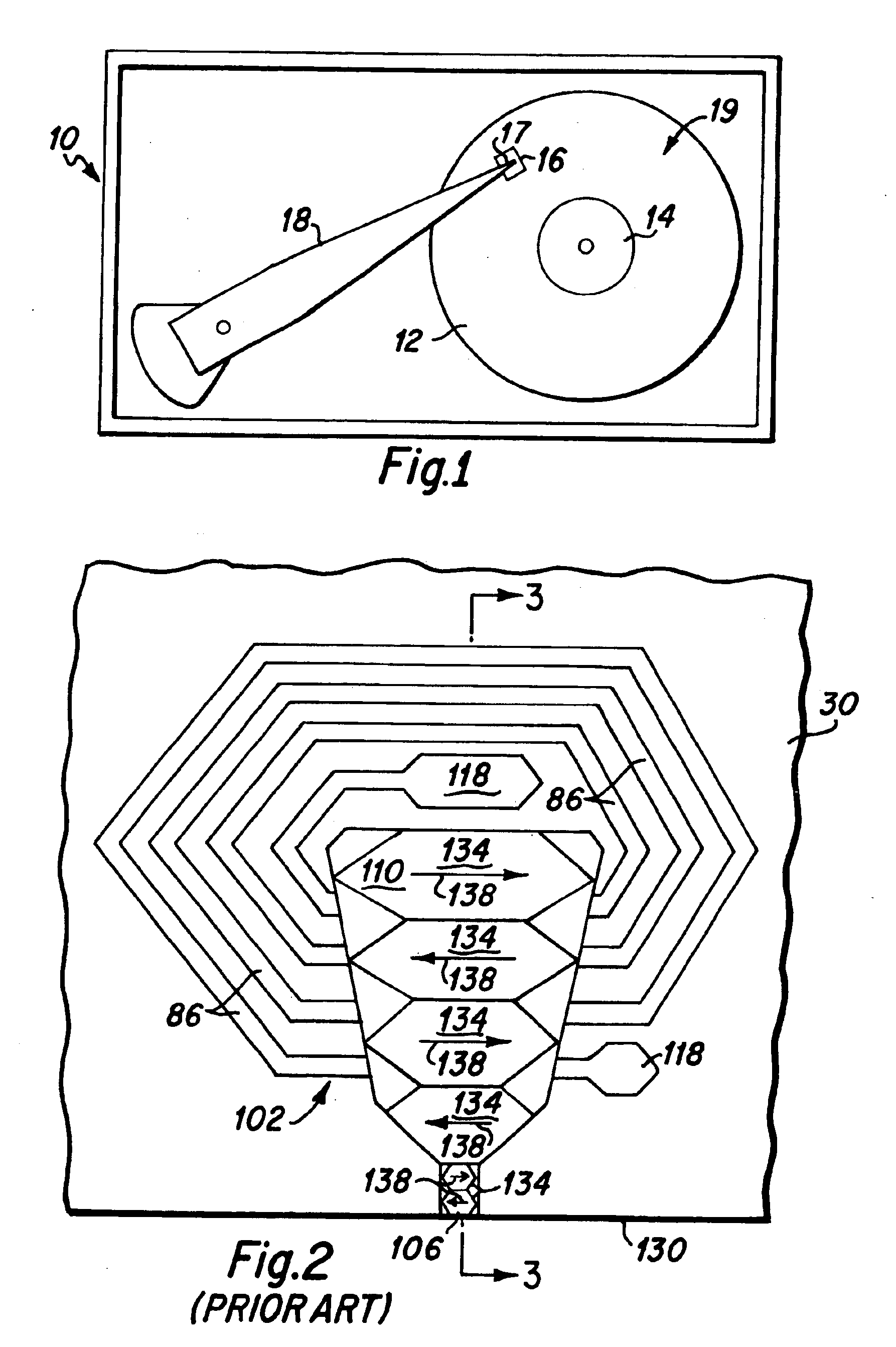

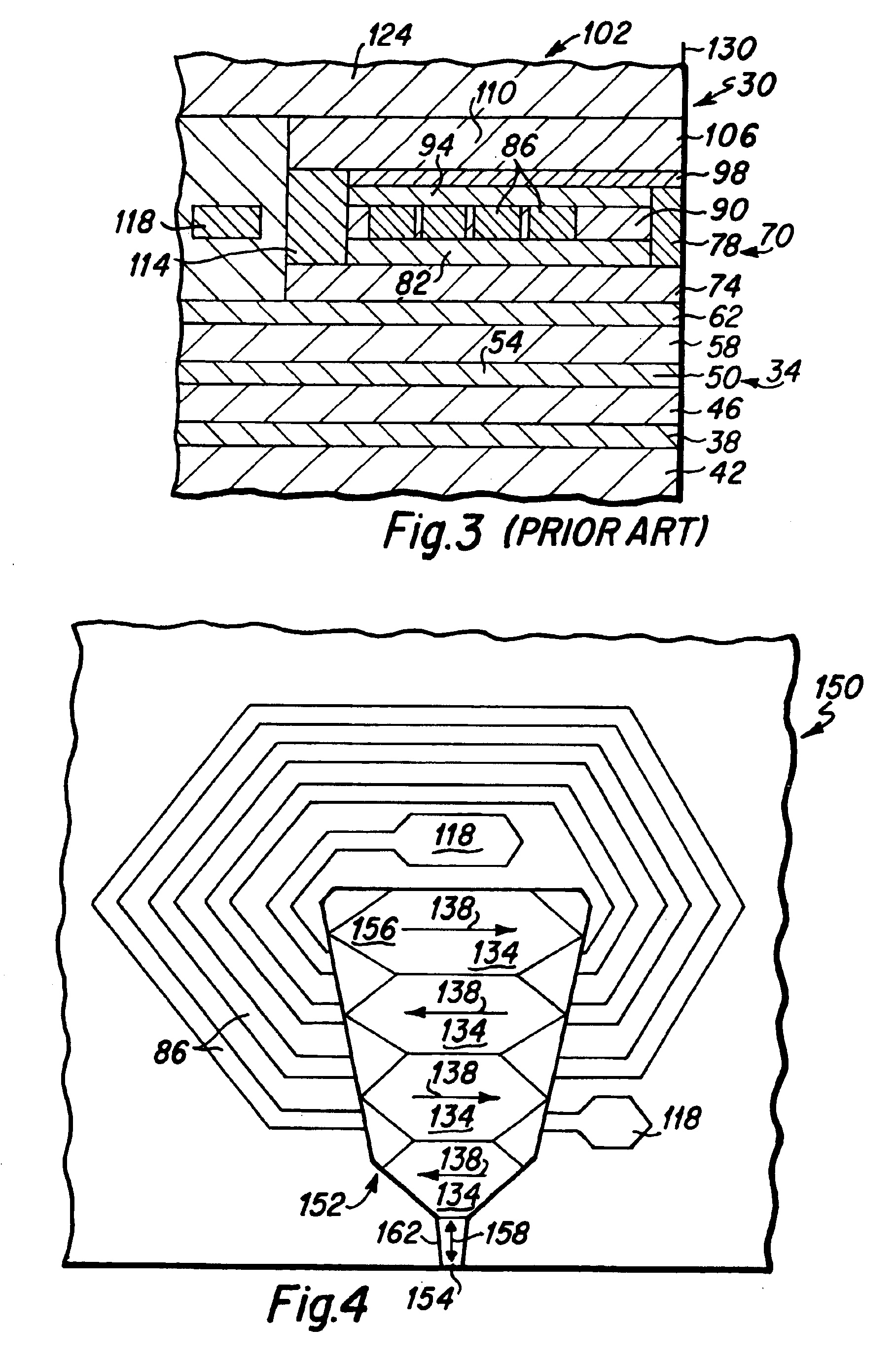

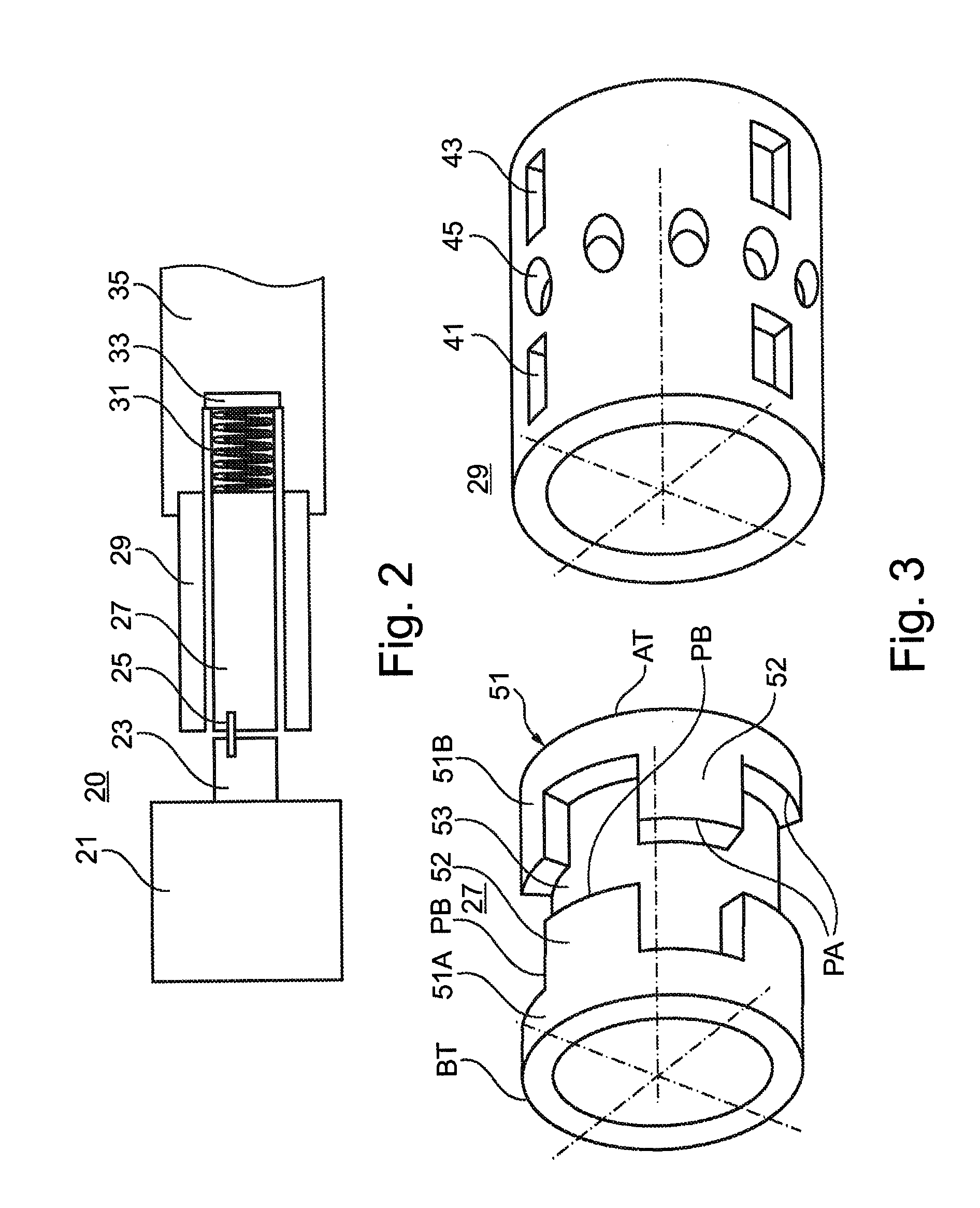

Localized pole tip heating device for magnetic head for hard disk drive

ActiveUS20050018347A1Reduce switching speedReduce pole tip stressConstruction of head windingsHeads using thin filmsHard disc driveMagnetization

The magnetic head is formed with a narrow pole tip, and a pole tip heating element is fabricated to reduce the pole tip stress and increase its permeability, such that the magnetization switching speed of the pole tip is increased. The heating element is preferably electrically interconnected within the induction coil circuit of the magnetic head, such that the electrical current flowing through the induction coil also flows through the heating element. In a preferred embodiment, the heating element is fabricated above the second magnetic pole. The heating element is preferably formed with a resistance of approximately 0.2 to 1.0 ohms, such that the approximately 40 mA current that flows through the induction coil and the heating element creates a heating energy of the heating element of approximately 0.3 to 1.6 mW. The heating element can be comprised of a variety of materials such as Cu, W, NiFe, NiCr and IrRh.

Owner:WESTERN DIGITAL TECH INC

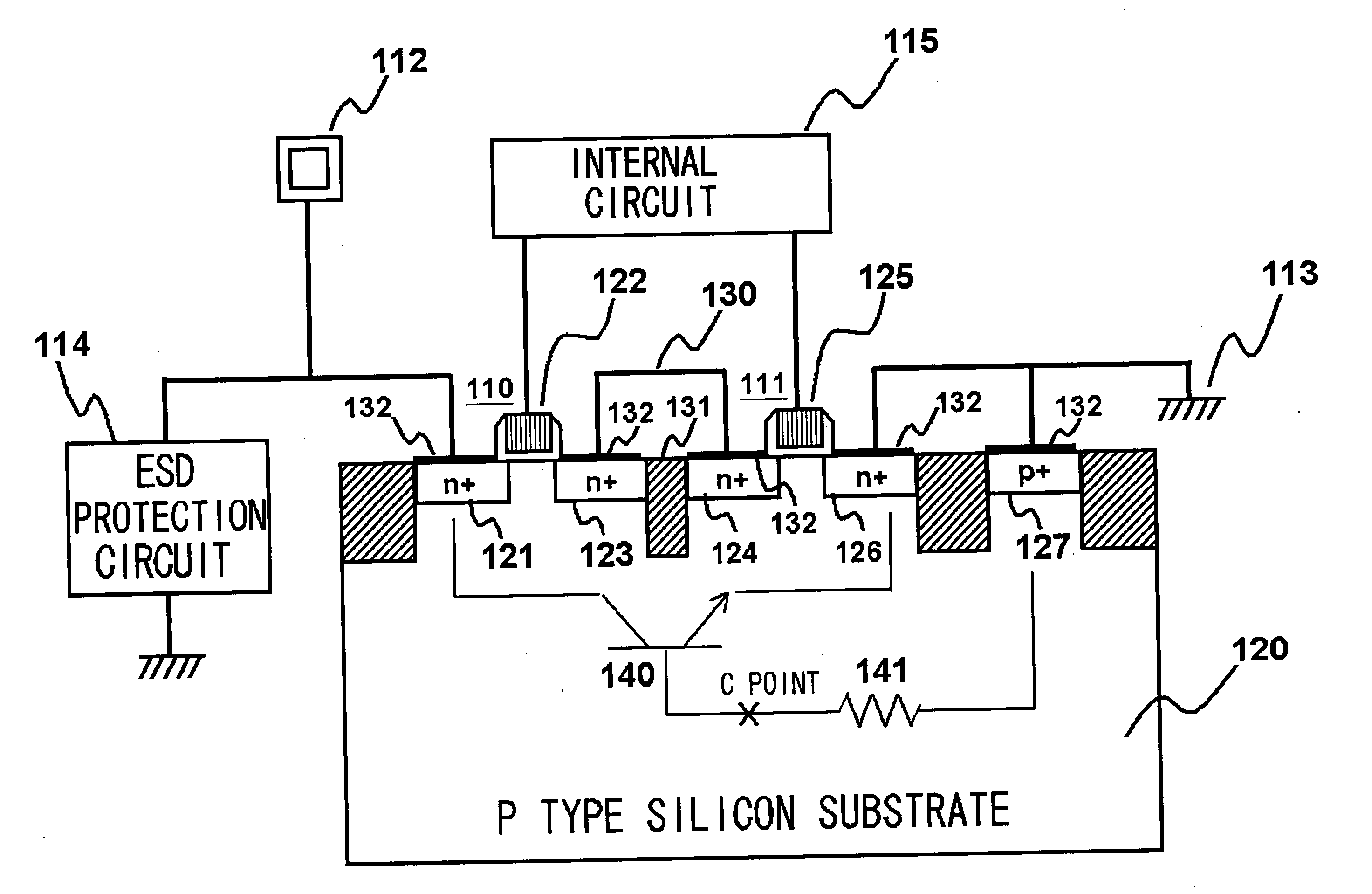

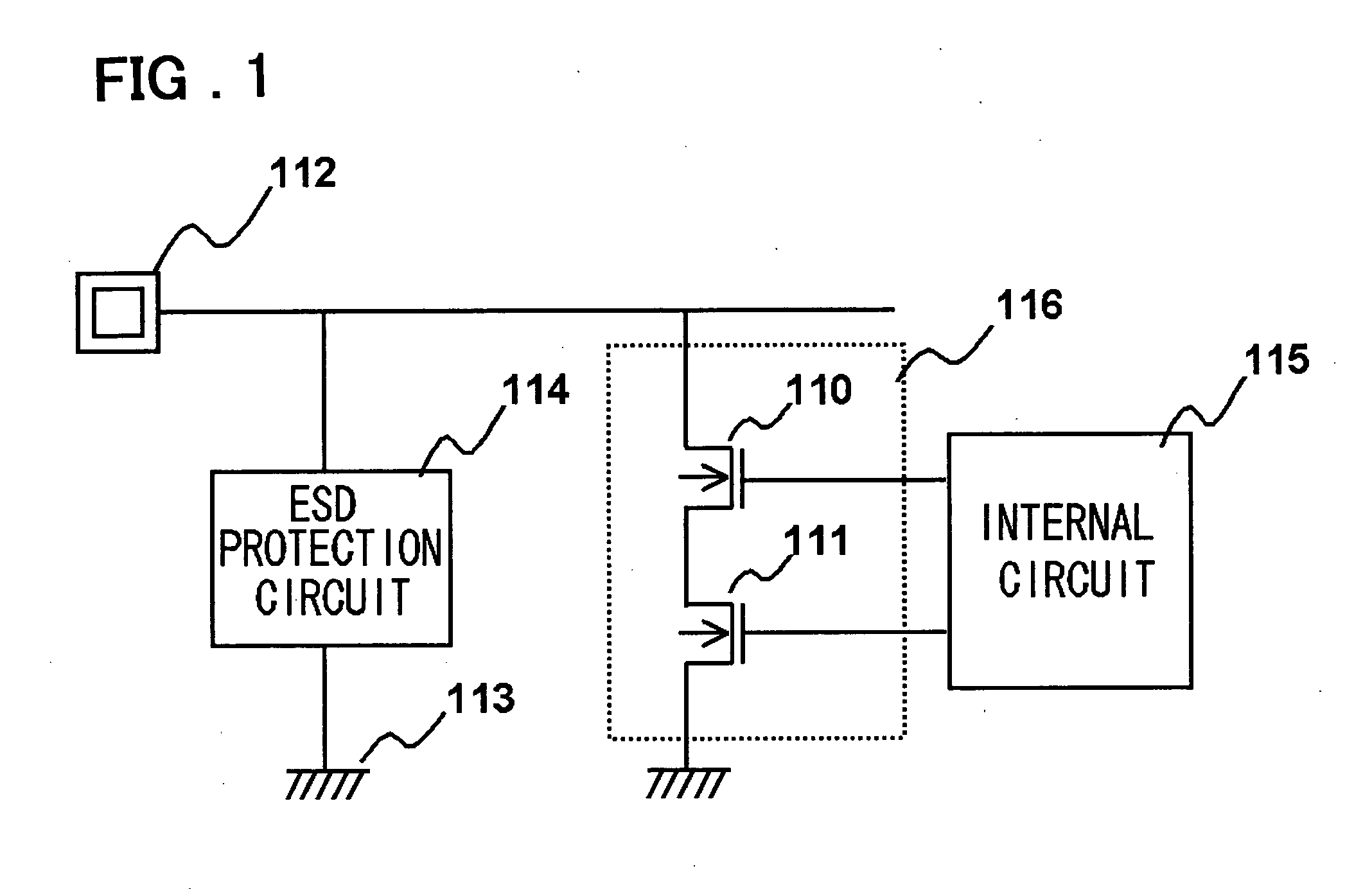

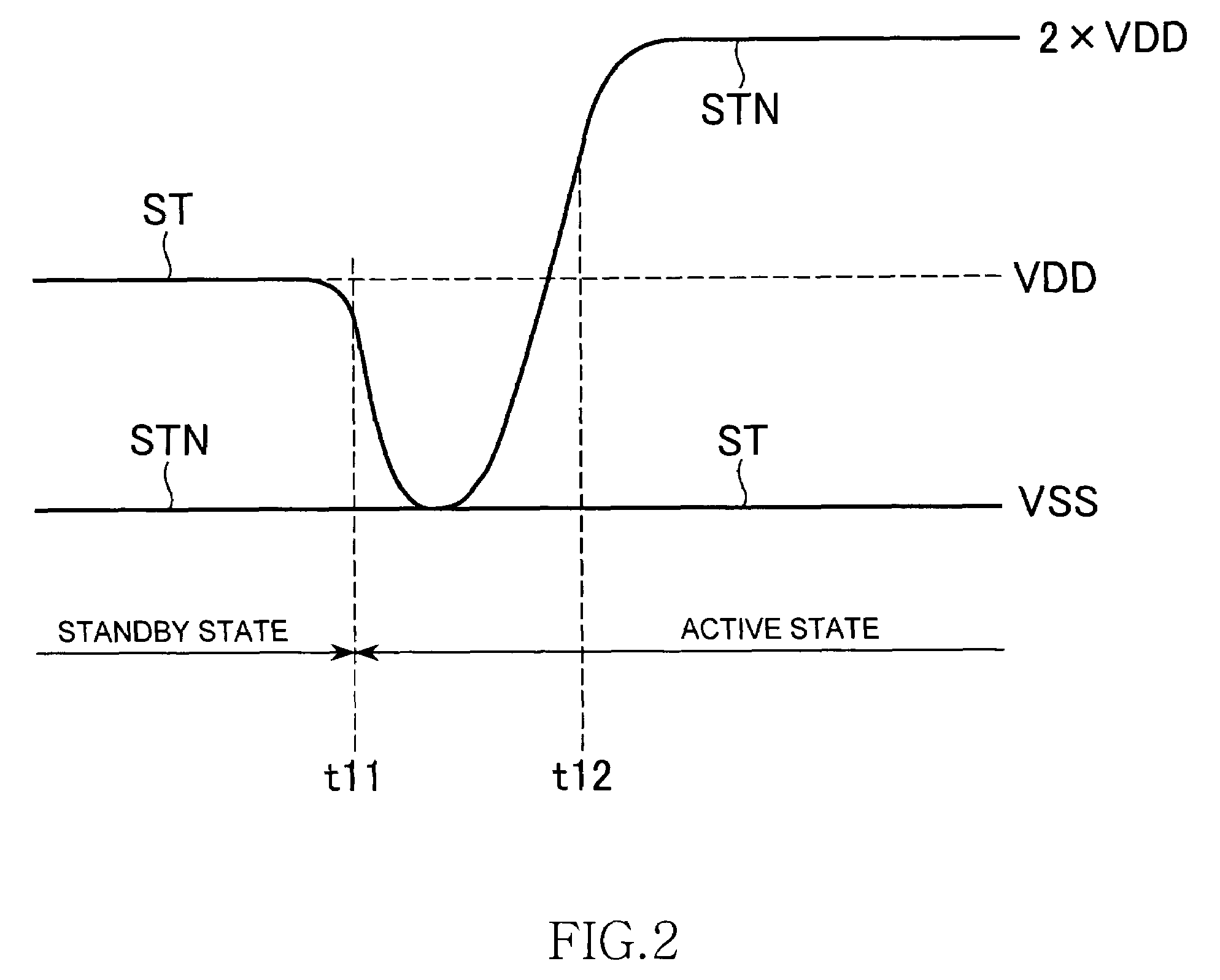

Semiconductor integrated circuit

InactiveUS20050017306A1Prevent speedingSpeedTransistorSemiconductor/solid-state device detailsElectrical resistance and conductanceParasitic capacitance

To provide an output circuit having a low parasitic capacitance and resistance in the drains of output transistors, which is operable at a high speed and its ESD performance is improved. A devoted electrostatic discharge protection circuit is provided between the output terminal (pin) and the ground terminal (or power supply terminal). An output circuit which is in parallel connected to this electrostatic discharge protection circuit comprises a first and second MOS transistors which are cascade-connected to each other. The entire area of the source / drain regions of the first and second MOS transistors are silicided. Both transistors have their gate electrodes which are connected to an internal circuit. The source doped region of the first MOS transistor is separated from the drain doped region of the second MOS transistor and they are connected to each other by metal wiring.

Owner:NEC ELECTRONICS CORP

Localized pole tip heating device for magnetic head for hard disk drive

ActiveUS7023660B2Reduce switching speedReduce rateConstruction of head windingsHeads using thin filmsHard disc driveElectricity

The magnetic head is formed with a narrow pole tip, and a pole tip heating element is fabricated to reduce the pole tip stress and increase its permeability, such that the magnetization switching speed of the pole tip is increased. The heating element is preferably electrically interconnected within the induction coil circuit of the magnetic head, such that the electrical current flowing through the induction coil also flows through the heating element. In a preferred embodiment, the heating element is fabricated above the second magnetic pole. The heating element is preferably formed with a resistance of approximately 0.2 to 1.0 ohms, such that the approximately 40 mA current that flows through the induction coil and the heating element creates a heating energy of the heating element of approximately 0.3 to 1.6 mW. The heating element can be comprised of a variety of materials such as Cu, W, NiFe, NiCr and IrRh.

Owner:WESTERN DIGITAL TECH INC

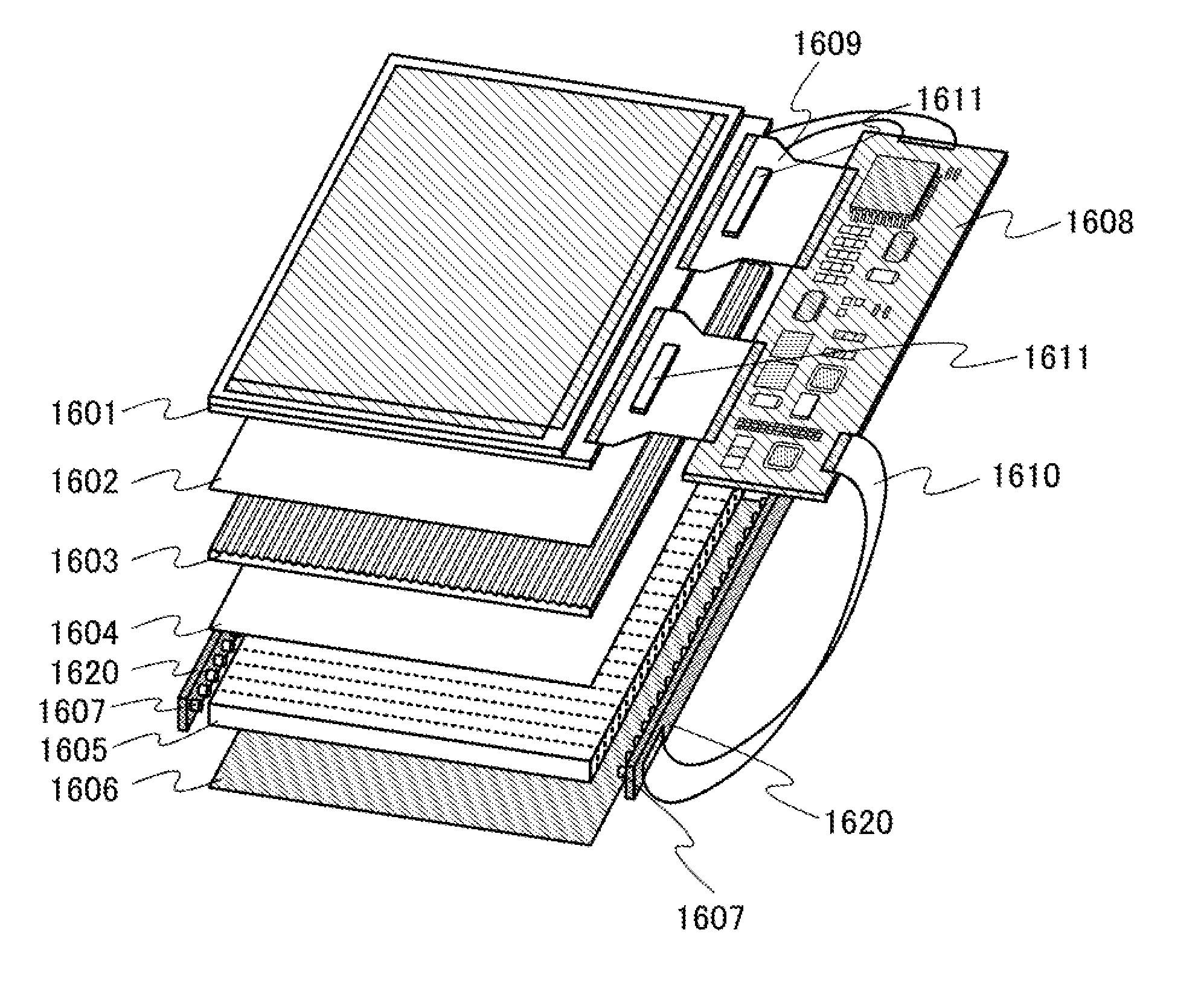

Liquid crystal display device and manufacturing method of liquid crystal display device

ActiveUS20120229724A1Increase contrastIncrease display areaLiquid crystal compositionsPretreated surfacesElectric fieldLiquid-crystal display

A horizontal electric field mode liquid crystal display device having a novel electrode structure, and a manufacturing method thereof are provided. The liquid crystal display device includes a first substrate having an insulating surface; a first conductive film and a second conductive film over the insulating surface; a first insulating film over the first conductive film; a second insulating film over the second conductive film; a second substrate facing the first substrate; and a liquid crystal layer positioned between the first substrate and the second substrate. Part of the first conductive film exists also on a side portion of the first insulating film, and part of the second conductive film exists also on a side portion of the second insulating film. The liquid crystal layer includes liquid crystal exhibiting a blue phase.

Owner:SEMICON ENERGY LAB CO LTD

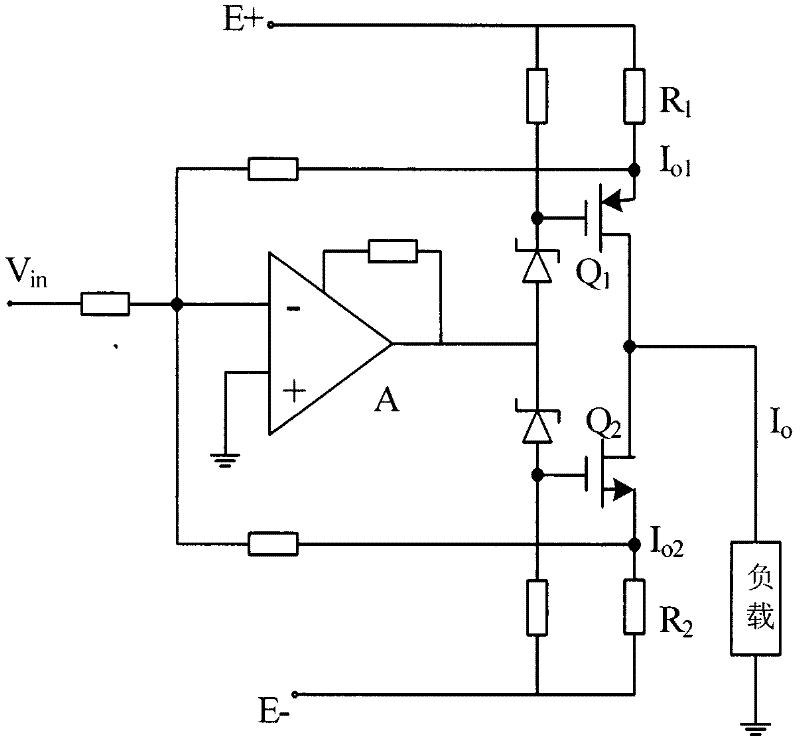

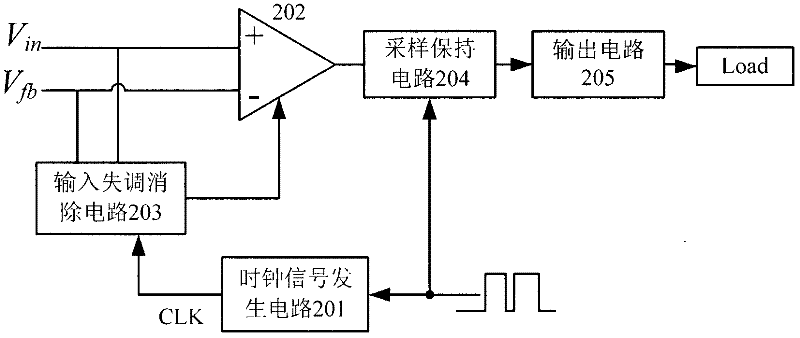

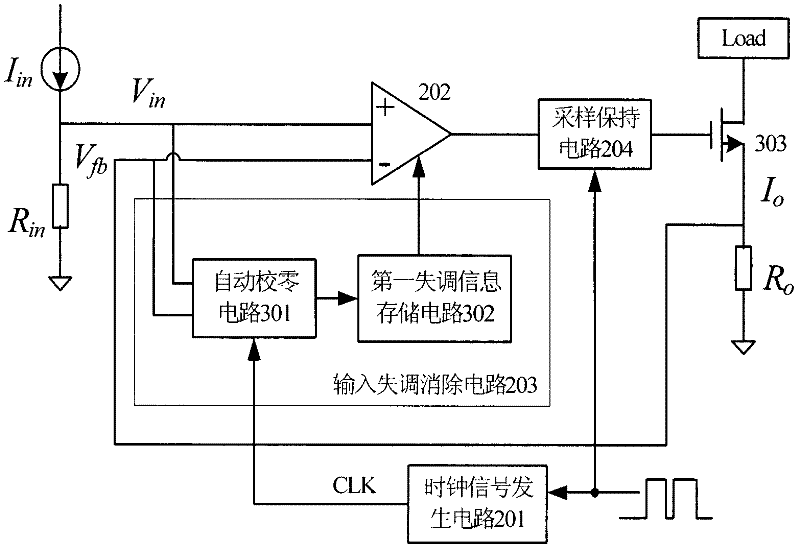

Low-offset and fast-response voltage-controlled current source, control method and power circuit applying voltage-controlled current source

ActiveCN102243505AReduce output errorReduce input offsetAmplifier with semiconductor-devices/discharge-tubesElectric variable regulationCMOSPower circuits

The invention relates to a low-offset and fast-response voltage-controlled current source. In the voltage-controlled current source which is realized by adopting an operational amplifier, an input offset voltage which is larger relative to an input reference voltage is reduced to an acceptable range through use of an automatic zeroing method, and the output error of the voltage-controlled current source is reduced. The slew rate of the operational amplifier is improved by adding a sampling hold circuit so as to realize the fast response of a circuit. The low-offset and fast-response voltage-controlled current source is especially suitable for applications, such as an LED driving circuit, requiring fast response. In addition, the input offset is reduced by adopting the automatic zeroing method, the low input offset of the voltage-controlled current source can be realized by adopting a standard CMOS (Complementary Metal Oxide Semiconducotr) process, the change of the input offset along with the changes of temperature, time, illumination and irradiation is unnecessarily considered, and the requirement on layout matching is lower, therefore the production cost and time are reduced.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

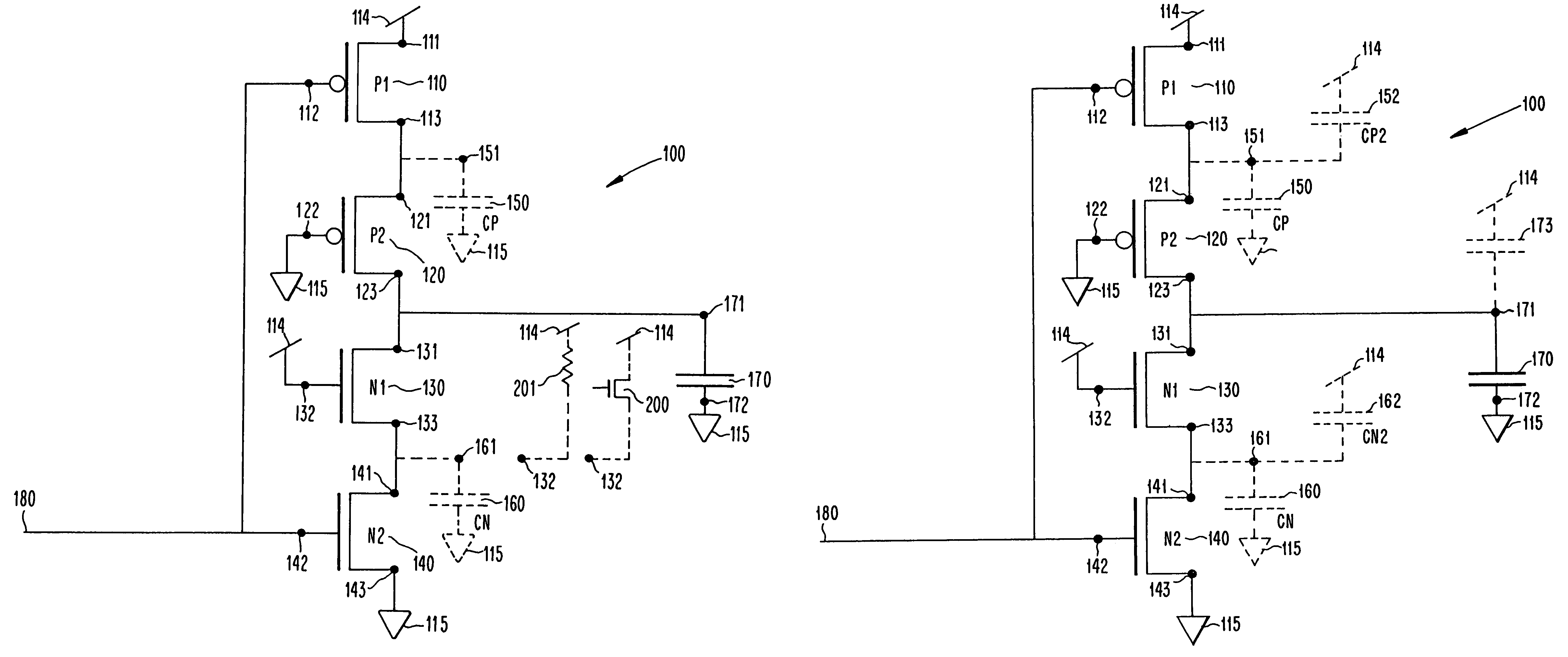

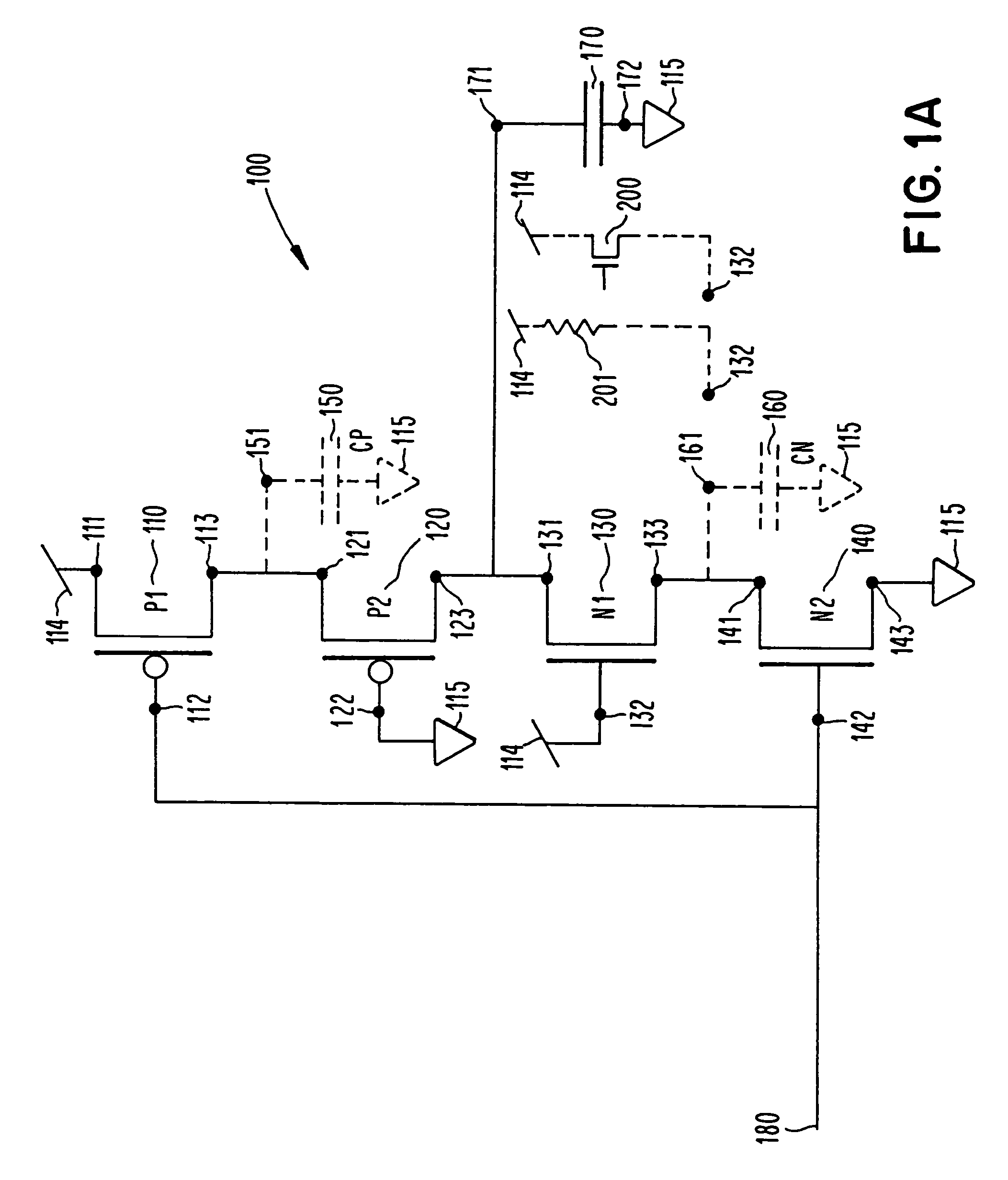

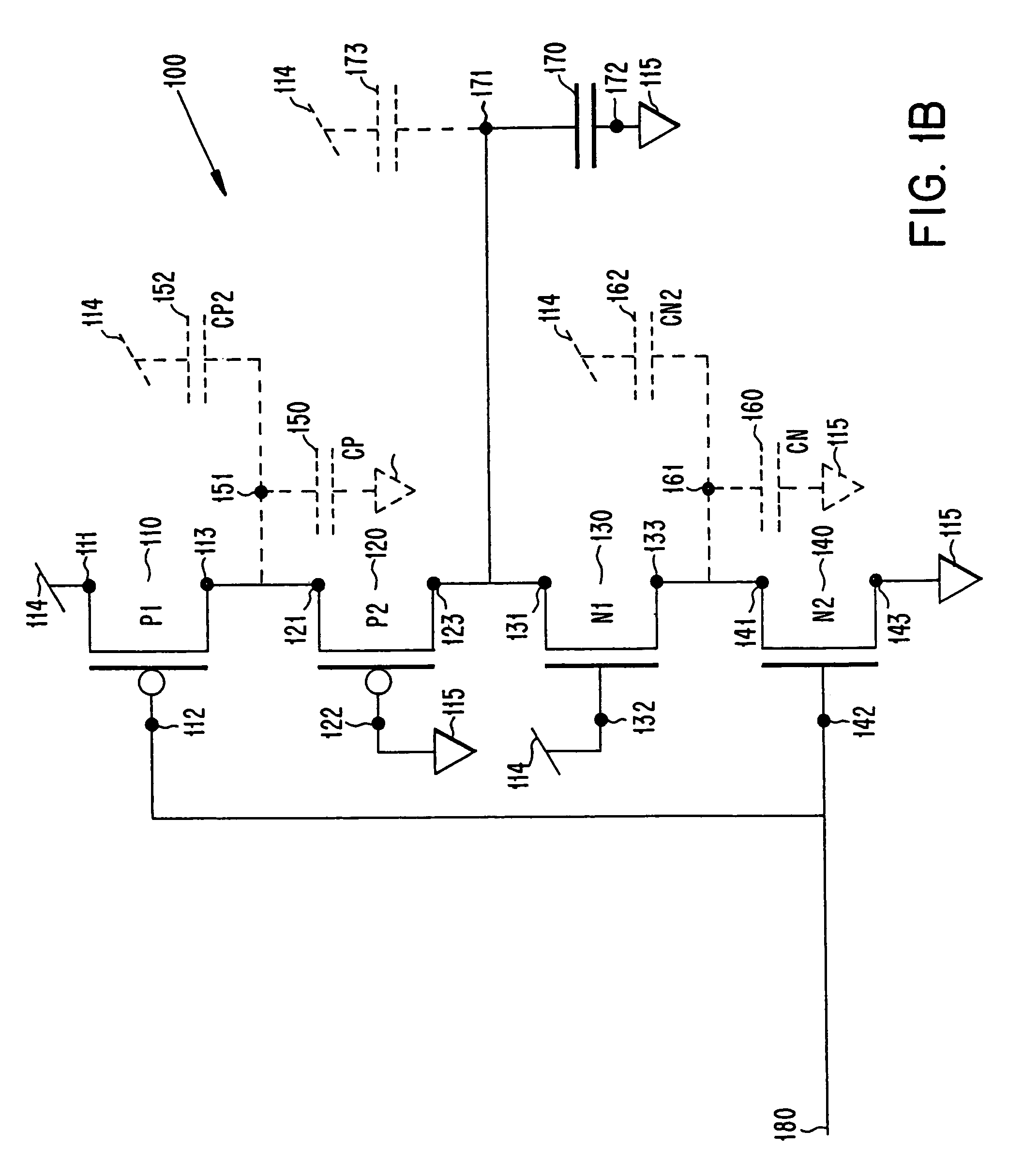

Cascode signal driver with low harmonic content

InactiveUS7205807B2Harmonic reductionReduce switching speedAmplifier modifications to reduce detrimental impedenceElectronic switchingDriver circuitControl signal

A method and apparatus for minimizing harmonic content in a digital signal driver circuit are disclosed. A digital input signal applied to an input node generates a corresponding digital output in a circuit with two or more MOS devices in cascode connection with each other. The slew rate of leading or trailing edge transitions associated with the output signal are controlled using one or more parasitic capacitances associated with the fabrication of two or cascode connected MOS devices. The two or more cascode connected MOS devices may further each have gate electrodes connected to a fixed potential so as to minimize the harmonic content. A control signal may further be applied to each gate electrode to turn off a leakage current path between source and drain electrodes. Harmonics may further be controlled by limiting a conductance between gate electrodes and fixed potentials using an active or passive device.

Owner:TELEFON AB LM ERICSSON (PUBL)

Thin film transistor substrate and display device

InactiveUS7781767B2Desired switching performancePerformance of semiconductor will deteriorateSemiconductor/solid-state device detailsSolid-state devicesDisplay deviceAlloy thin film

Owner:KOBE STEEL LTD

Digital driving of active matrix displays

ActiveUS9905159B2Less complexLess space consumingStatic indicating devicesNon-linear opticsActive matrixDisplay device

A method for digital driving of an active matrix display with a predetermined frame rate is described. The display contains a plurality of pixels organized in a plurality of rows and a plurality of columns. The method includes representing each of the plurality of pixels of an image to be displayed within a frame by an n-bit digital image code. The method also includes dividing the image frame into sub-frames, which may be of substantially equal duration. Within each sub-frame, the method includes sequentially selecting at least one of the plurality of rows twice. Upon a first selection, a first digital code is written to the selected row and upon a second selection a second digital code is written to the selected row. There is a predetermined time delay between the second selection and the first selection. Digital driving circuitry is also described.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

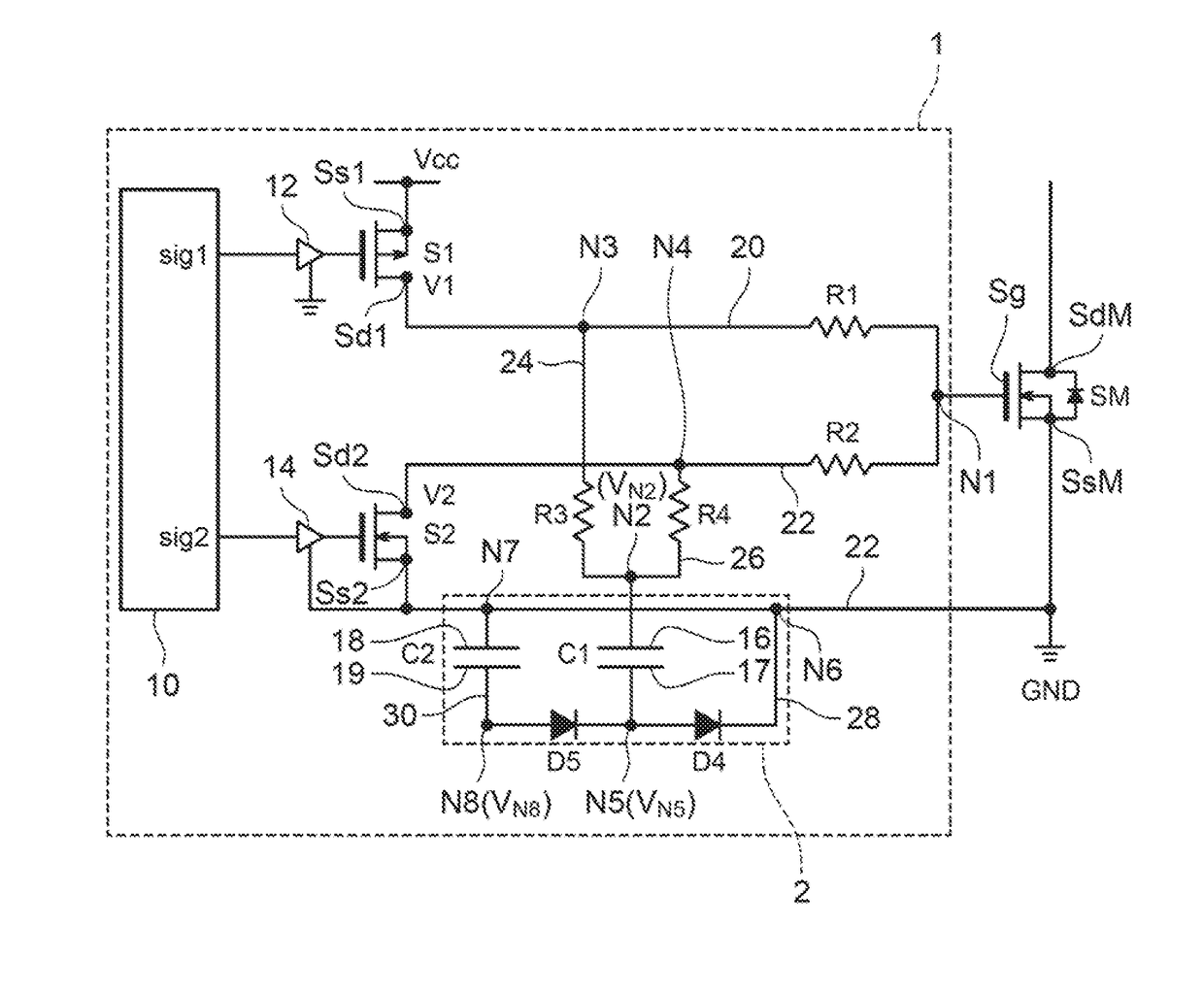

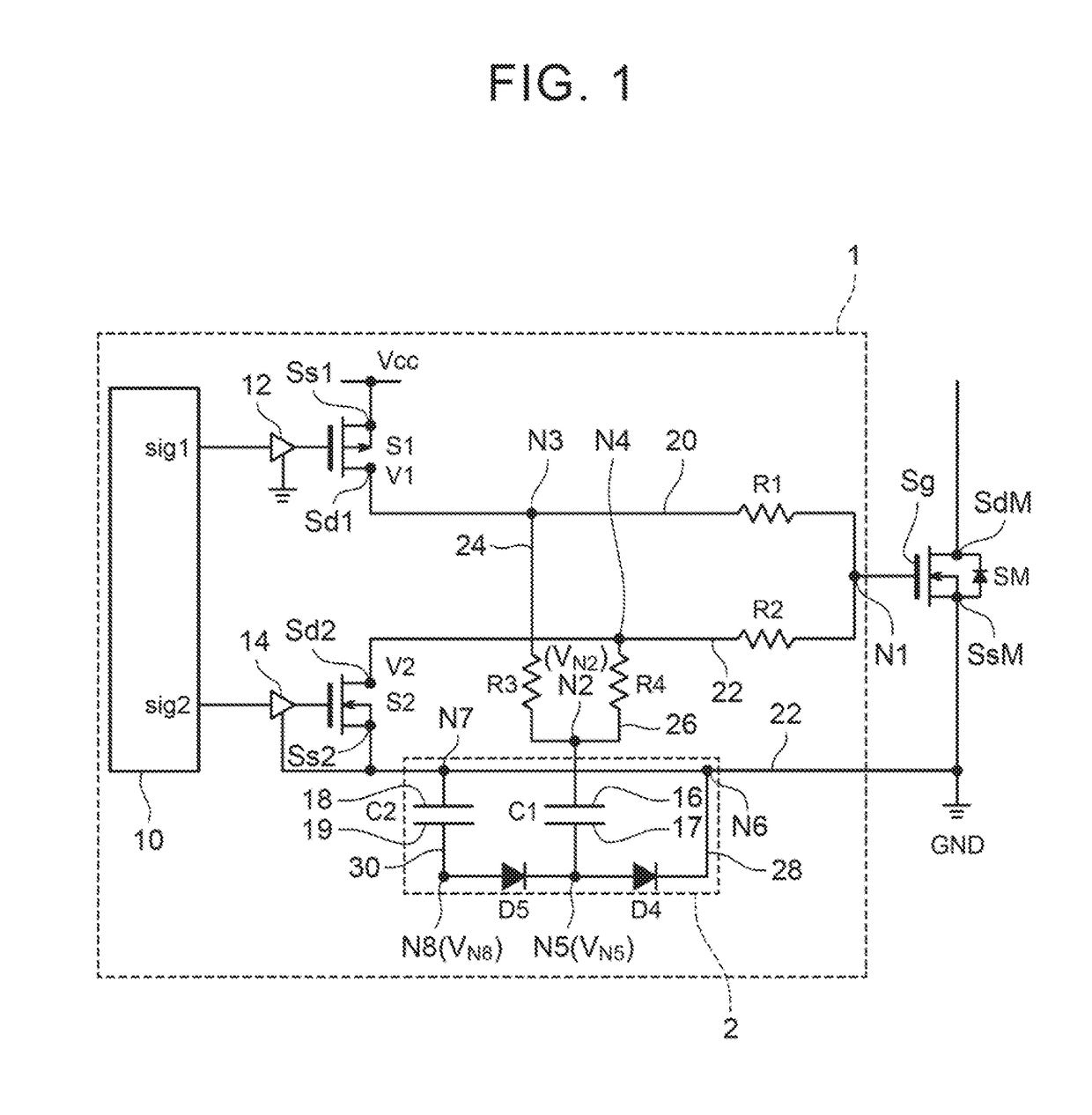

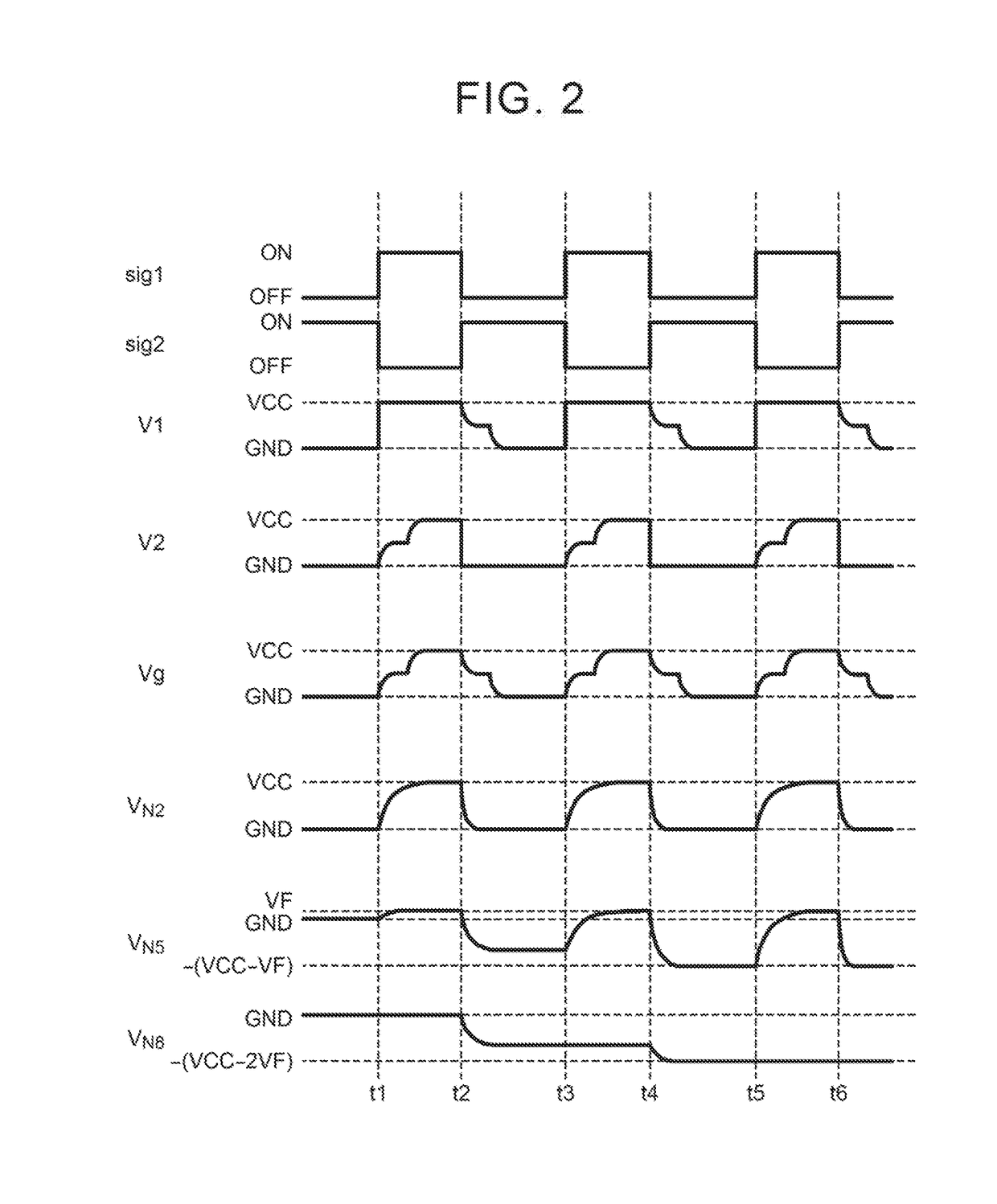

Switching Circuit And Power Conversion Circuit

ActiveUS20170149330A1Reduce switching speedSwitching loss increaseTransistorApparatus without intermediate ac conversionCapacitanceNegative voltage

A first switching element and a gate of a voltage-driven switching element are connected by a gate turn-on wiring through a first resistor. The gate of the voltage-driven switching element and a second switching element are connected by a gate turn-off wiring through a second resistor. A charge pump unit has a first capacitor, and a second capacitor configured to output a negative voltage. A resistor unit is arranged in at least one of a first wiring configured to connect the gate turn-on wiring and the first capacitor and a second wiring configured to connect the gate turn-off wiring and the first capacitor, and is configured to charge the first capacitor through the first wiring when the first switching element is turned on and to discharge the first capacitor through the second wiring when the second switching element is turned on.

Owner:TOYOTA JIDOSHA KK

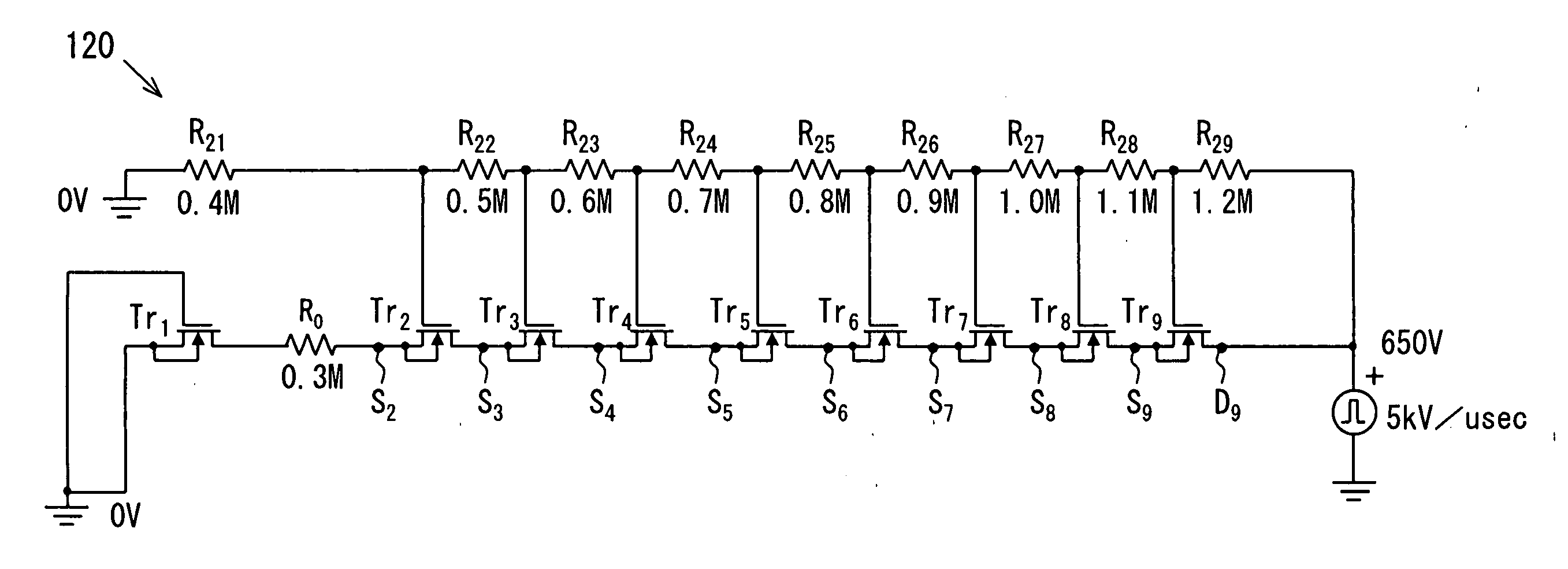

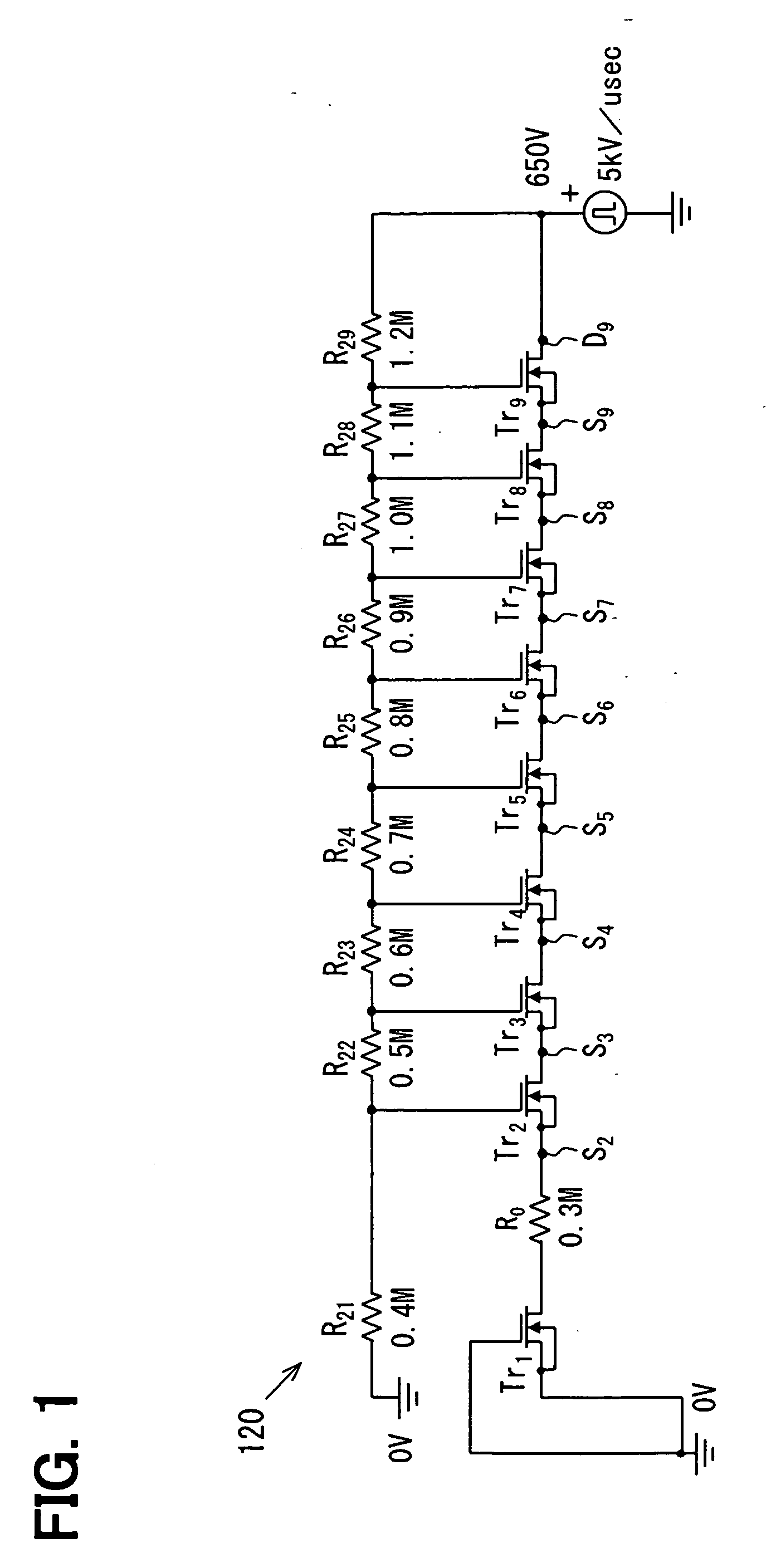

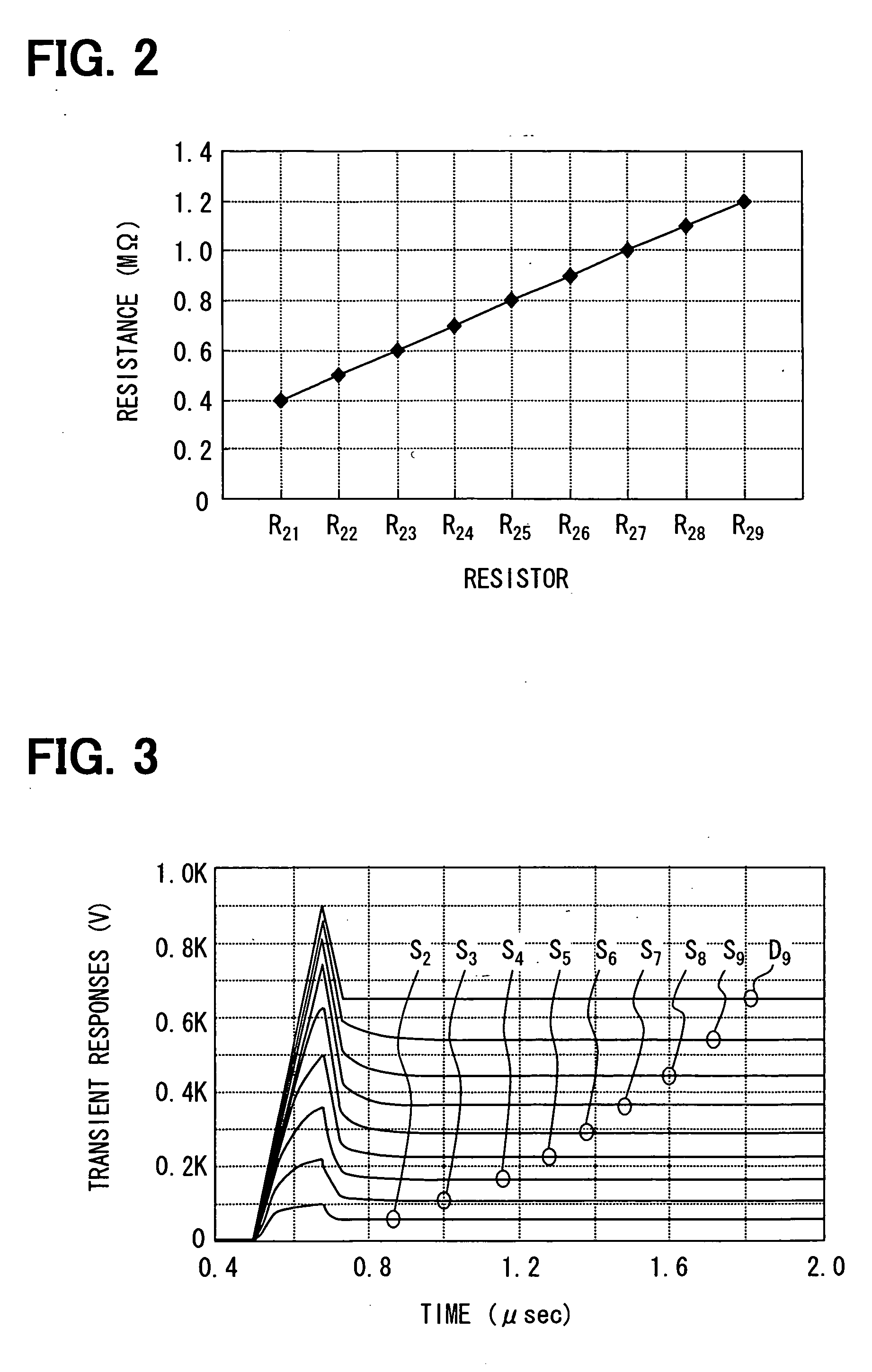

Semiconductor device for high voltage IC

InactiveUS20060231868A1Improve device speedFast transferSolid-state devicesElectronic switchingElectrical resistance and conductanceDevice material

A semiconductor device includes: a plurality of transistors connected in series between a ground potential and a predetermined potential; an input terminal provided by a gate terminal of the first step transistor; a plurality of resistors connected in series between the ground potential and the predetermined potential; and an output terminal provided by a predetermined potential side terminal of the Nth step transistor. A gate terminal of each transistor other than the first step transistor is sequentially connected between neighboring two resistors. One of the resistors defined as an Ith step resistor has a resistance, which is smaller than a resistance of a (I+1)th step resistor.

Owner:DENSO CORP

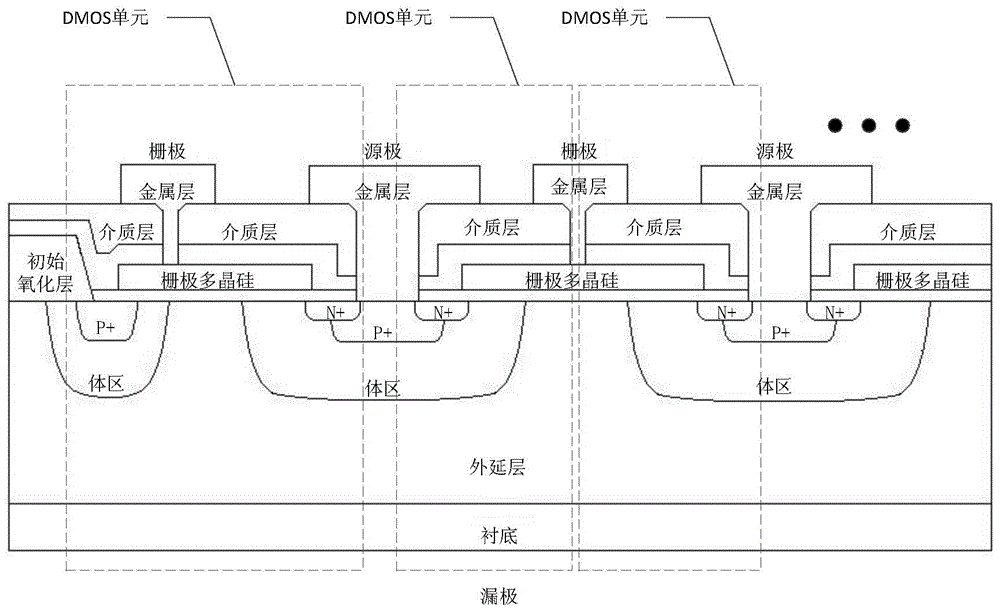

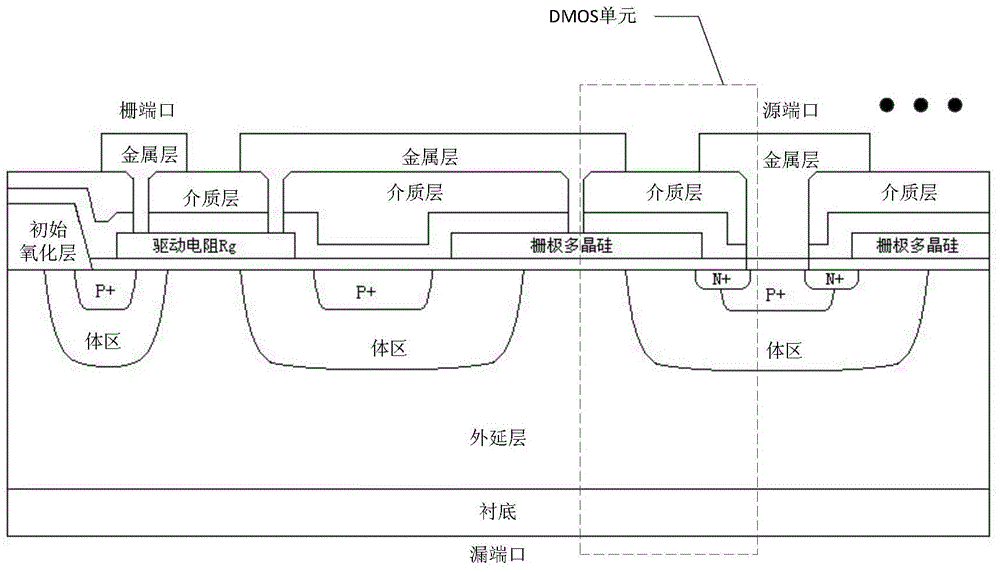

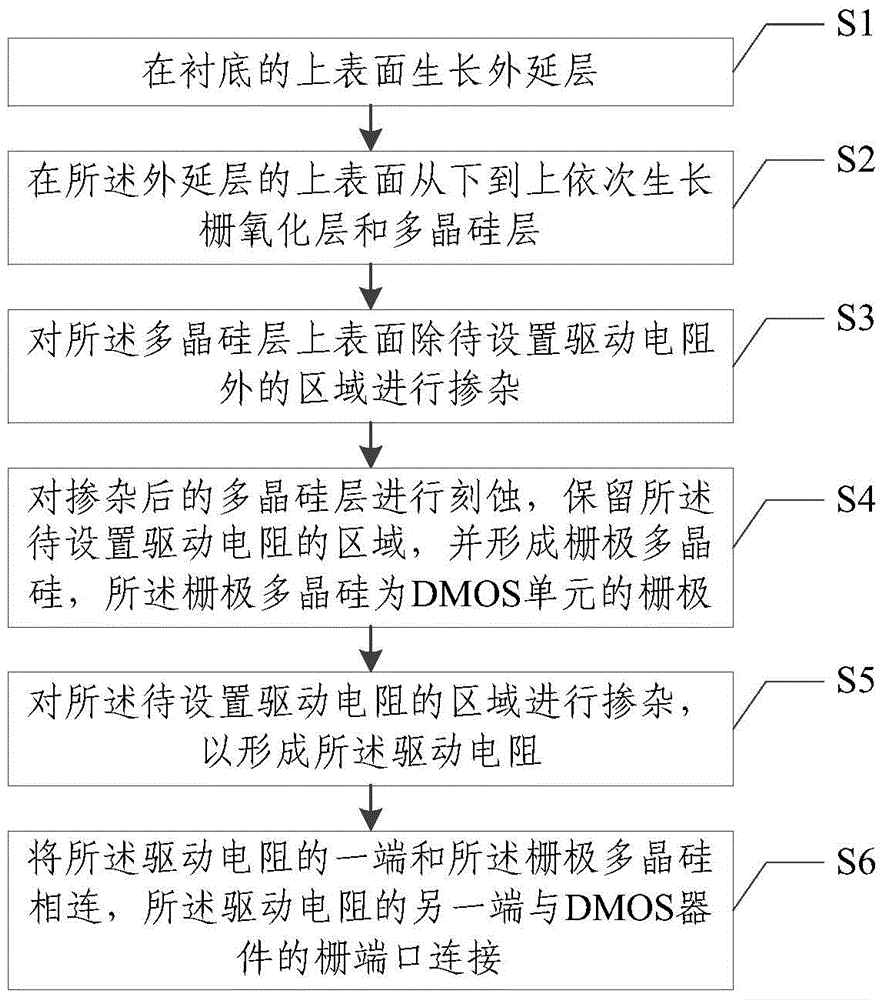

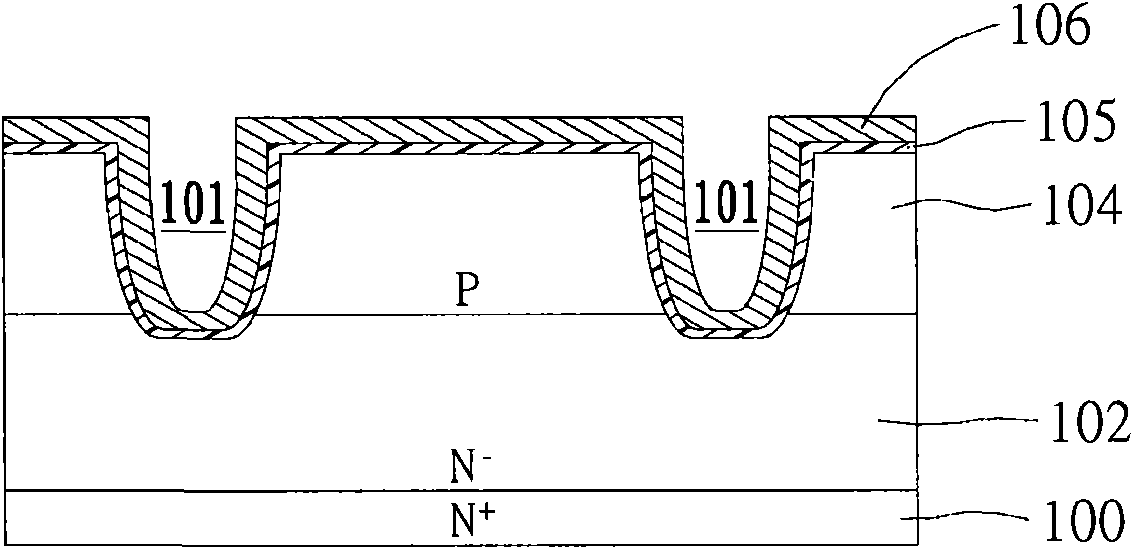

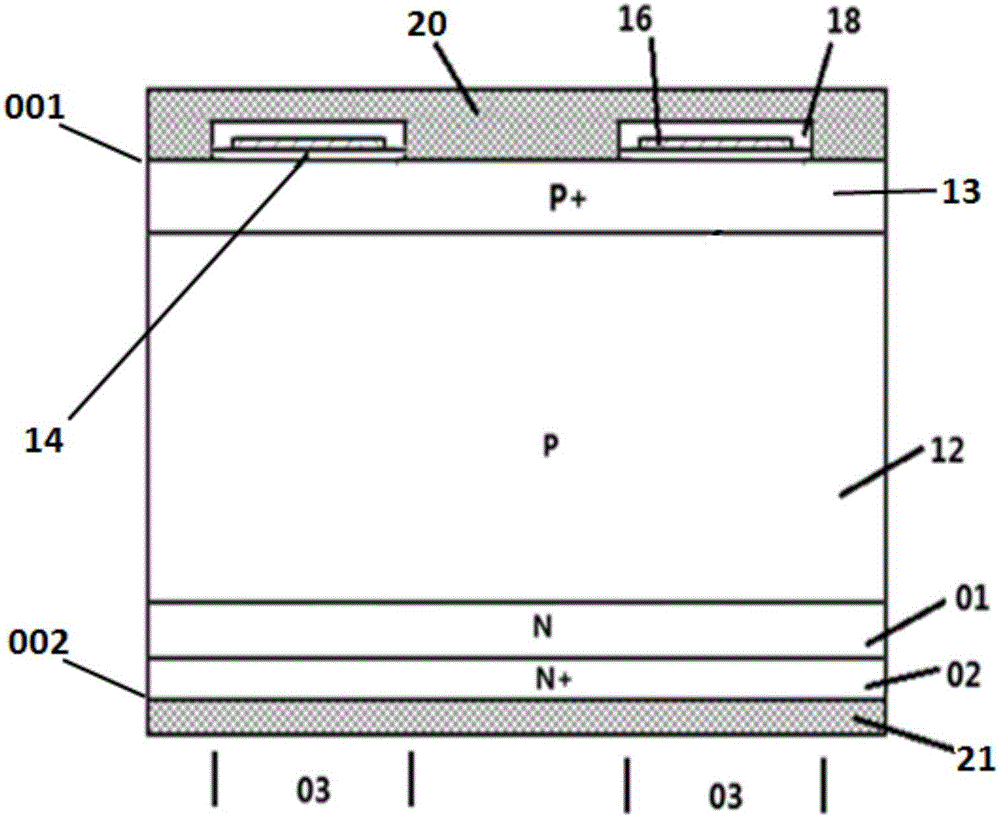

Double diffusion metal-oxide-semiconductor (DMOS) device of integrated driving resistor and method for manufacturing same

InactiveCN104867972AReduce switching speedSuppress high frequency oscillationSemiconductor/solid-state device manufacturingSemiconductor devicesDouble diffusionSemiconductor

The present invention discloses a DMOS device of an integrated driving resistor and a method for manufacturing the same, and relates to the semiconductor technology field. The DMOS device comprises a grid port, a driving resistor and a plurality of DMOS units. Each DMOS unit comprises a grid, the grid port is connected with one end of the driving resistor, and the other end of the driving resistor is connected with the grid of each DMOS unit separately. According to the present invention, by arranging the driving resistor of the grid port in the DMOS device, the on-off speeds of the DMOS units are reduced, and the high frequency oscillation is restrained.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

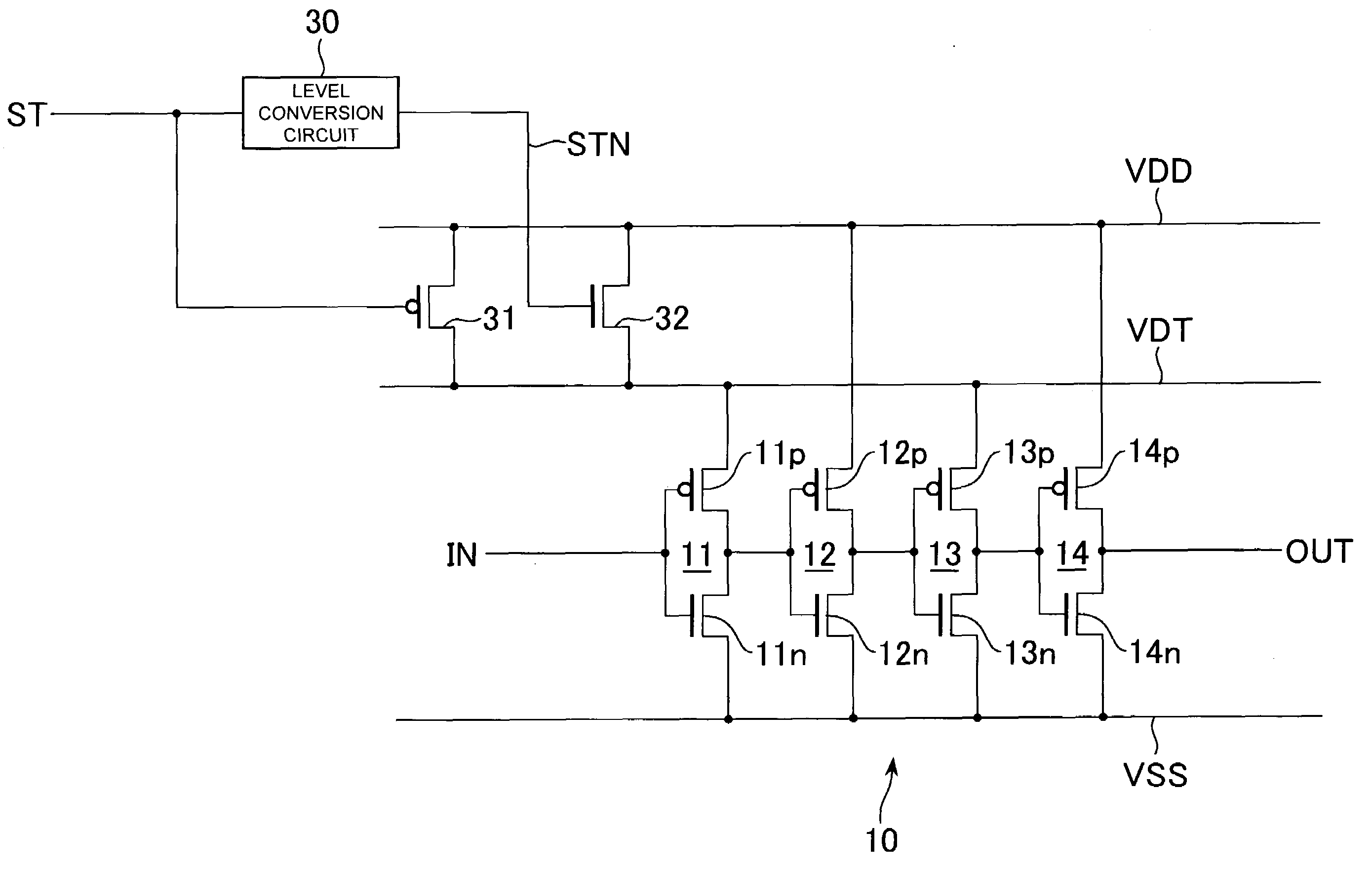

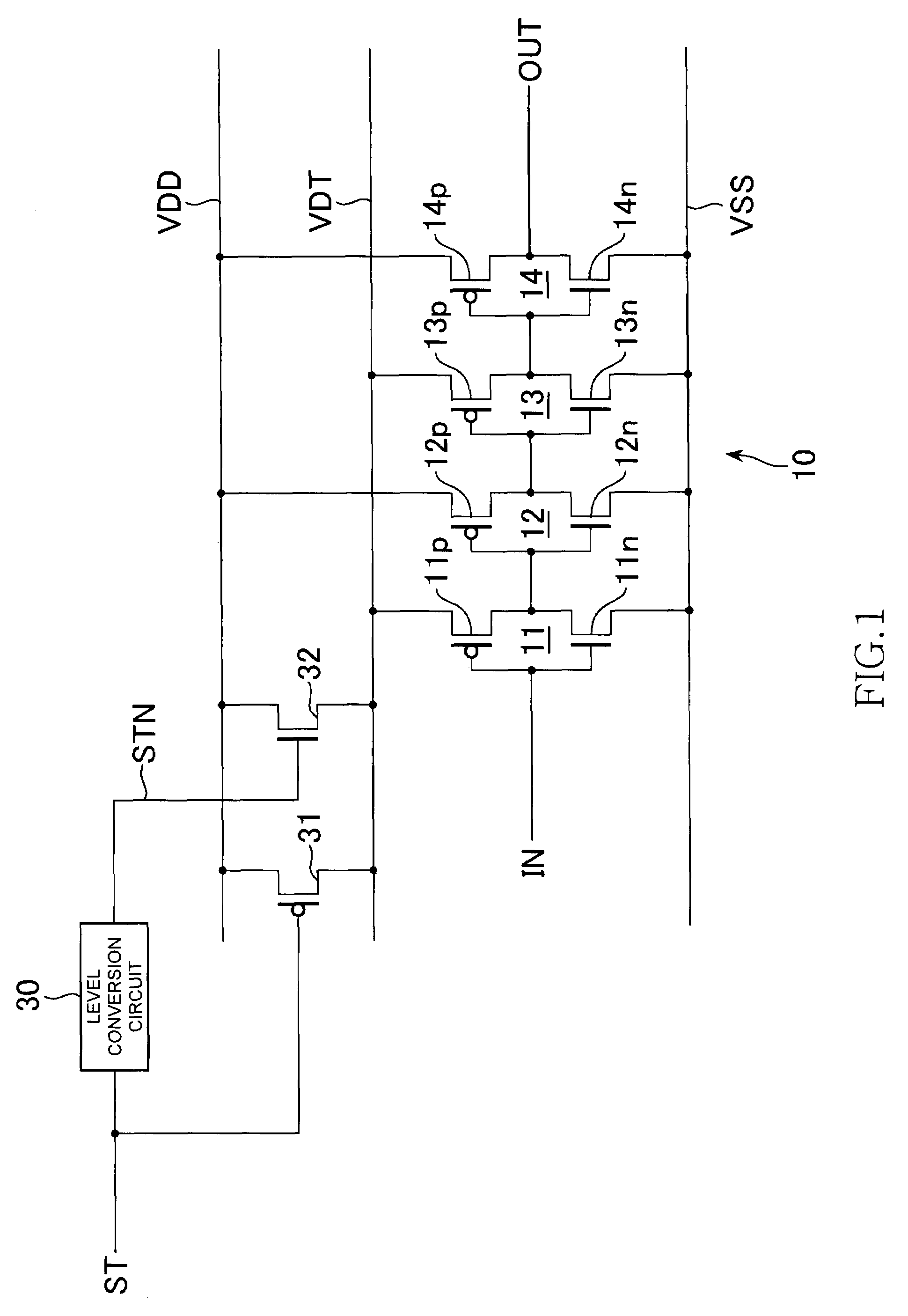

Semiconductor device having a pseudo power supply wiring

ActiveUS7532036B2Reduce power consumptionReduce switching speedReliability increasing modificationsPower reduction by control/clock signalPower semiconductor deviceEngineering

A semiconductor device includes main power supply wirings VDD and VSS, an pseudo power supply wiring VDT, inverters connected between the pseudo power supply wiring VDT and the main power supply wiring VSS, and inverters connected between the main power supply wiring VDD and the main power supply wiring VSS. Between the main power supply wiring VDD and the pseudo power supply wiring VDT, an N-channel MOS transistor and a P-channel MOS transistor that are rendered a conductive state at the time of active are connected in parallel. According to the present invention, the transistors different in conductivity type are used in parallel, and thus, it becomes possible to reduce power consumption at the time of standby while suppressing a decrease in switching speed from a standby state to an active state.

Owner:LONGITUDE LICENSING LTD

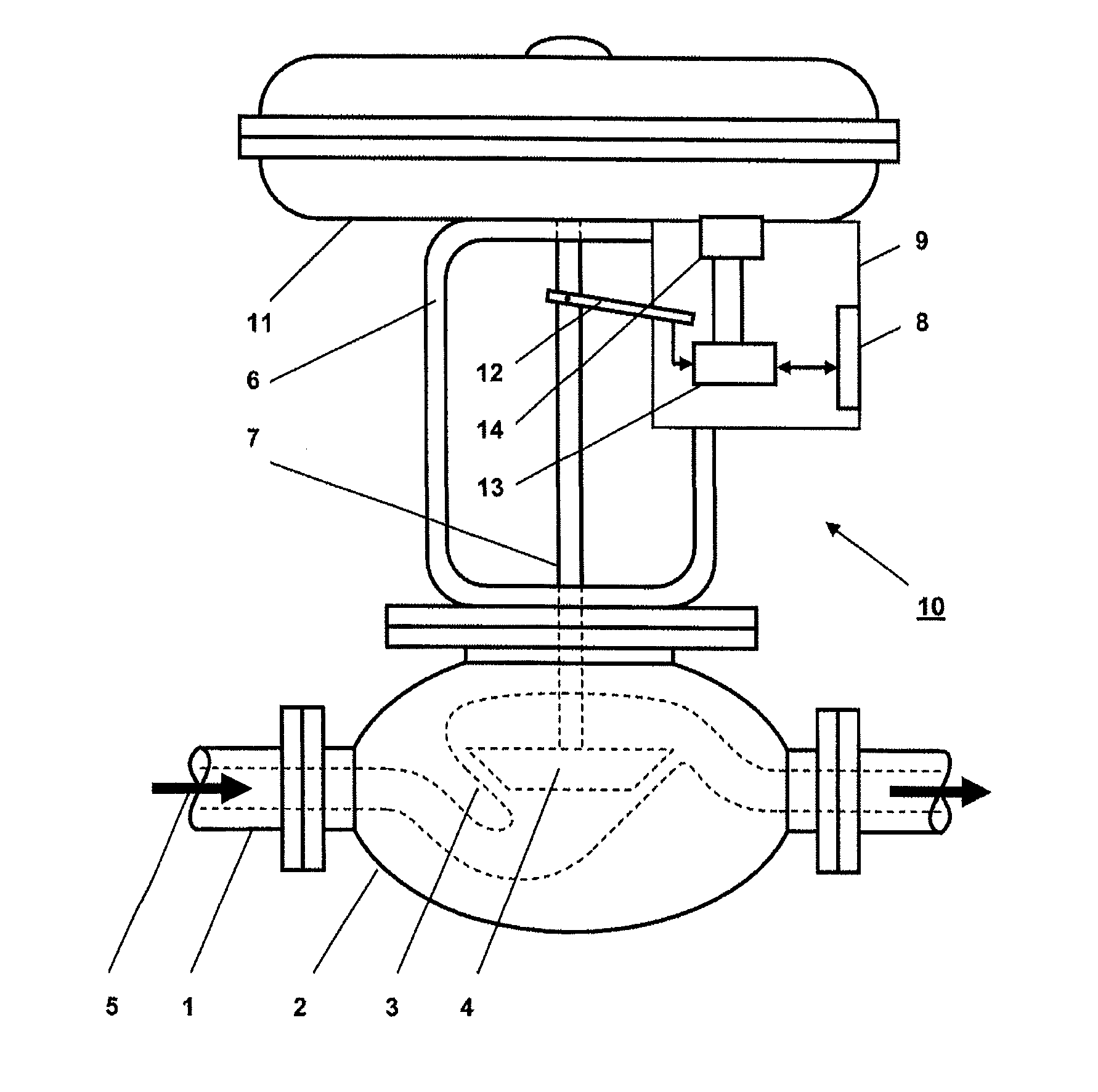

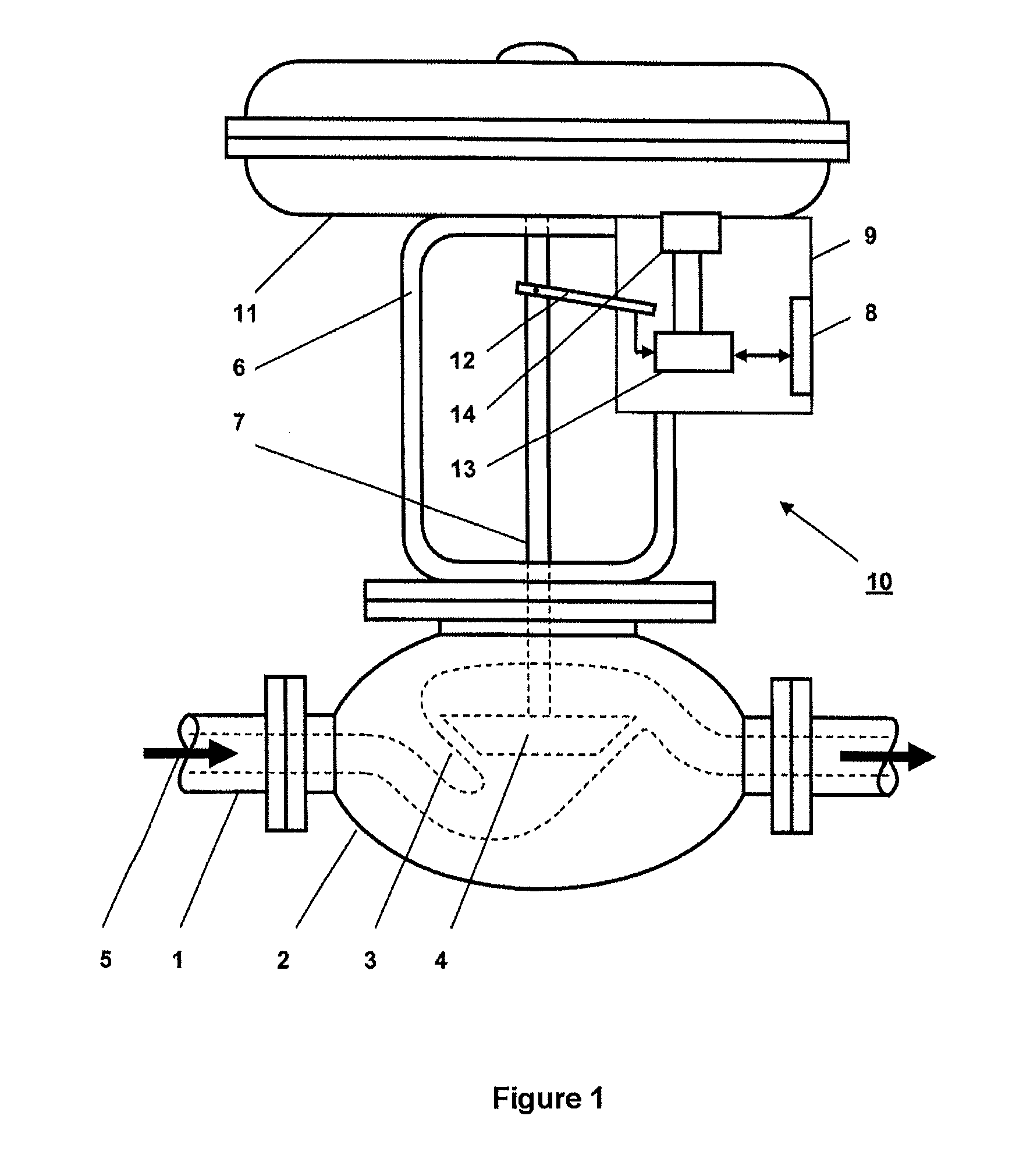

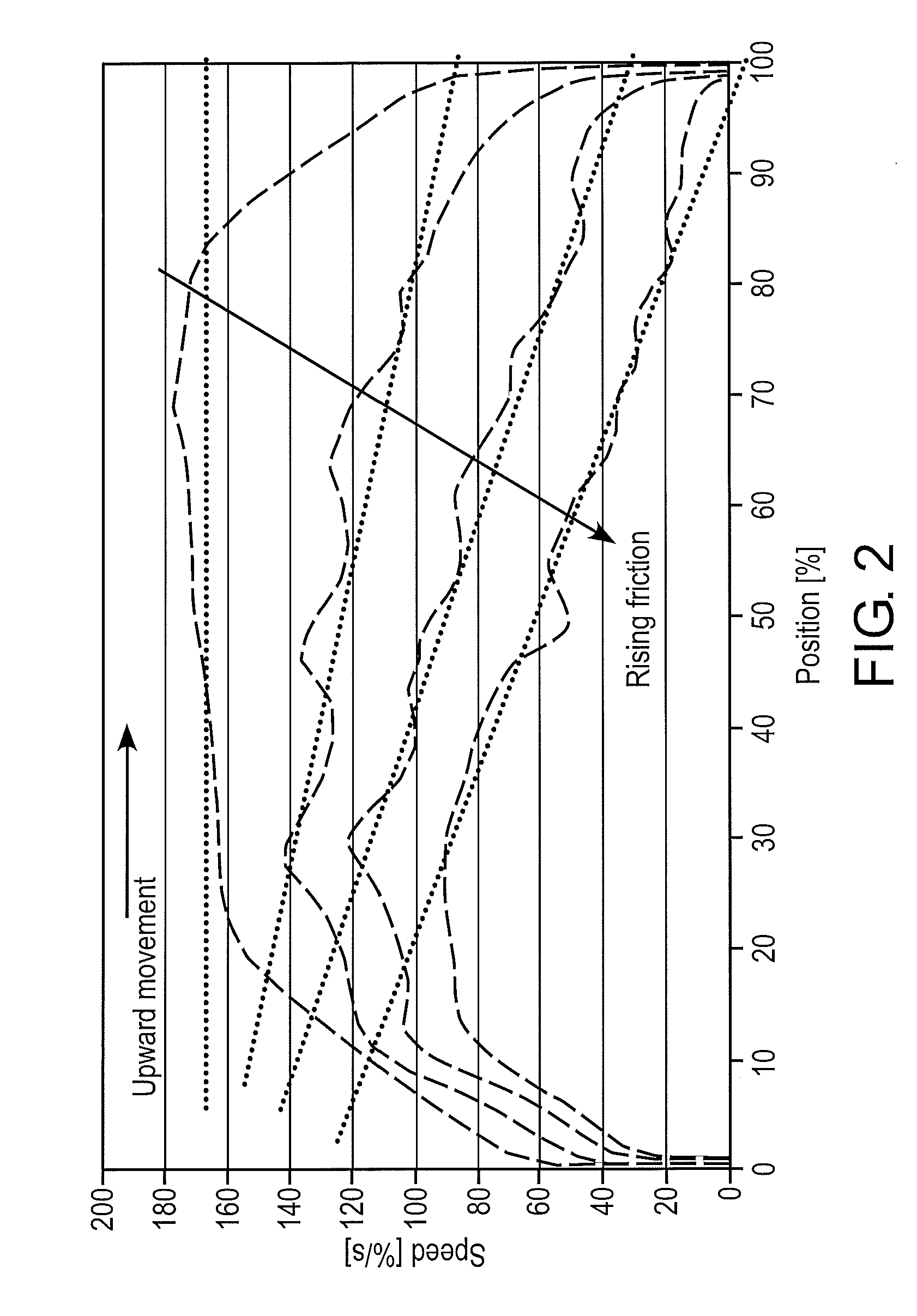

Electronic wear state determination in a valve arrangement

InactiveUS20100305874A1Accurate valueReduce switching speedPlug gaugesFluid-pressure actuator testingPosition sensorVALVE PORT

A method is provided for determining the electronic wear state of a valve arrangement for controlling a process medium flow. A valve element is arranged to move axially within a valve housing, is reset by a spring, and is moved by application of control pressure via an I / P converter. The I / P converter ensures a constant opening cross section at least over a portion of the switching stroke, in the case of which the time at which various positions of the valve element along the ventilating and / or venting distance are reached is determined by means of a position sensor system, and this time is used to mathematically derive the speeds of the valve element prevailing at these positions by means of an evaluation unit. The change profile of the speeds represents a measure of the wear state of the valve mechanism.

Owner:ABB TECH AG

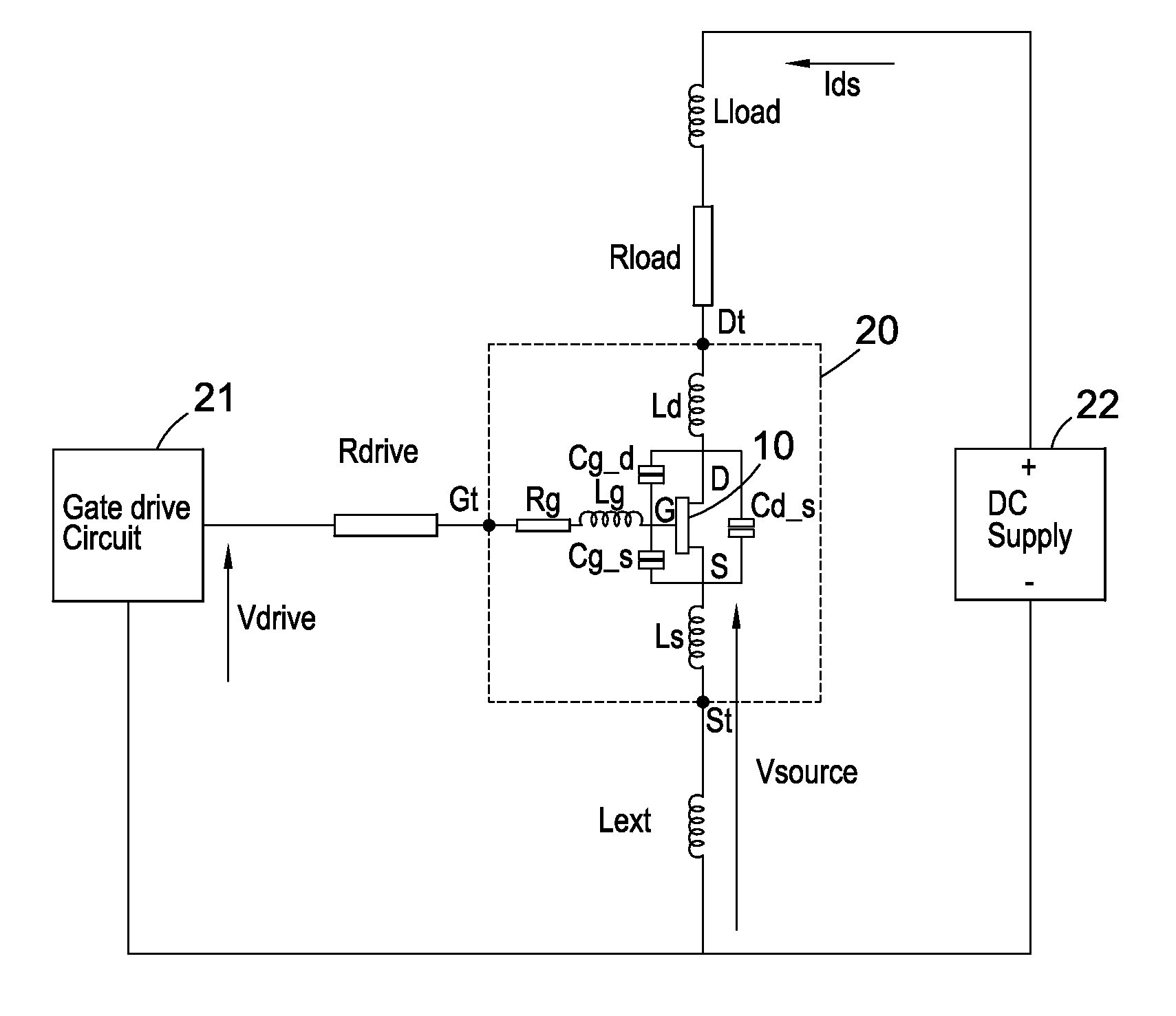

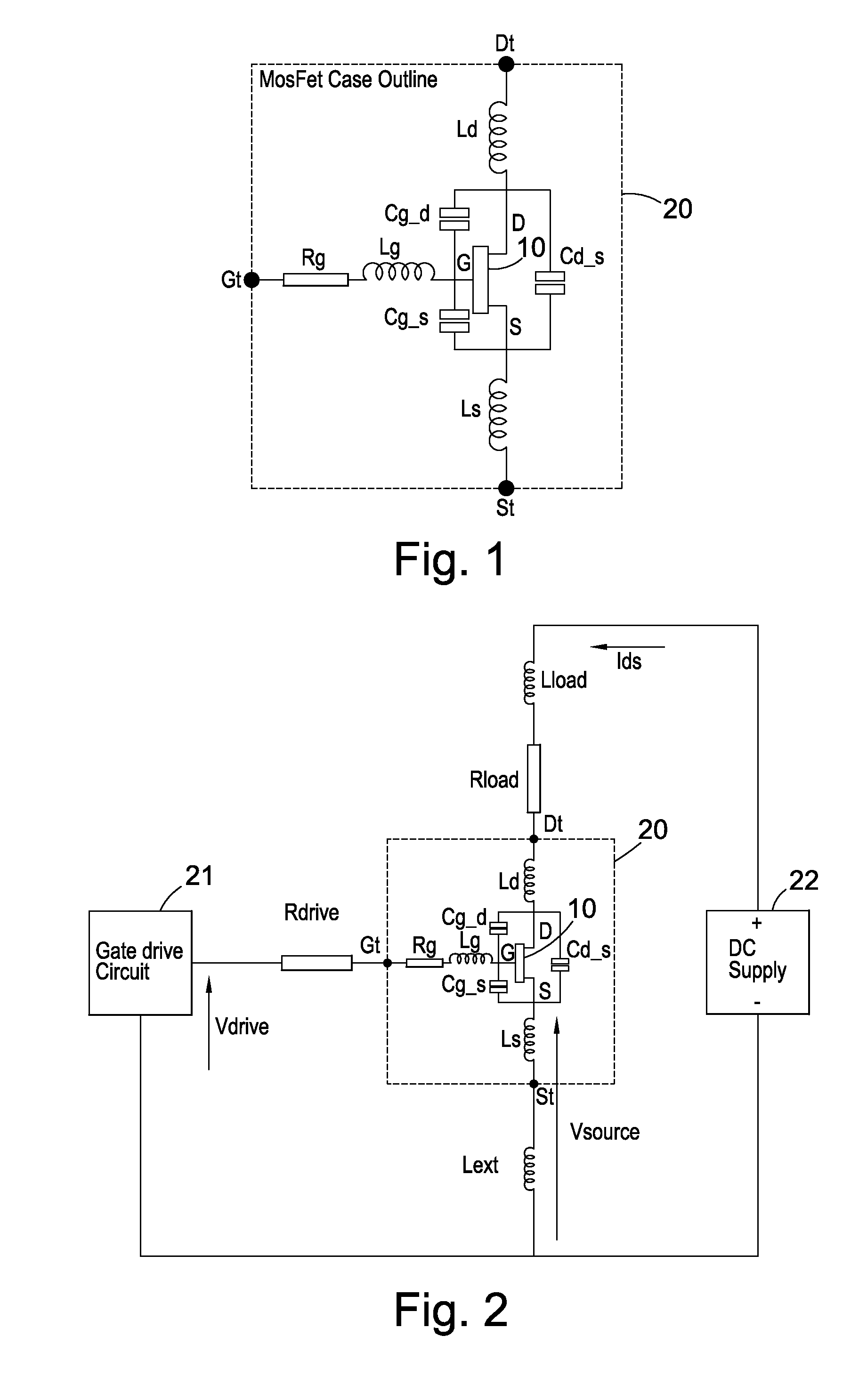

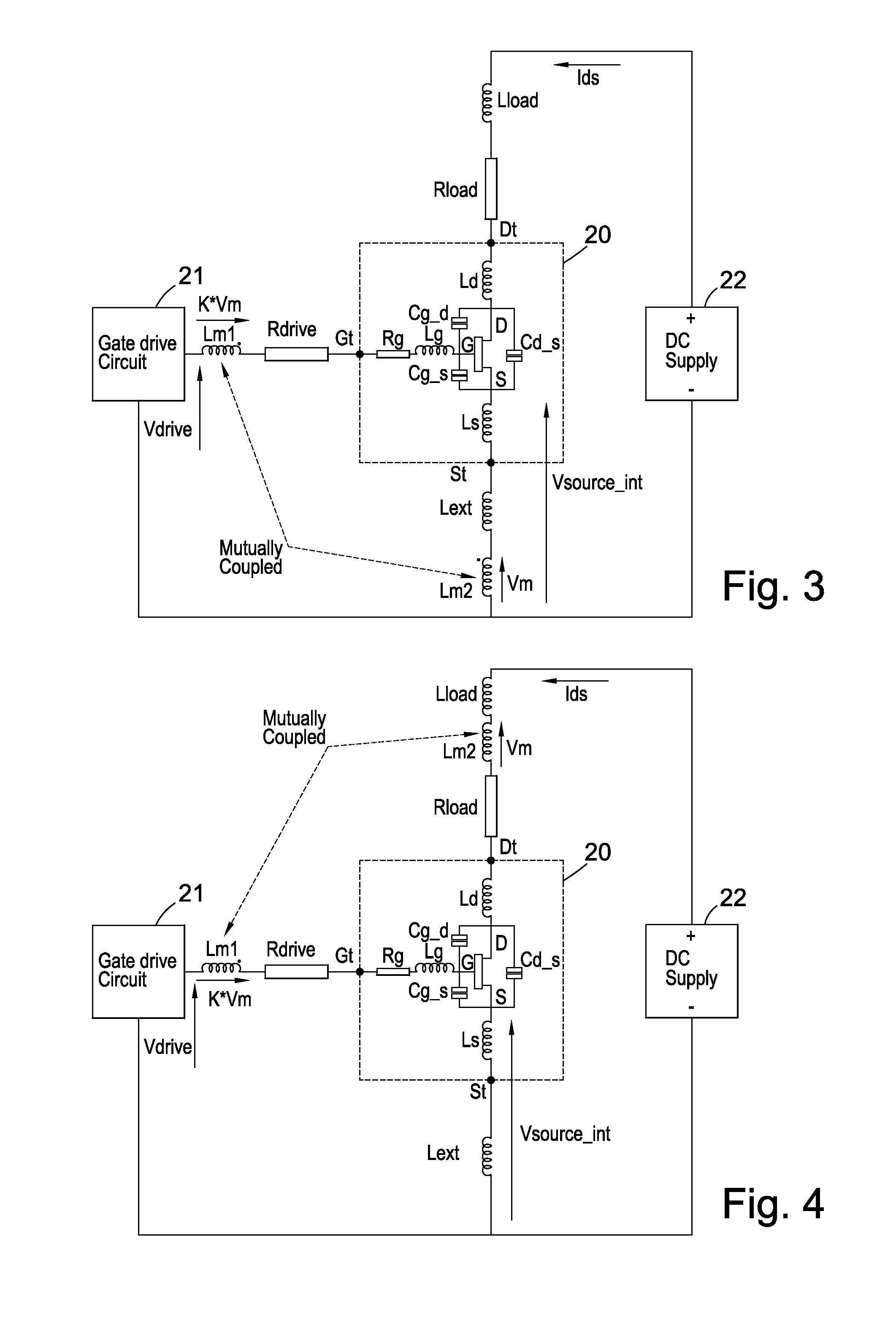

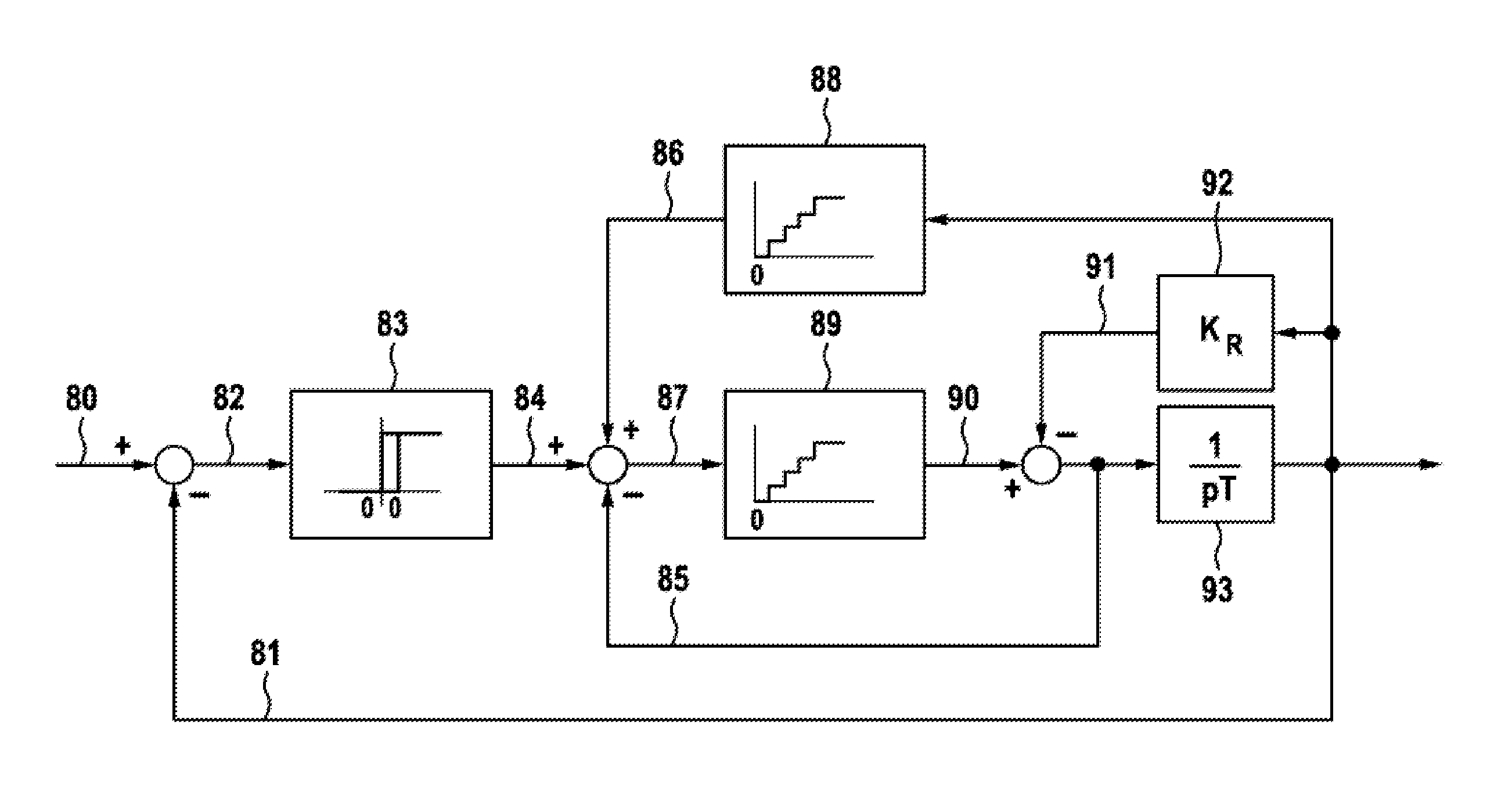

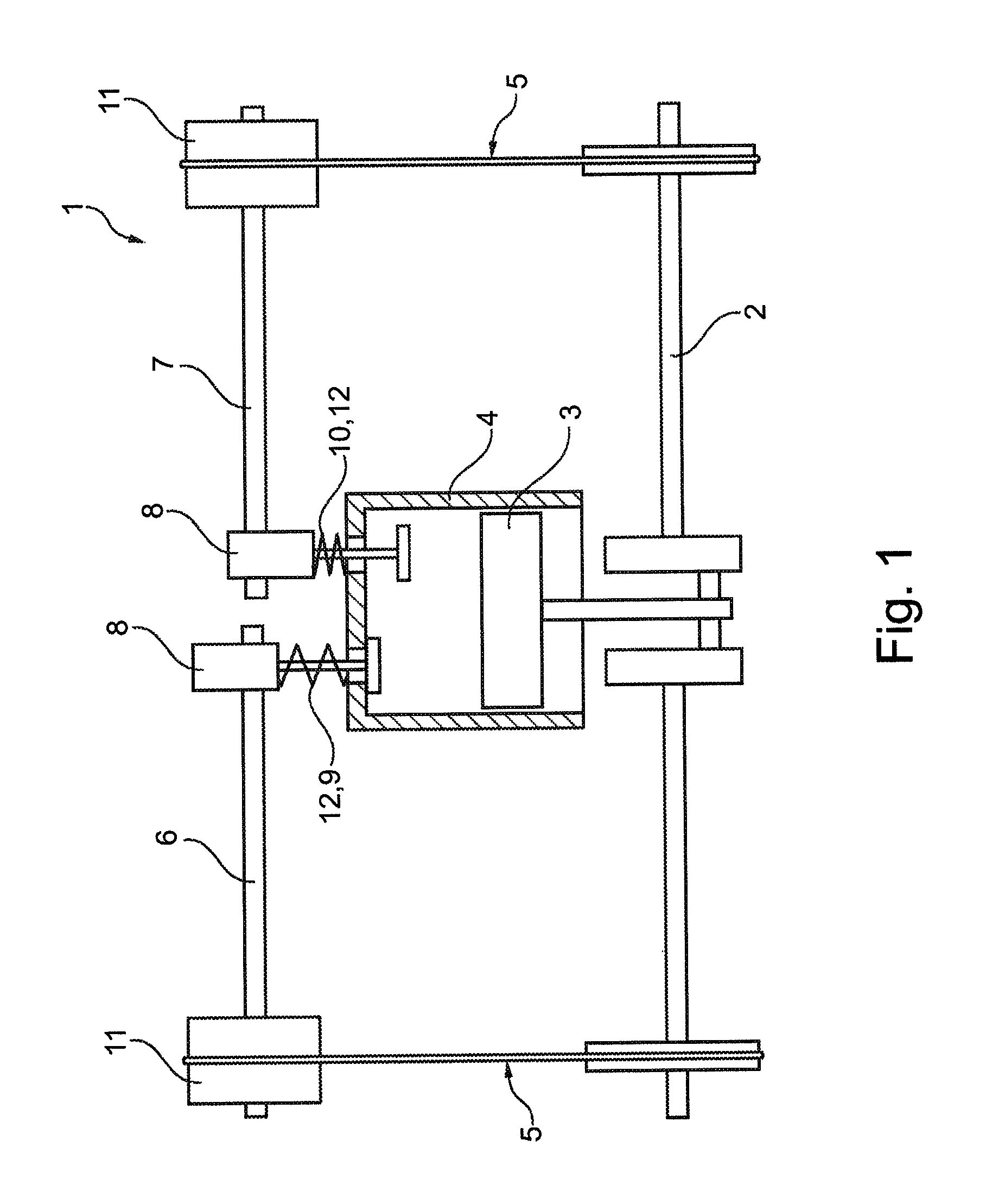

Drive circuit and method for a gated semiconductor switching device

ActiveUS20140203849A1Fast switching speedReduce switching speedTransistorElectronic switchingEngineeringGate voltage

Drive circuit and method for a gated semiconductor switching device A drive circuit and method for a gated semiconductor switching device (10) comprising providing coupling such as a mutual inductance between a gate drive circuit (21) for the device and a drain to source current supply circuit (22) for the device in order to change a gate voltage provided by the gate drive circuit dependent on a rate of change of a current in the drain to source current supply circuit. The change in gate voltage has a magnitude and phase arranged to increase or decrease a switching speed of the gated semiconductor switching device.

Owner:E2V TECH (UK) LTD

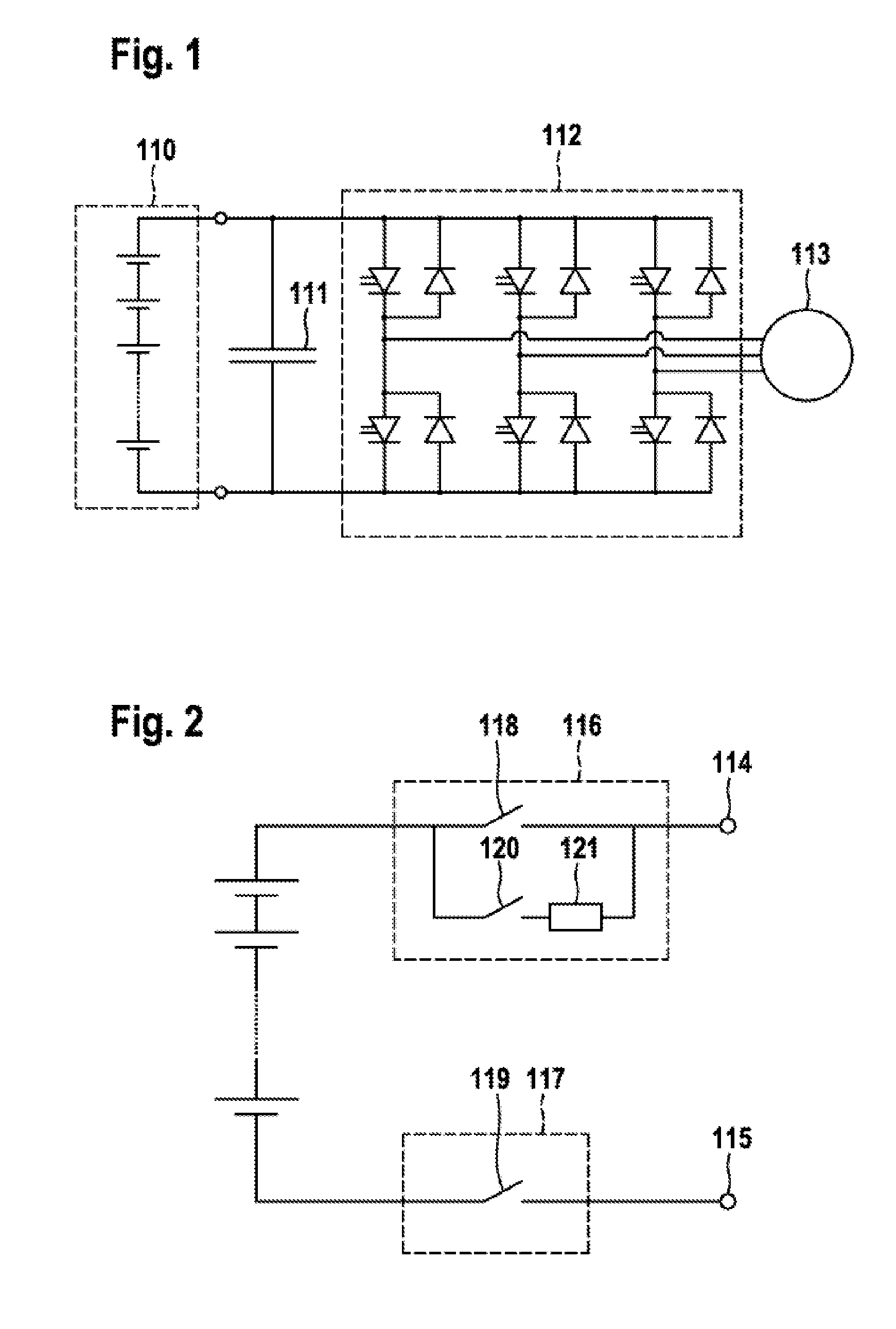

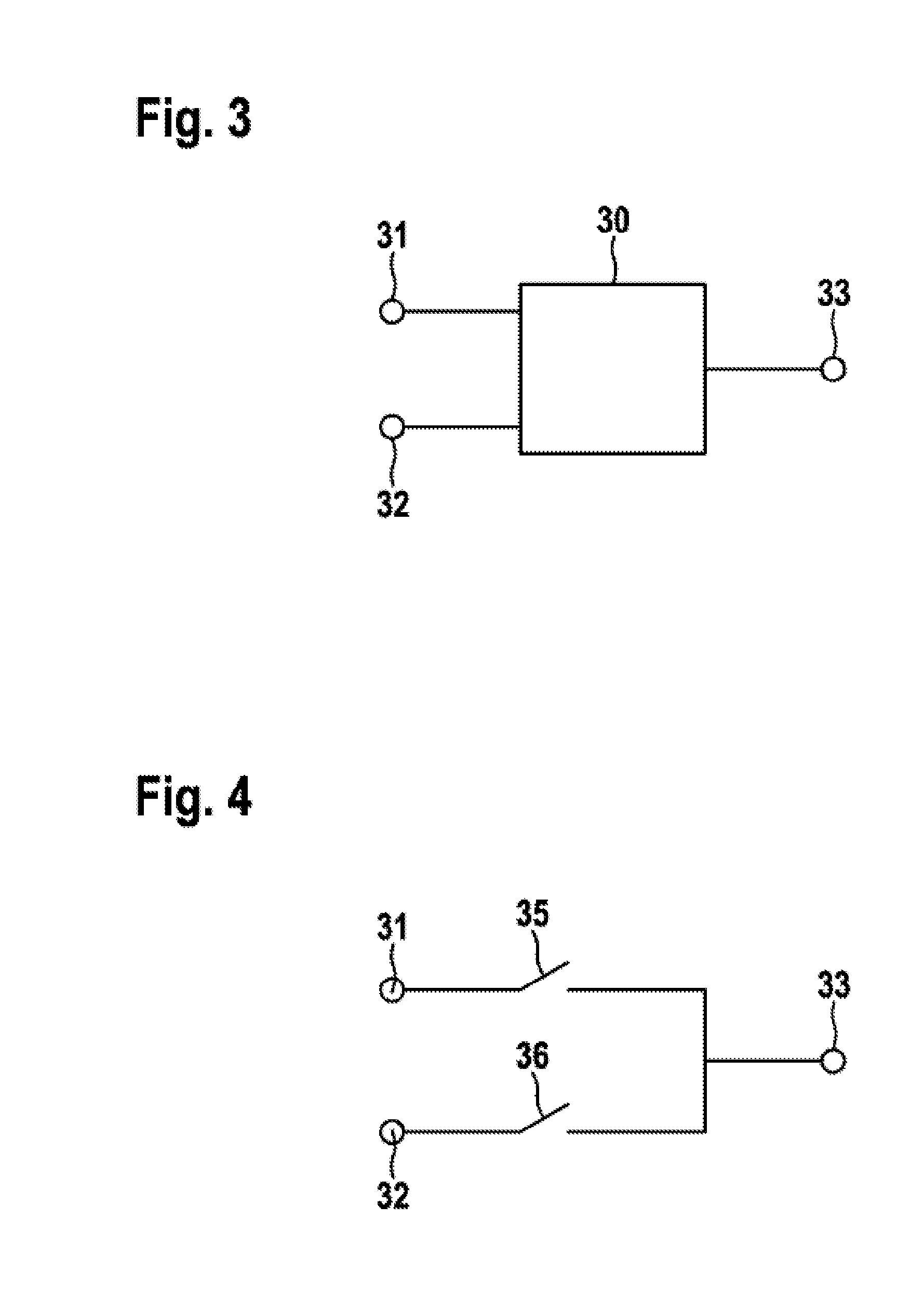

Method for Adjusting a DC Voltage Intermediate-Circuit Voltage

ActiveUS20130278190A1CostFunctionalMotor/generator/converter stoppersAC motor controlLow voltageEngineering

A method is disclosed for adjusting a voltage of a DC-voltage intermediate circuit in a battery system having a battery and a drive system. The battery is configured to output one selectable output voltage from n+1 different output voltages. In a first step of the method, an actual value of the voltage of the DC-voltage intermediate circuit is determined, and is then compared with the various output voltages of the battery. A first selected output voltage of the battery, which is the highest voltage of those output voltages of the battery which are less than the actual value of the voltage of the DC-voltage intermediate circuit, and a second selected output voltage of the battery, which is the lowest voltage of those output voltages of the battery which are higher than the actual value of the voltage of the DC-voltage intermediate circuit, are then selected.

Owner:ROBERT BOSCH GMBH +1

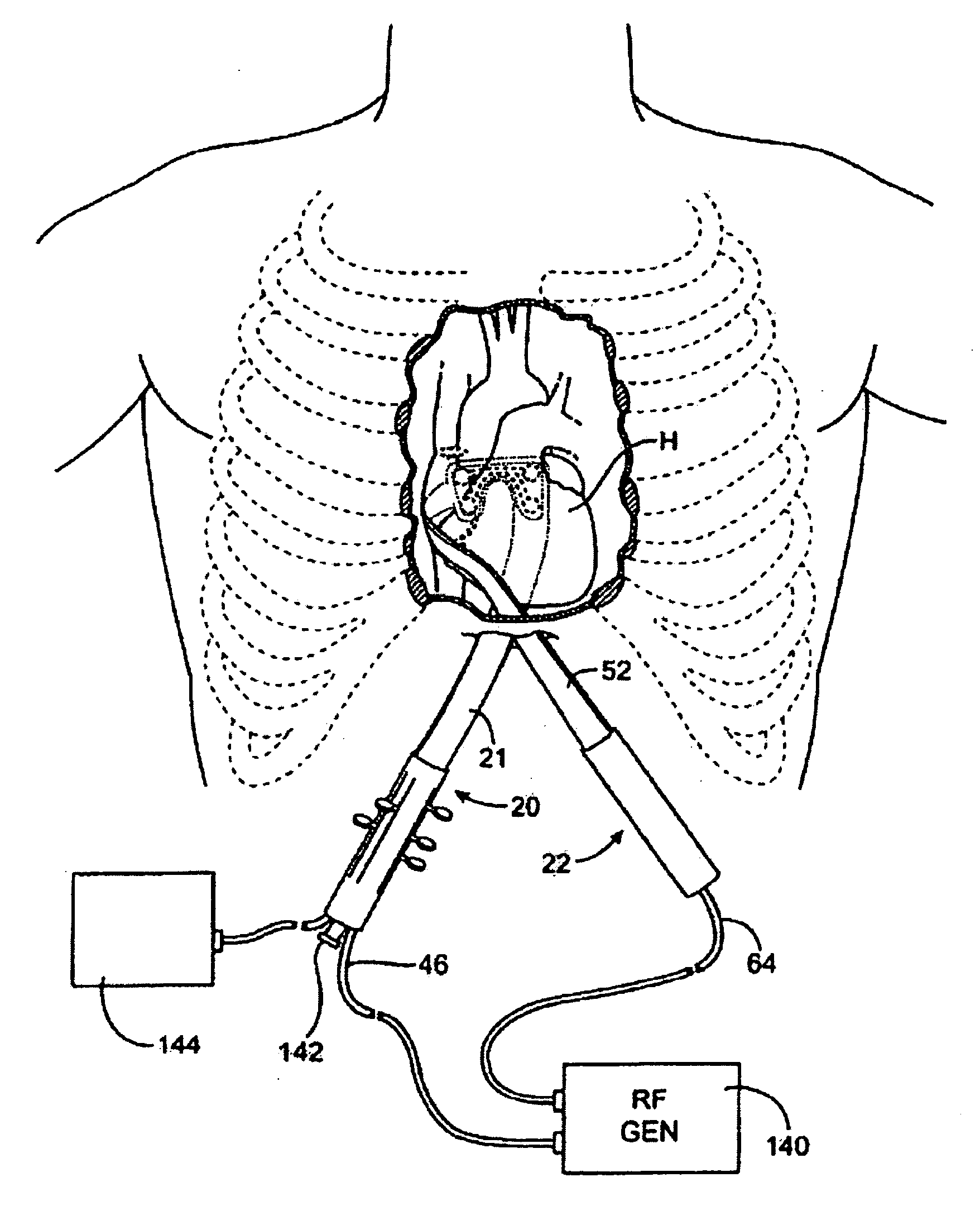

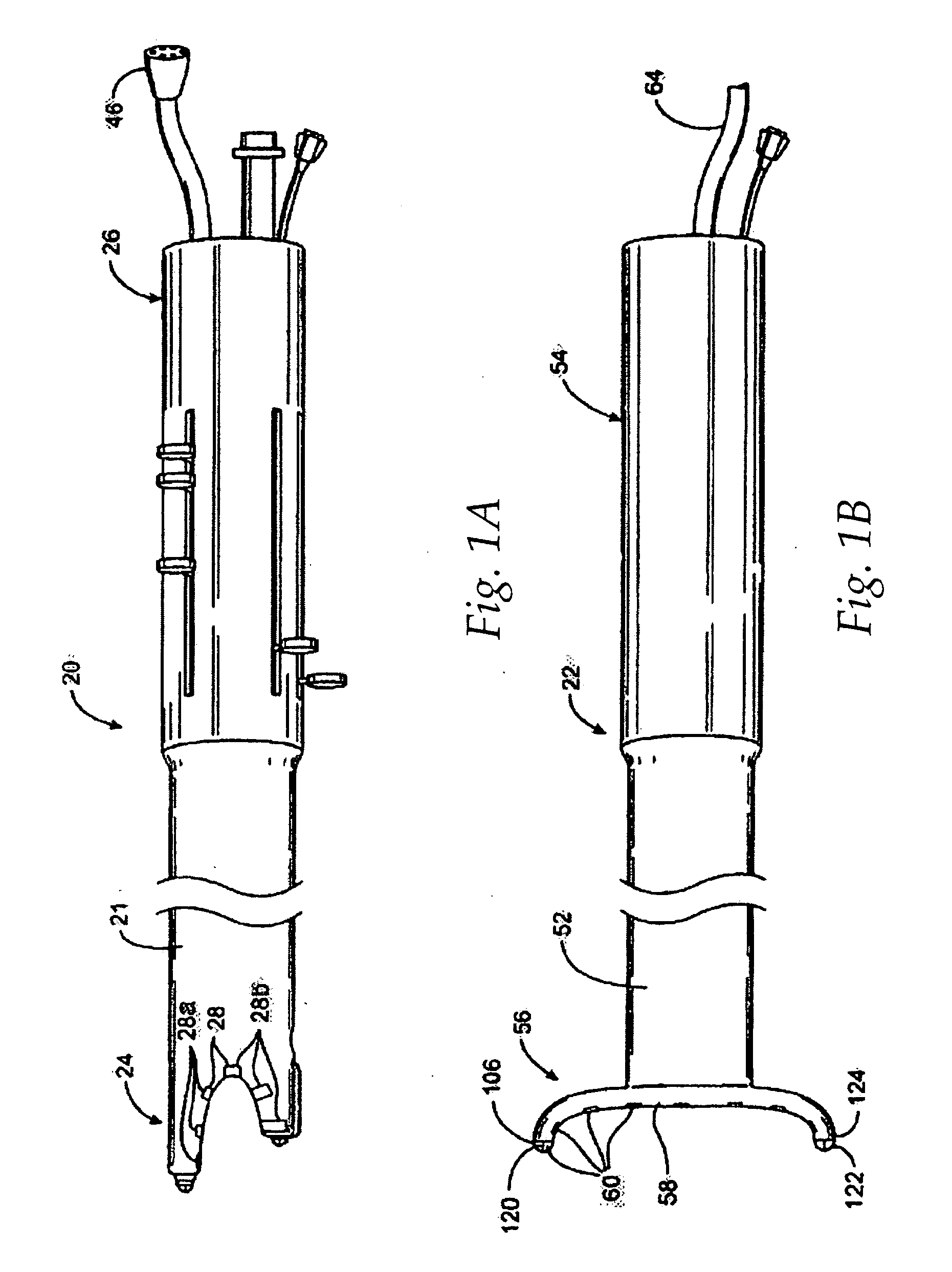

Switching methods and apparatus

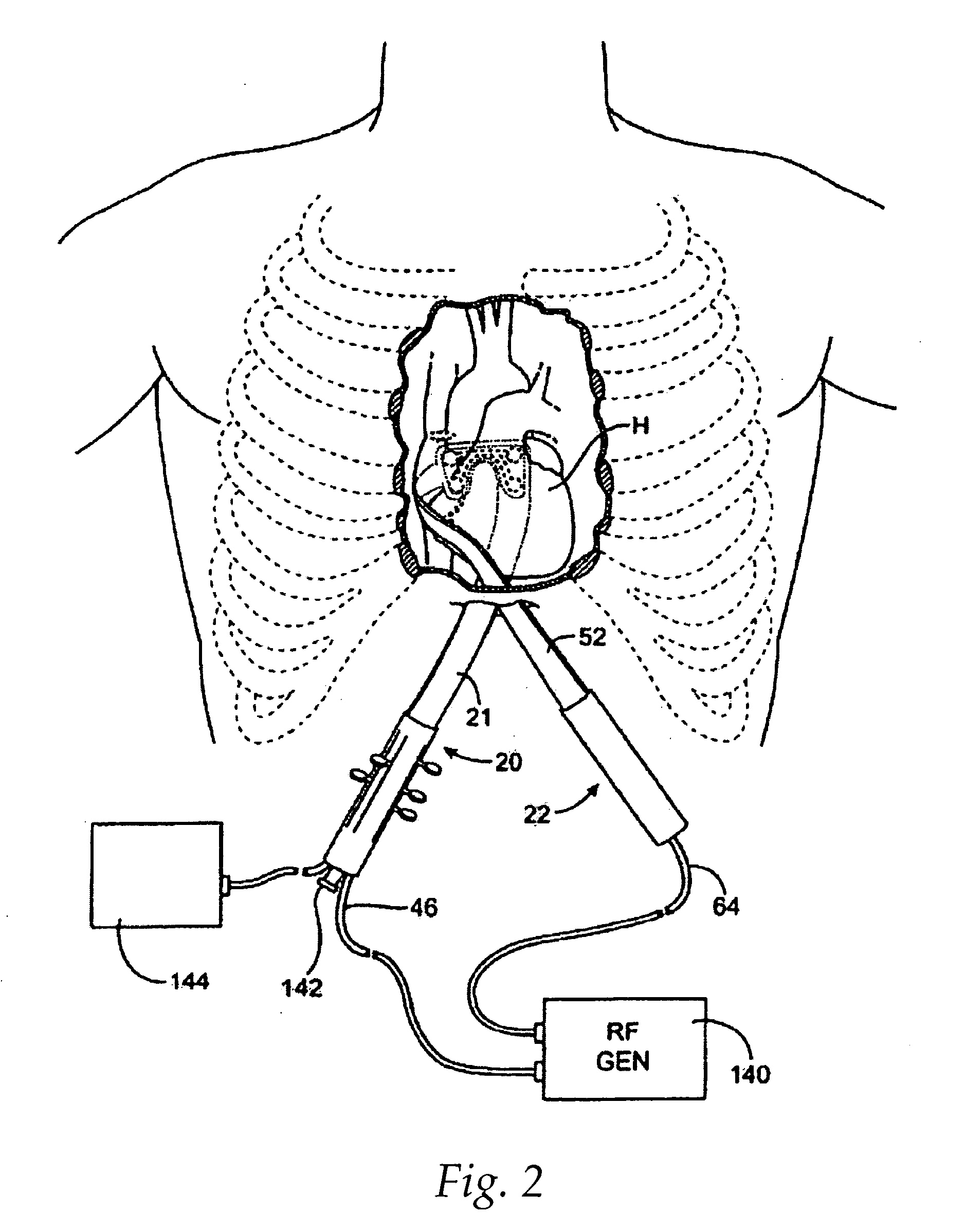

InactiveUS20080183169A1Constant rateQuick switchUltrasound therapyCatheterControl powerPower switching

Embodiments of the invention controlling power distribution in an ablation control apparatus or the like. In one embodiment, a power switching apparatus comprises a first switch assembly having an input end to receive a power input signal, the first switch assembly having a plurality of output channels; a second switch assembly coupled to the output channels of the first switch assembly; a plurality of power receiving members coupled to the second switch assembly; and a controller controlling the first switch assembly to selectively transmit the power input signal to the output channels one at a time in a cyclical manner according to a first switching rate. The controller controls the second switch assembly to transmit the power input signal from the output channels of the first switch assembly to one subset of the power receiving members at a time according to a second switching rate, so as to transmit the power input signal to a subset of power receiving members one power receiving member at a time within the subset of power receiving members according to the first switching rate.

Owner:ST JUDE MEDICAL ATRIAL FIBRILLATION DIV

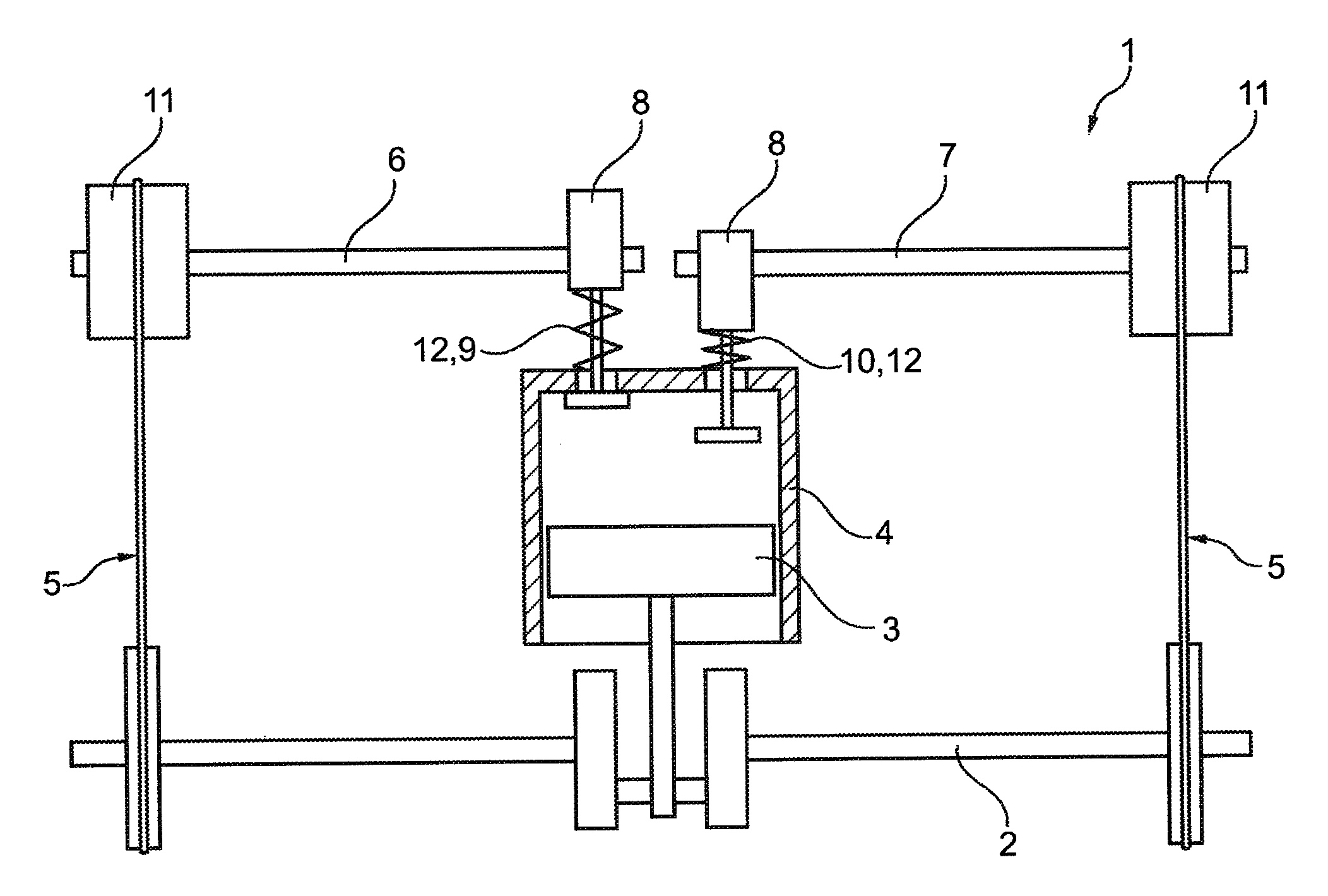

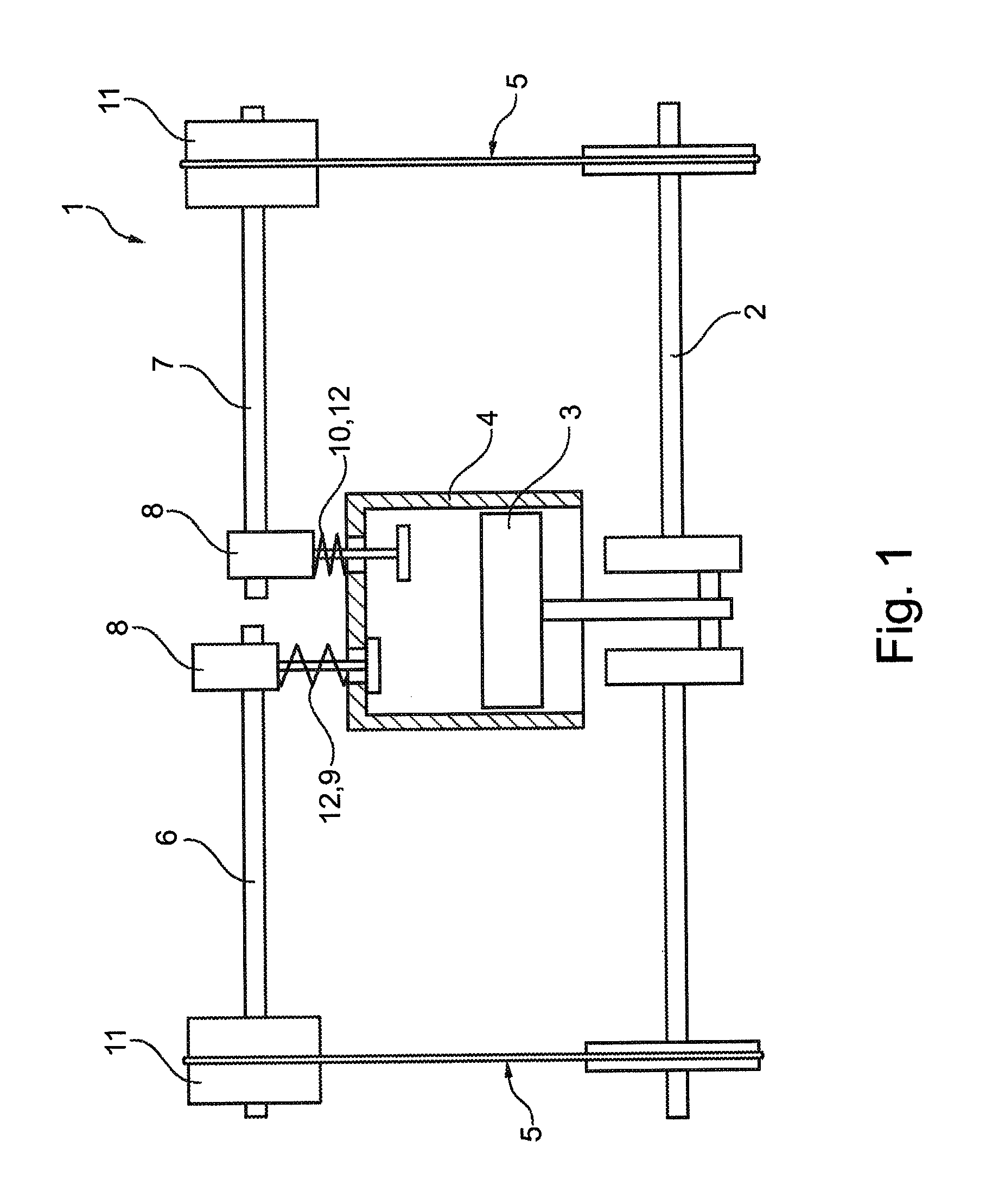

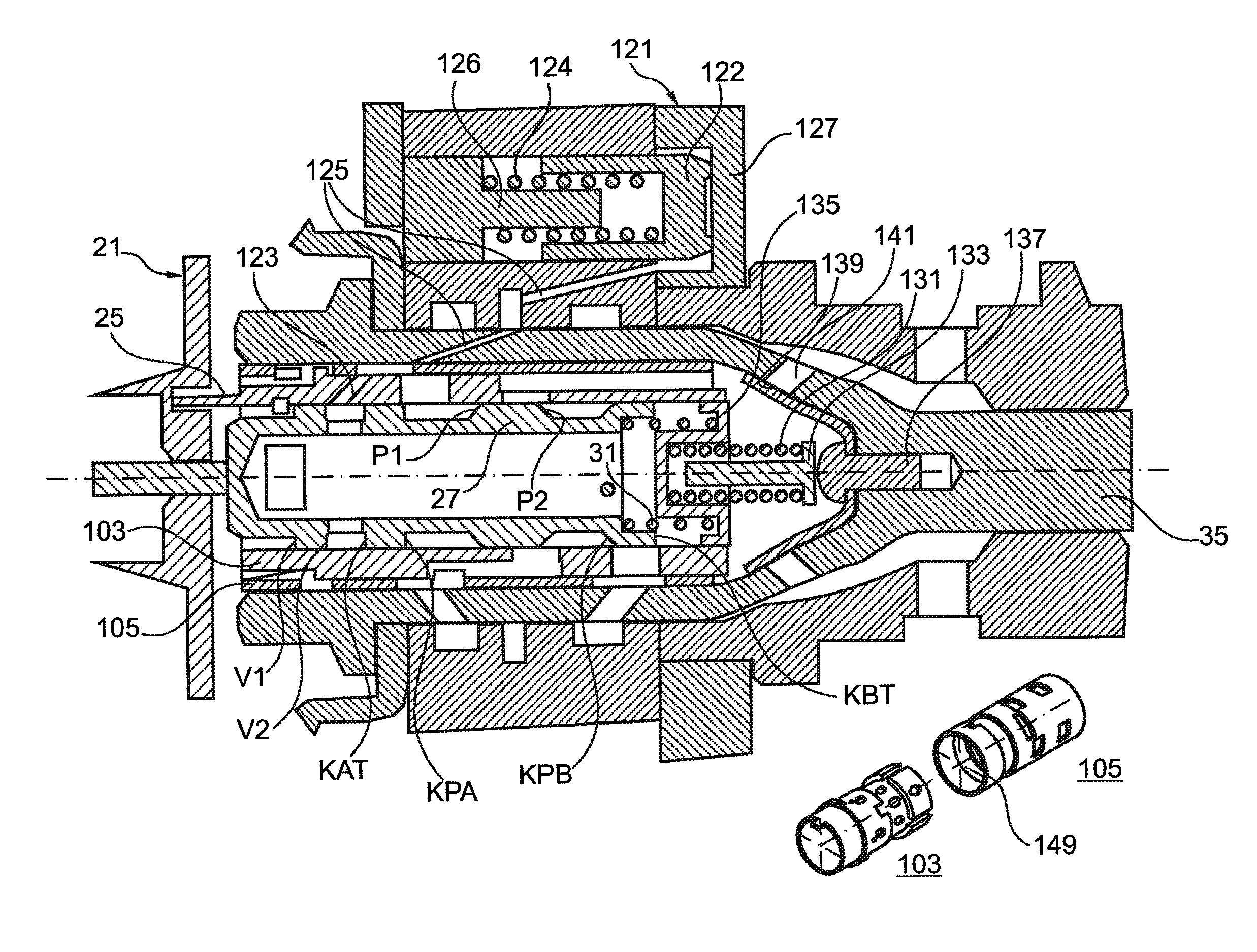

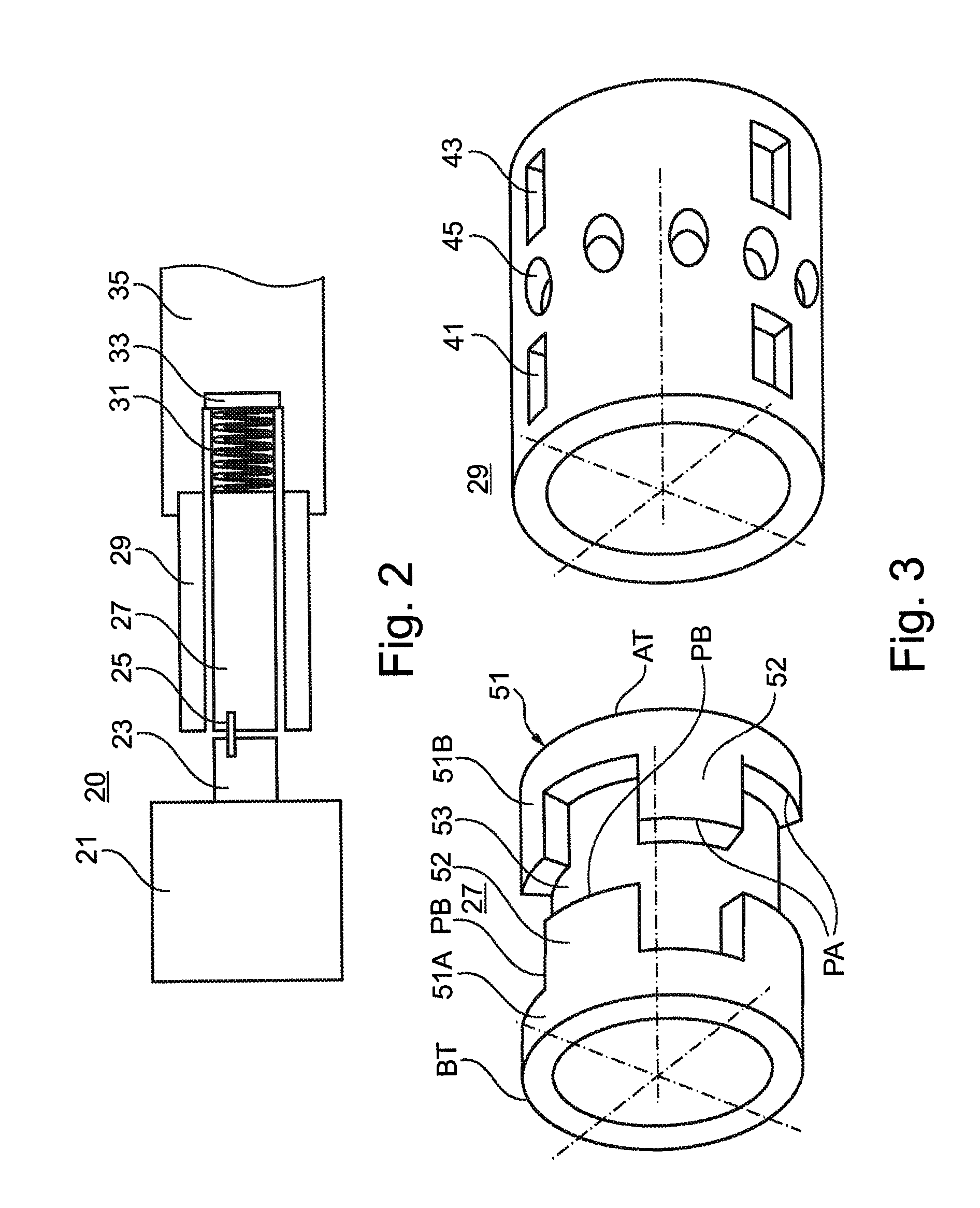

Device for variably adjusting the control times of gas exchange valves of an internal combustion engine

InactiveUS20120210961A1Easy to installAdd locking functionValve arrangementsMachines/enginesCombustionInternal combustion engine

A camshaft adjuster for actuating cylinder valves of a combustion engine, retardation torques are imparted back to the adjuster by the camshaft when cams are running on, and advance torques are imparted back to the adjuster by the camshaft when cams are running off, supply and removal of pressure medium is controllable by a control unit, a torque mode or pump mode is selectively adjusted by the control unit, and primarily camshaft torque is used in torque mode to build pressure in the first or second partial chamber, whereas pressure build-up in the first or second partial chamber primarily occurs in the pump mode via the pump. The control unit includes a control valve with inner and outer sleeves, and an adjustment direction and the pump or torque mode is adjustable by the control valve by the relative rotational position of the inner sleeve to the outer sleeve.

Owner:SCHAEFFLER TECH AG & CO KG

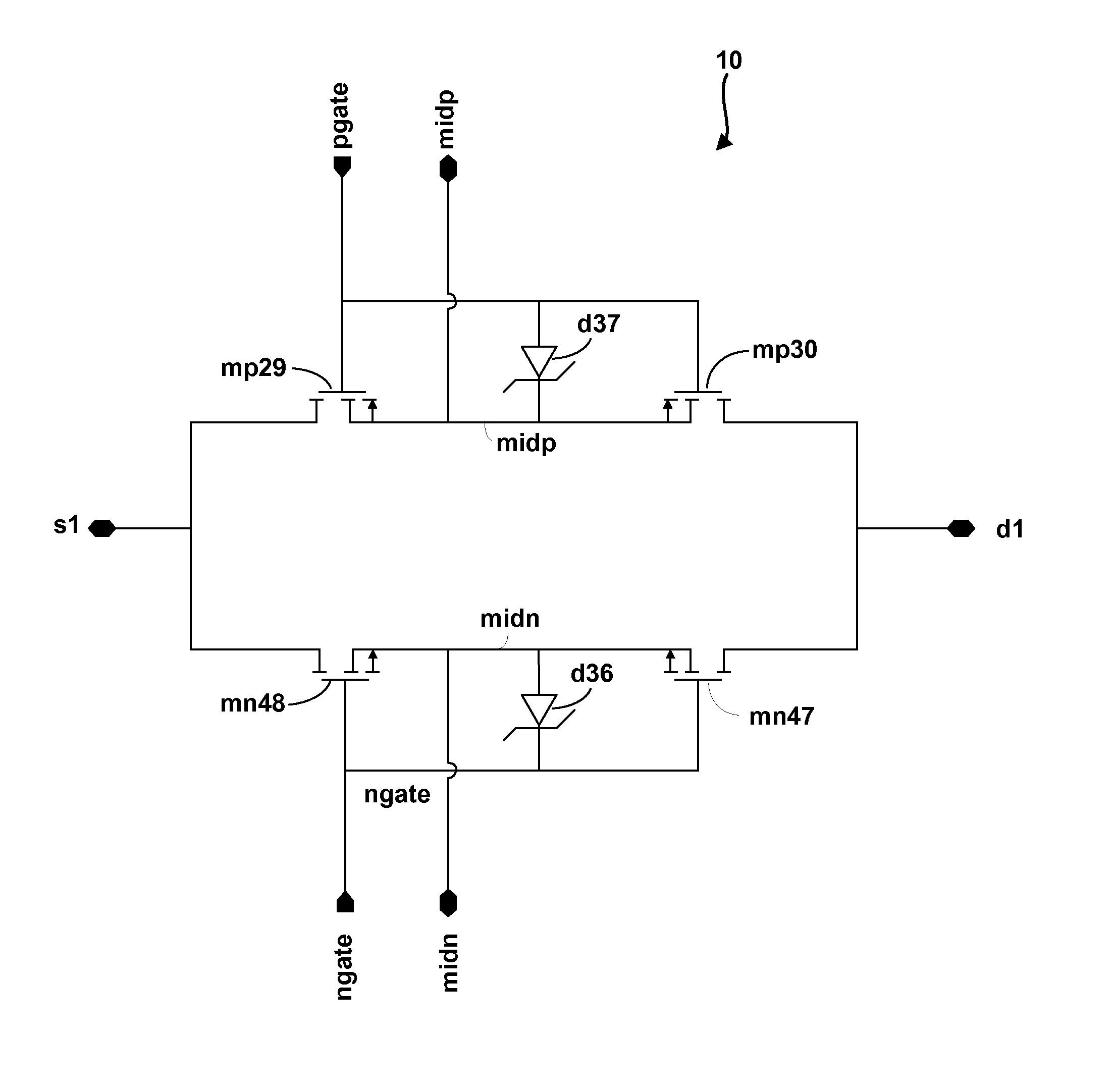

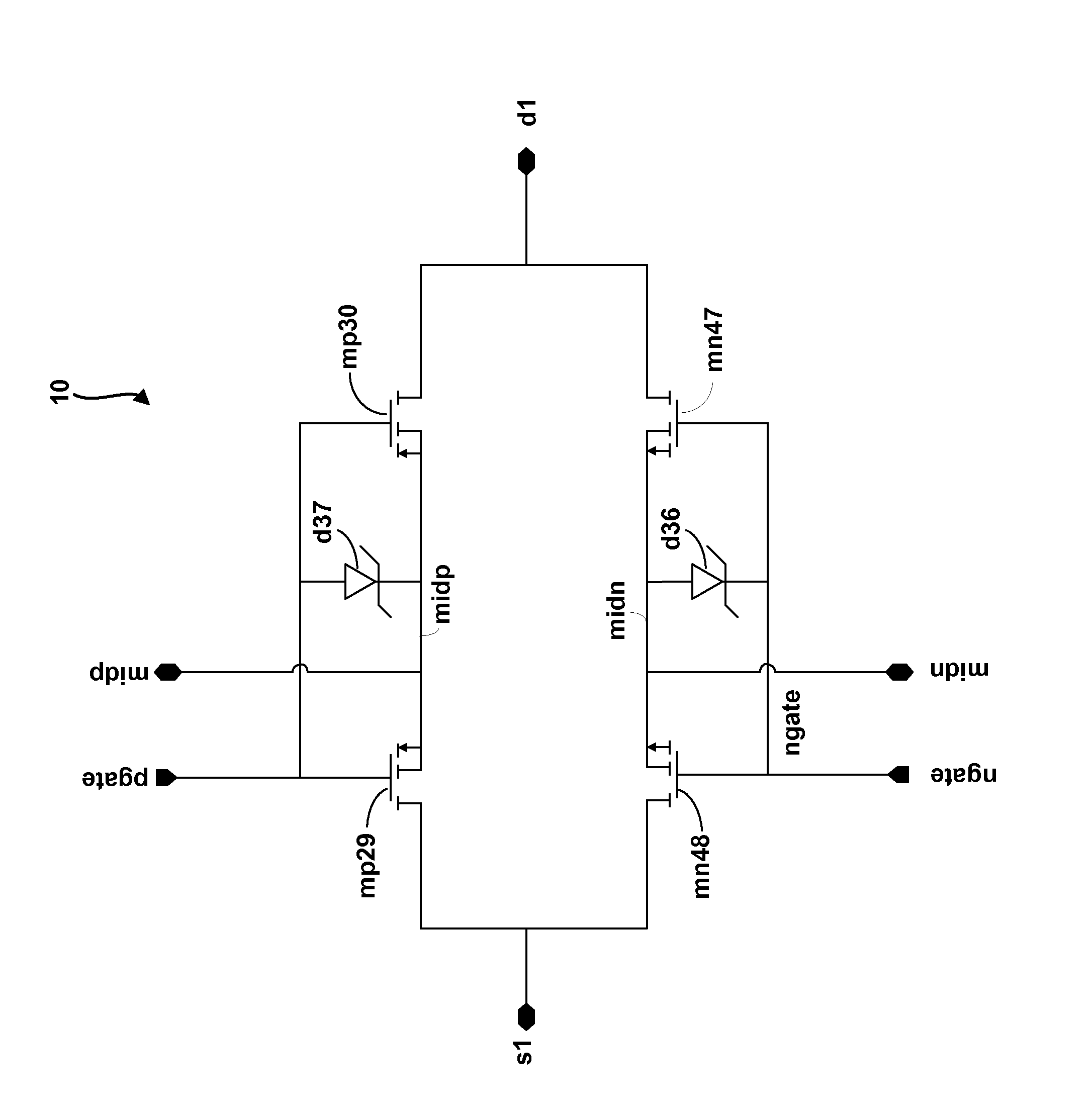

Bi-directional switch using series connected n-type mos devices in parallel with series connected p-type mos devices

ActiveUS20130248923A1High supply currentReduce switching speedElectronic switchingSemiconductor devicesEngineeringEngineering physics

A bi-directional switch circuit includes a pair of N-type MOS devices connected in series with a common source terminal, and a pair of P-type MOS devices connected in series with a common source terminal. The series connected N-type devices are connected in parallel with the series connected P-type devices in a configuration that includes a first input / output (I / O) point of the switch circuit being connected to a drain of a first one of the N-type devices and a drain of a first one of the P-type devices. The parallel configuration also includes a second I / O point of the switch circuit being connected to a drain of a second one of the N-type devices and a drain of a second one of the P-type devices.

Owner:ANALOG DEVICES INC

Device for variably adjusting the control times of gas exchange valves of an internal combustion engine

InactiveUS8733305B2Add locking functionReduce switching speedValve arrangementsMachines/enginesCombustionExternal combustion engine

A camshaft adjuster for actuating cylinder valves of a combustion engine, retardation torques are imparted back to the adjuster by the camshaft when cams are running on, and advance torques are imparted back to the adjuster by the camshaft when cams are running off, supply and removal of pressure medium is controllable by a control unit, a torque mode or pump mode is selectively adjusted by the control unit, and primarily camshaft torque is used in torque mode to build pressure in the first or second partial chamber, whereas pressure build-up in the first or second partial chamber primarily occurs in the pump mode via the pump. The control unit includes a control valve with inner and outer sleeves, and an adjustment direction and the pump or torque mode is adjustable by the control valve by the relative rotational position of the inner sleeve to the outer sleeve.

Owner:SCHAEFFLER TECH AG & CO KG

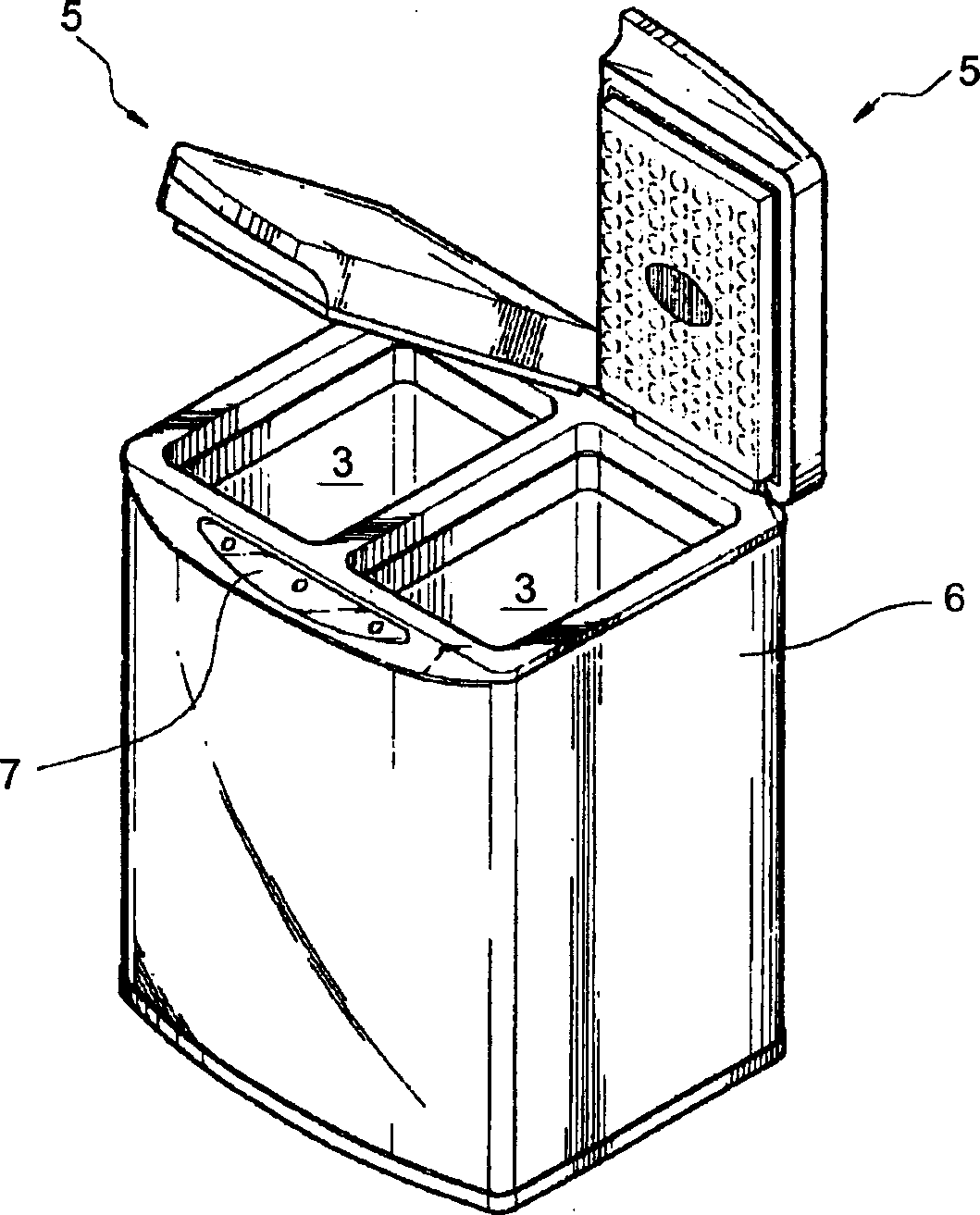

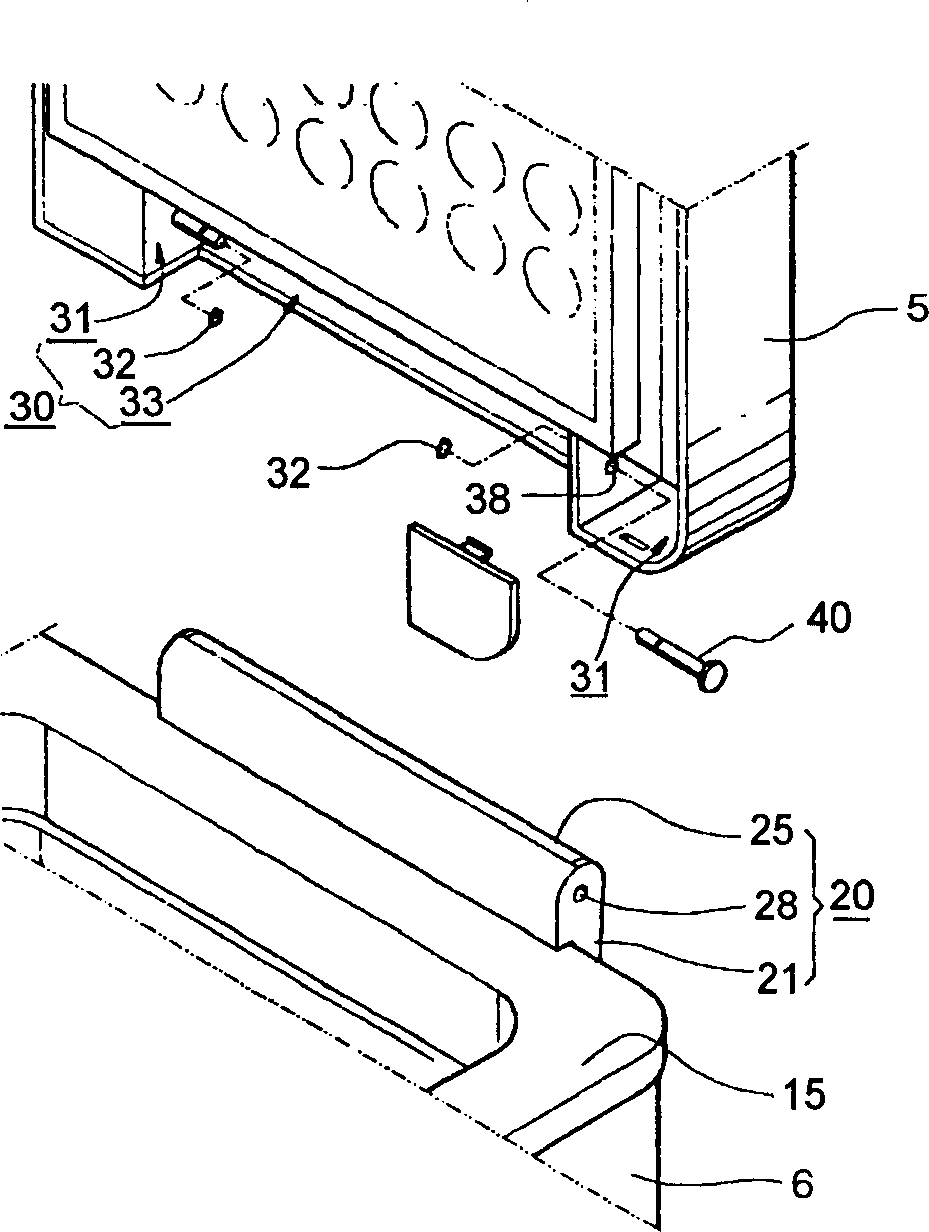

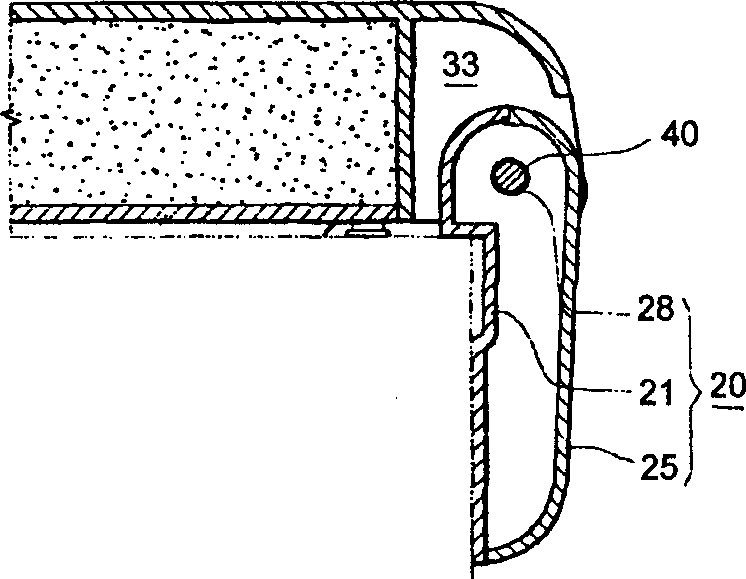

Door hinge assembly for pickles storage case

InactiveCN1369608AReduce switching speedSmooth switchingLighting and heating apparatusFood preservationEngineeringMechanical engineering

The present invention provides a hinge assembly for the door of a pickle storage box, which opens and closes the door of a storage compartment of the pickle storage box and is mounted on the upper surface of the box body. This hinge assembly includes: a cover plate 100 fixed on the box body 6; an elastic device; a support plate 86 that supports the elastic device; an adjustment plate 84 that adjusts the reset elastic force; and is connected to the above-mentioned elastic device to support the space between the pressure components 65. The force supporting member 90 and the like are inserted into the hinge housing 70 and are connected to the above-mentioned pressing member, and are integrally connected to the rotating member 50 and the like fixed on the door 5 . It can prevent the door from being impacted when opening and closing, thereby preventing damage to the door.

Owner:MANDO CLIMATE CONTROL

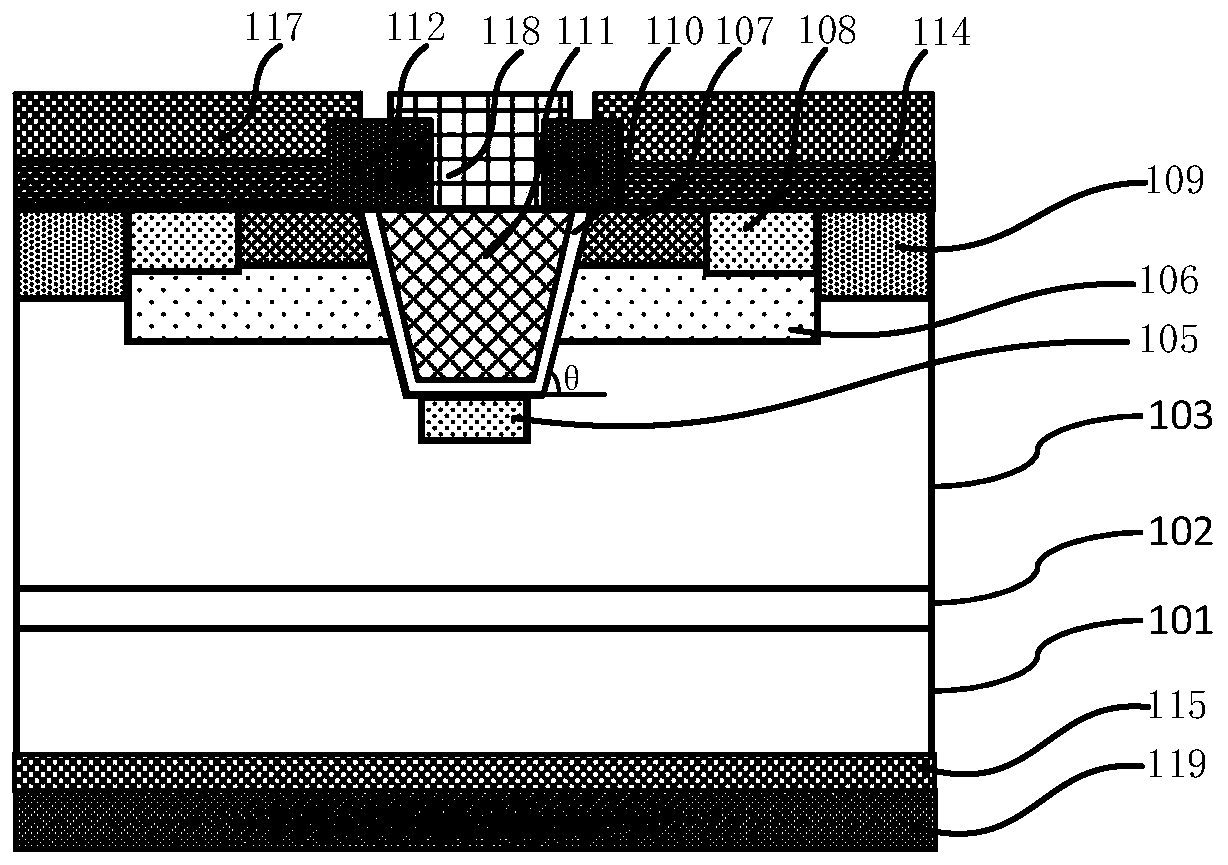

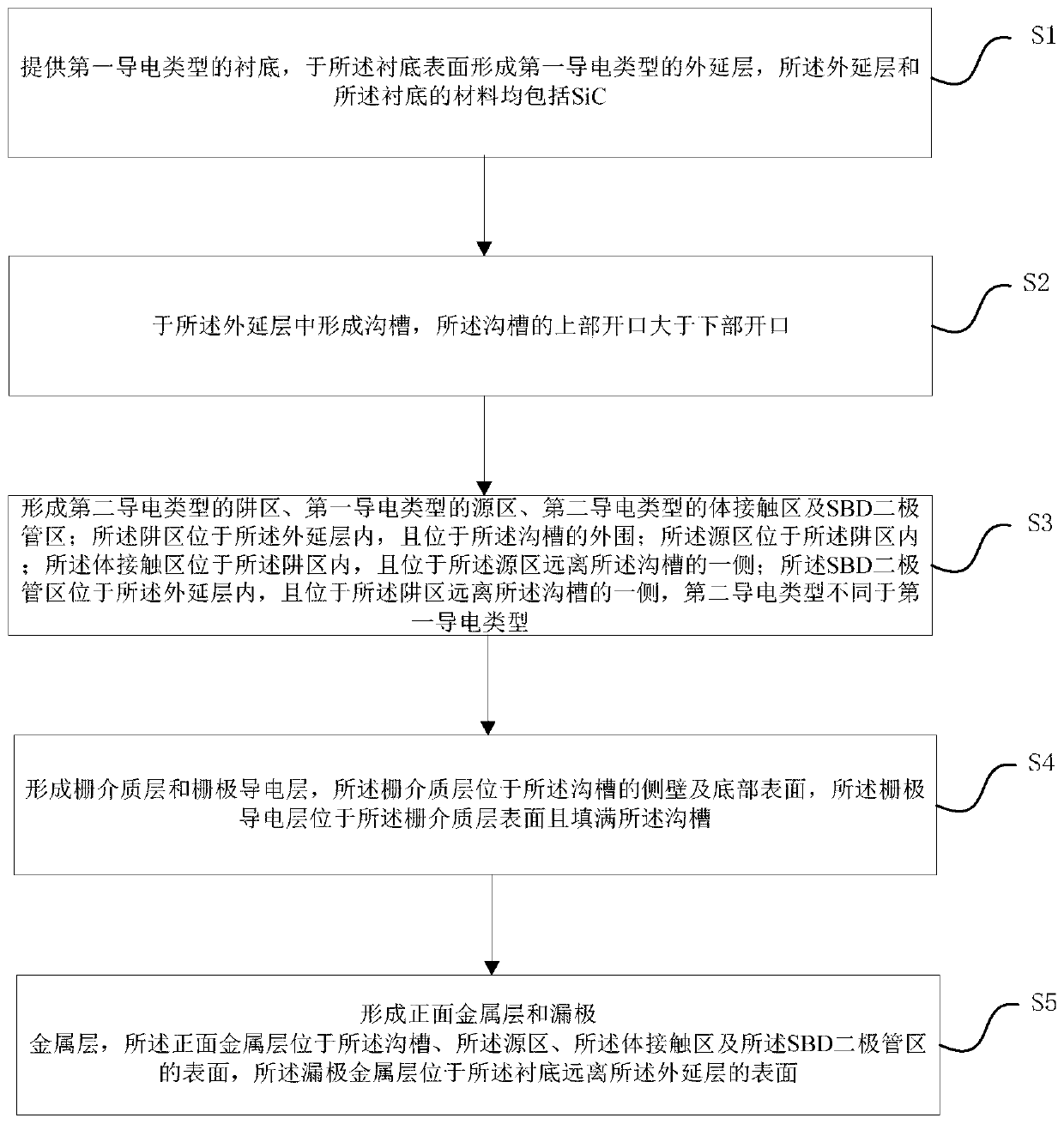

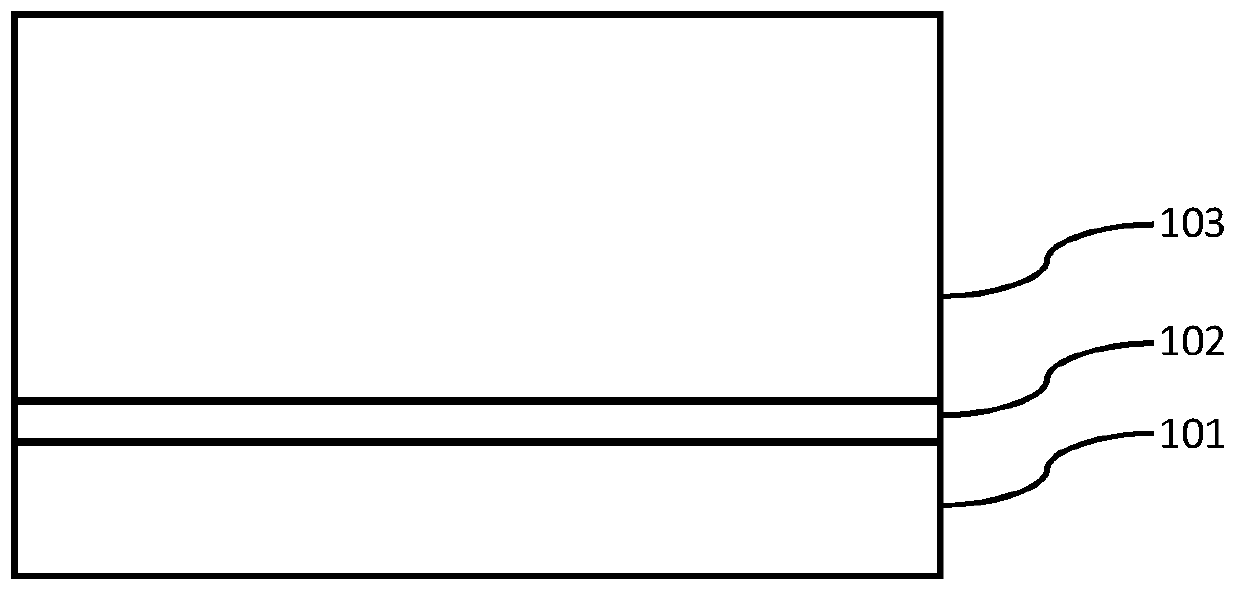

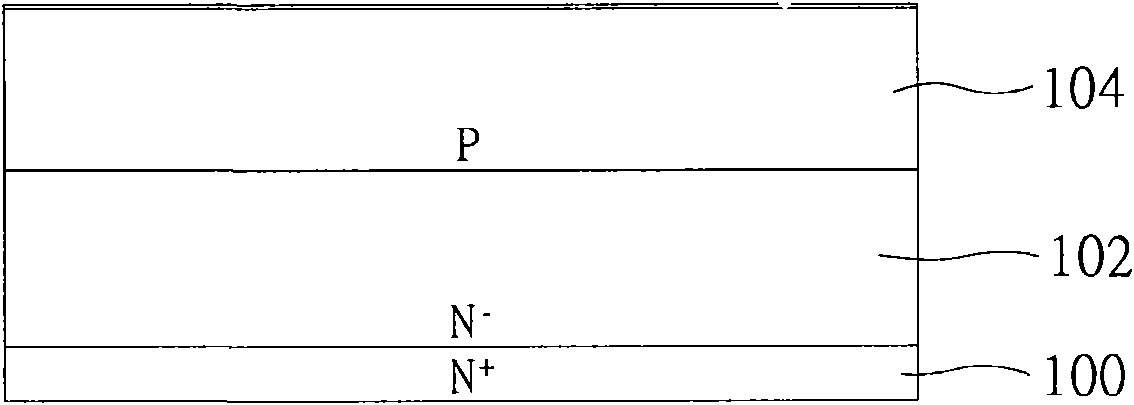

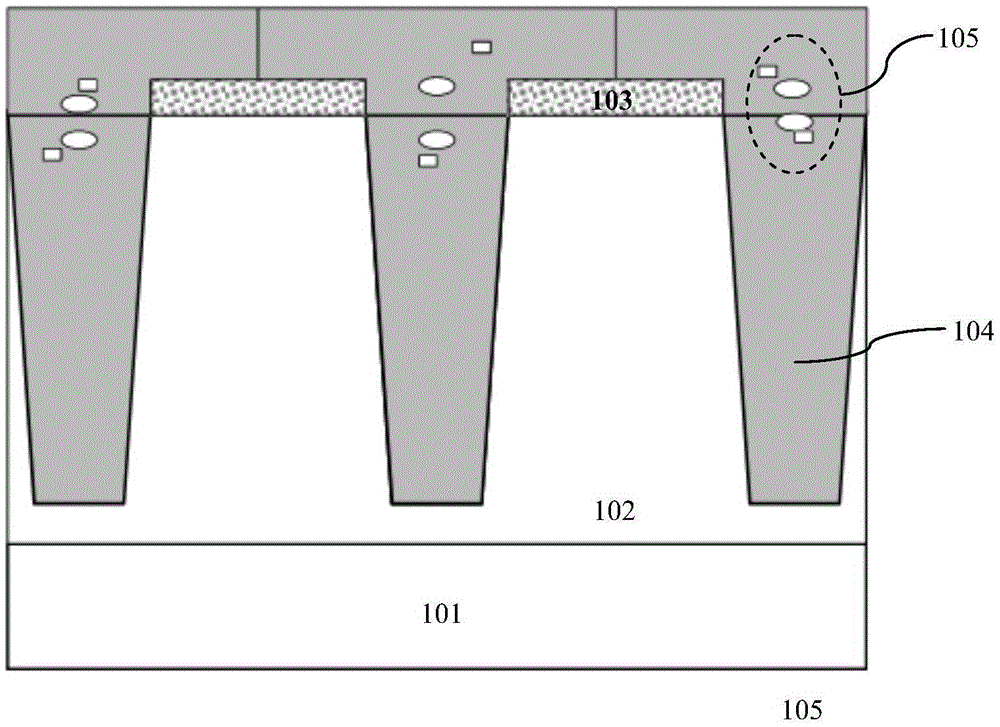

SiC MOSFET power device and preparation method thereof

InactiveCN110350035AReduced on-resistance and on-power dissipationReduce input capacitanceSemiconductor devicesCapacitanceMOSFET

The invention provides a SiC MOSFET power device and a preparation method thereof. The device comprises a substrate, an epitaxial layer, a trench, a gate dielectric layer, a gate conductive layer, a well region, a source region, a body contact region, an SBD diode region, a front metal layer and a drain metal layer, wherein the epitaxial layer is positioned on the surface of the substrate; the trench is located in the epitaxial layer, and the upper opening of the trench is larger than the lower opening of the trench; the gate dielectric layer is positioned on the side wall and the bottom surface of the trench; the gate conductive layer is located on the surface of the gate dielectric layer and fills the trench; the well region is located in the epitaxial layer and is located on the periphery of the trench; the source region is located in the well region; the body contact region is located in the well region; the SBD diode region is located in the epitaxial layer. According to the device, the structure of a traditional SiC MOSFET power device is optimized, so that the conduction resistance and the conduction power consumption of the device can be reduced, and the device can also have a relatively low input capacitance, the switch speed of the device is increased, the power consumption of the switch is reduced, the reverse conducting capability of the device is improved, and theoverall size and the economic cost of the power module are reduced. The structure and the method are simple, and a wide application prospect is achieved.

Owner:上海功成半导体科技有限公司

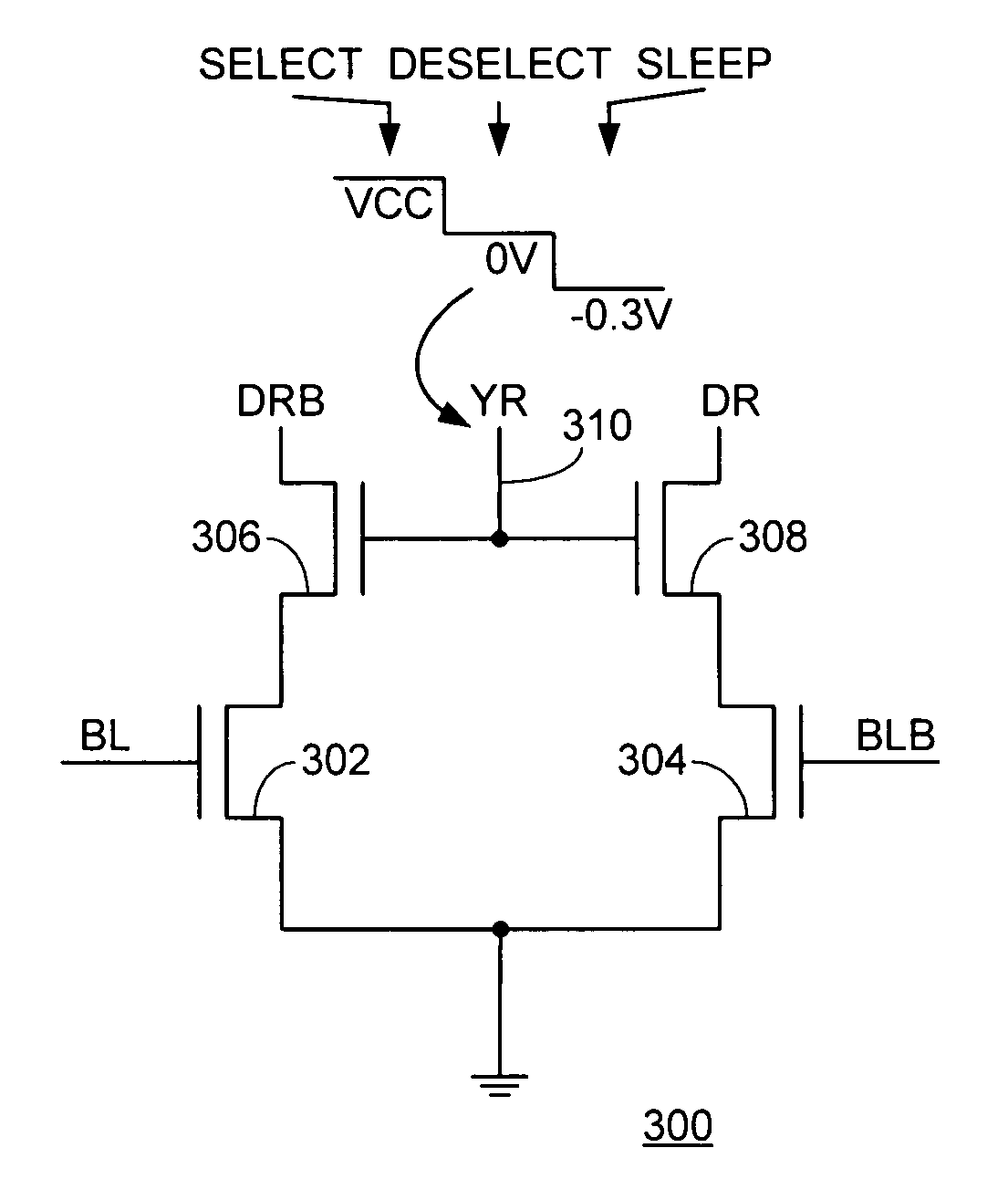

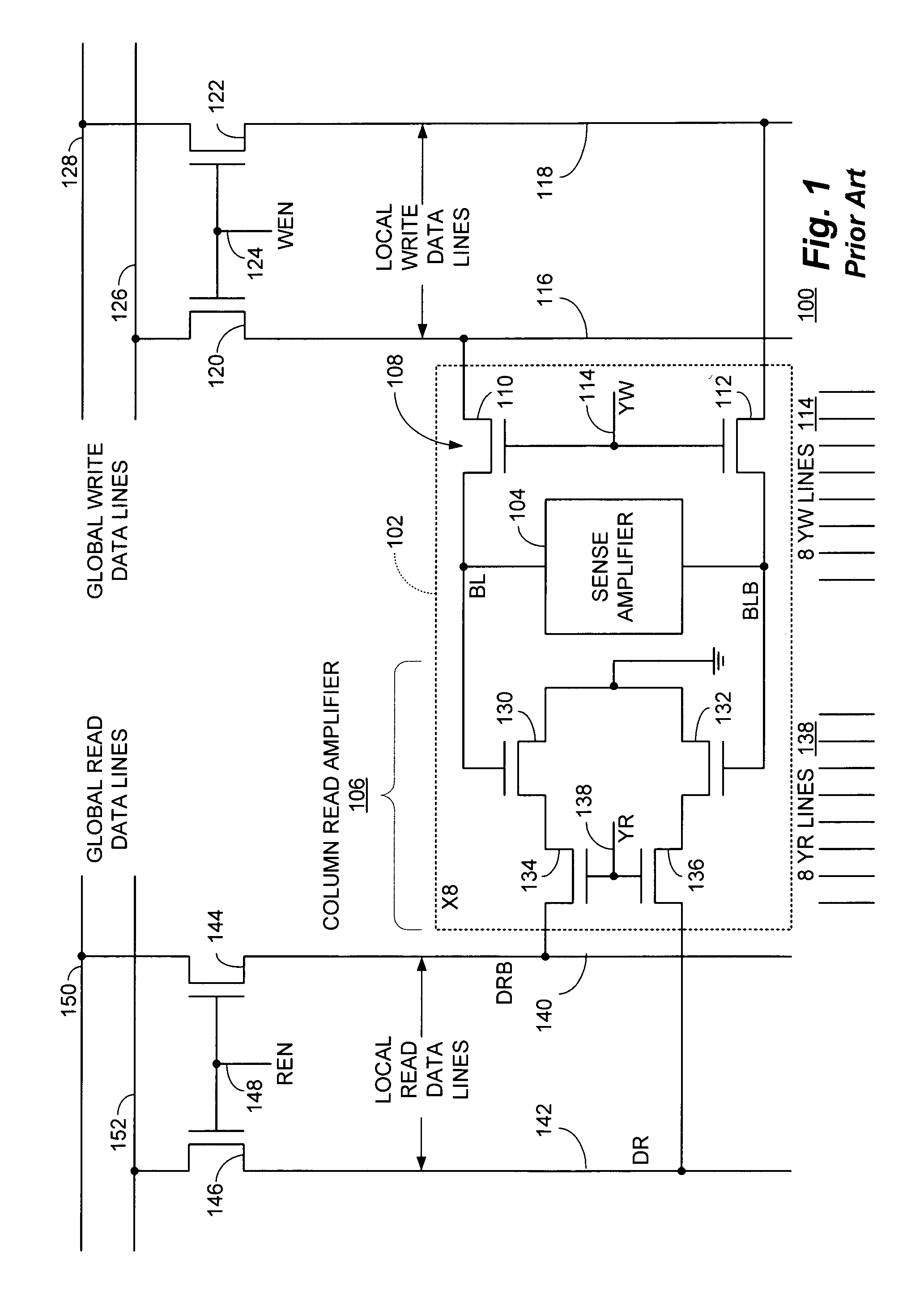

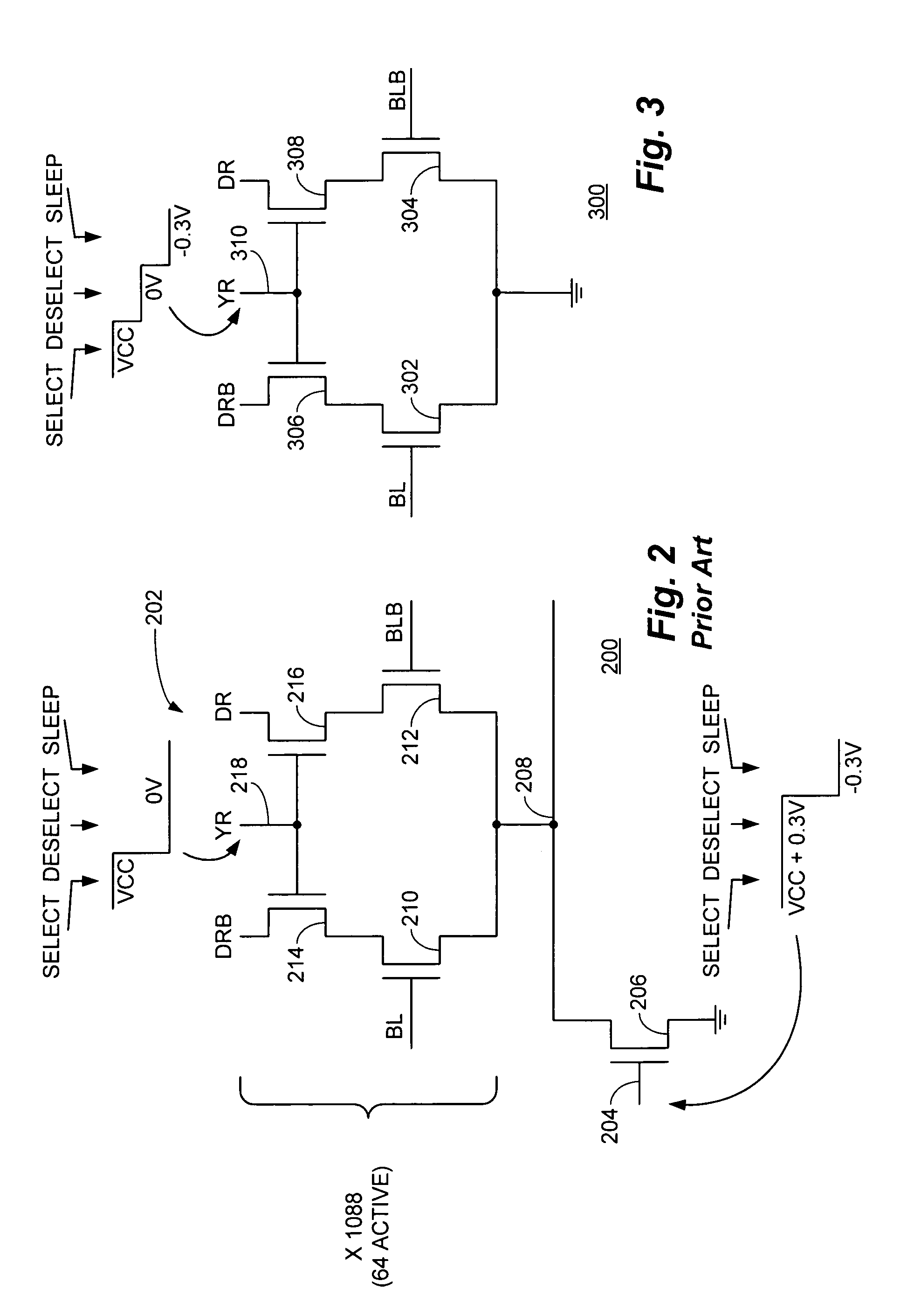

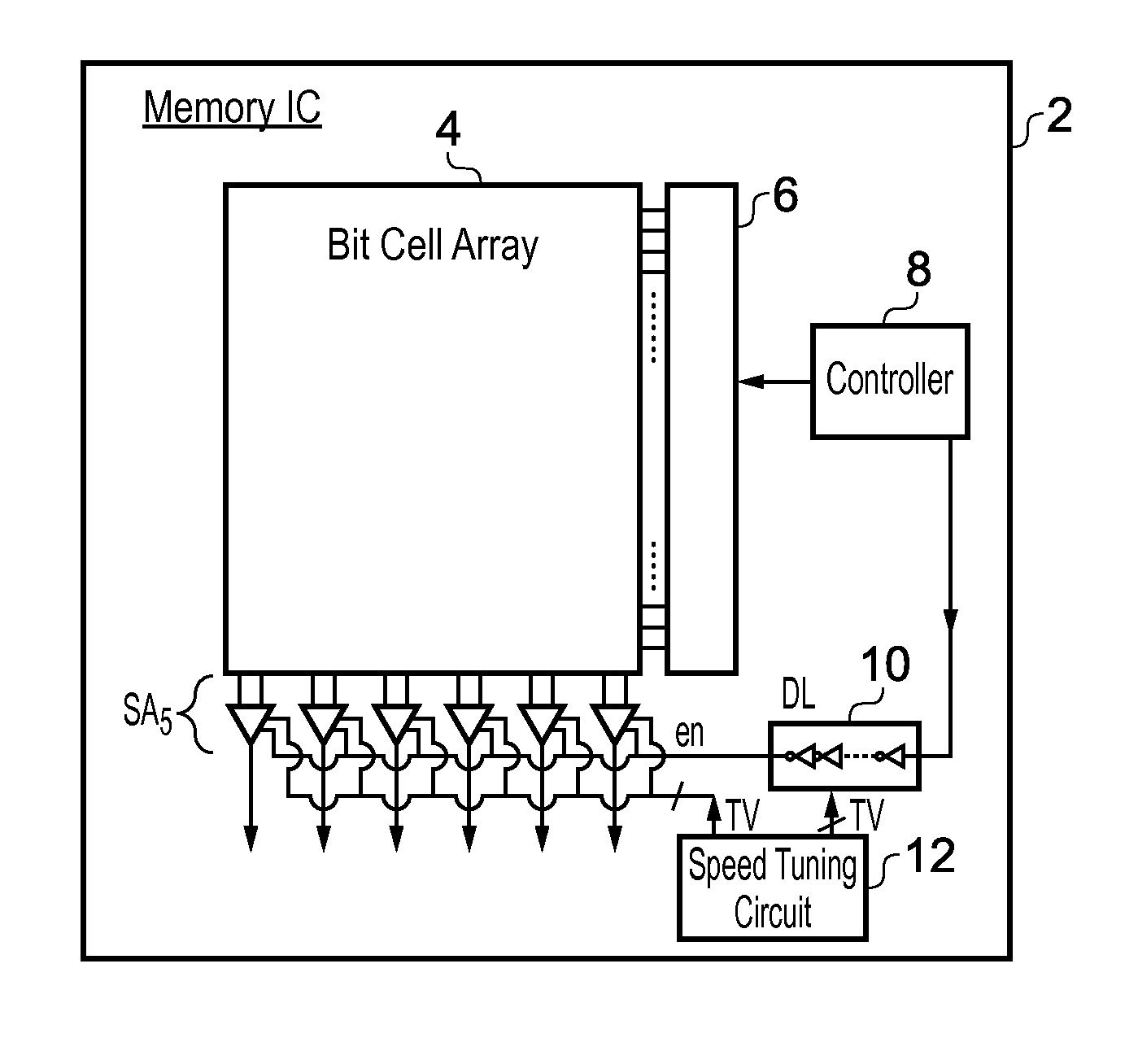

Column read amplifier power-gating technique for integrated circuit memory devices and those devices incorporating embedded dynamic random access memory (DRAM)

ActiveUS6990029B2Reduce switching speedSave areaDigital storageStatic random-access memoryAudio power amplifier

Owner:SONY CORP

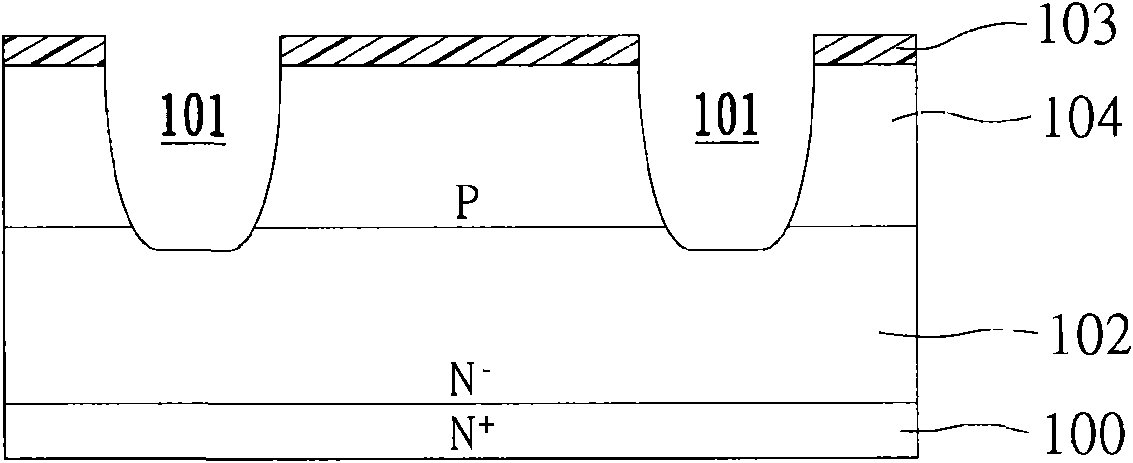

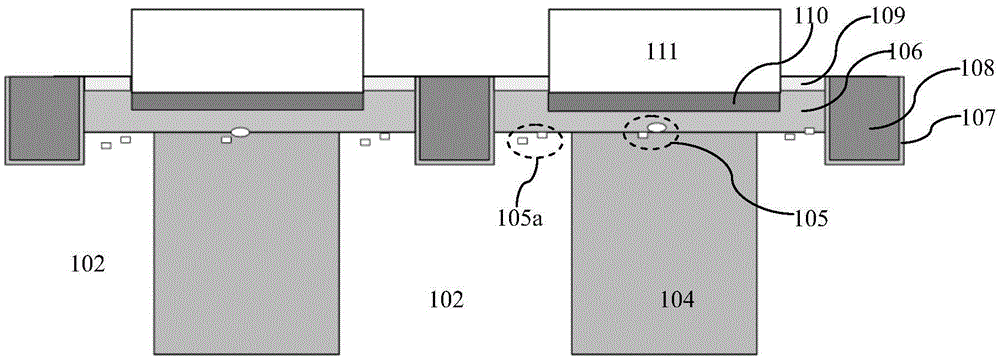

Production method of groove-type power semiconductor with low grid charge and structure thereof

InactiveCN101847603AReduce overlap areaReduce switching speedTransistorSemiconductor/solid-state device manufacturingBody areaMetal silicide

The invention discloses a production method of a groove-type power semiconductor with a low grid charge and a structure thereof. The production method is characterized by comprising the following steps of: providing a first conductive type semiconductor substrate and forming a first conductive epitaxial layer and a second conductive type body area on the first conductive type semiconductor substrate; and forming a plurality of grooves; forming a first insulating layer on the second conductive type body area and on the lateral surface of each groove; forming a polysilicon side wall on the sidewall of each groove and exposing one part of the bottom surface of the groove; filling a dielectric structure into each groove; filling polysilicon above the dielectric structure of each groove; forming a metallic silicide on the polysilicon, wherein the metallic silicide is a first phase composition; and converting the metallic silicide from the first phase composition into a second phase composition. The invention can improve the switching speed and achieve the effect of reducing the switching loss.

Owner:NIKO SEMICON

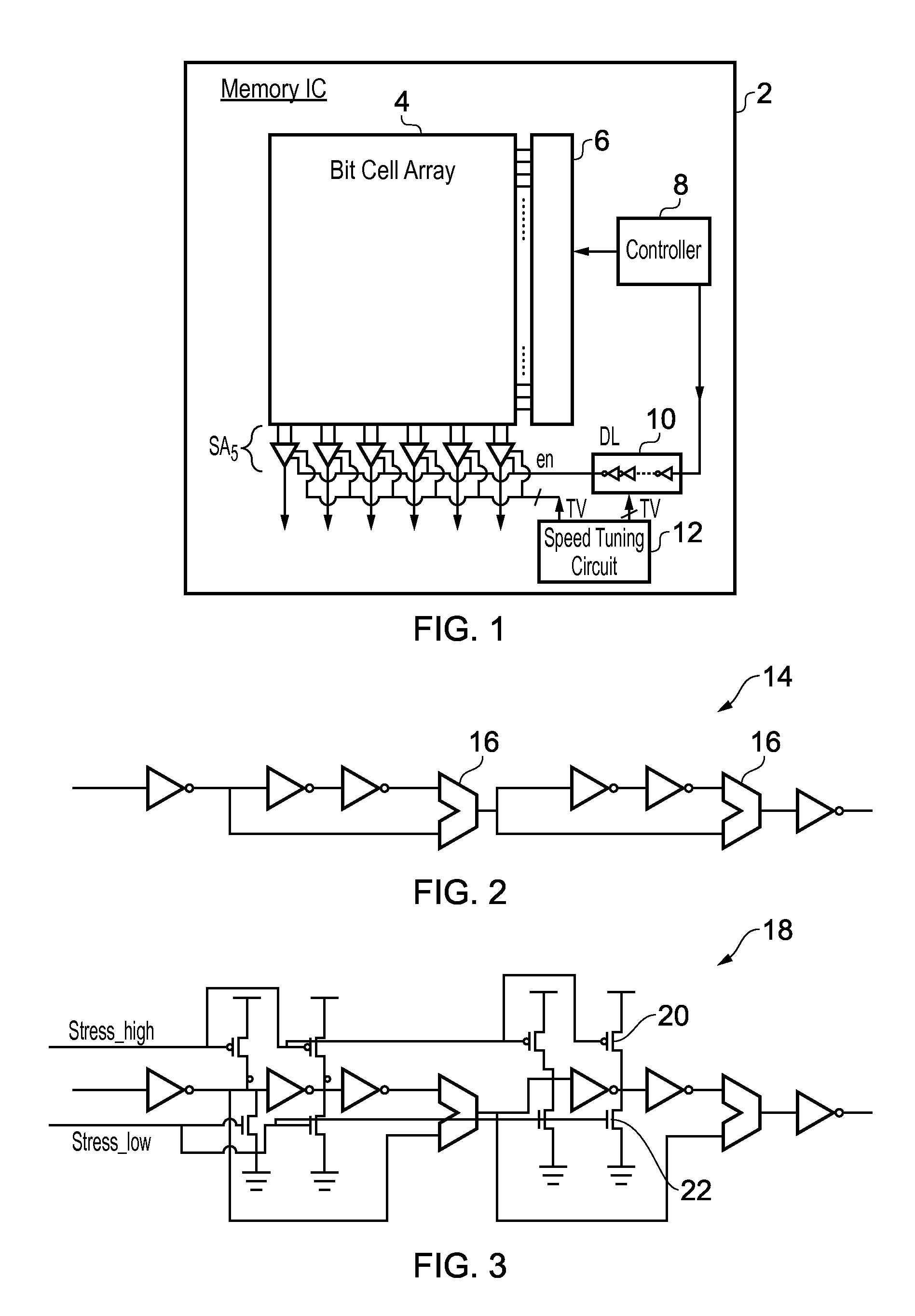

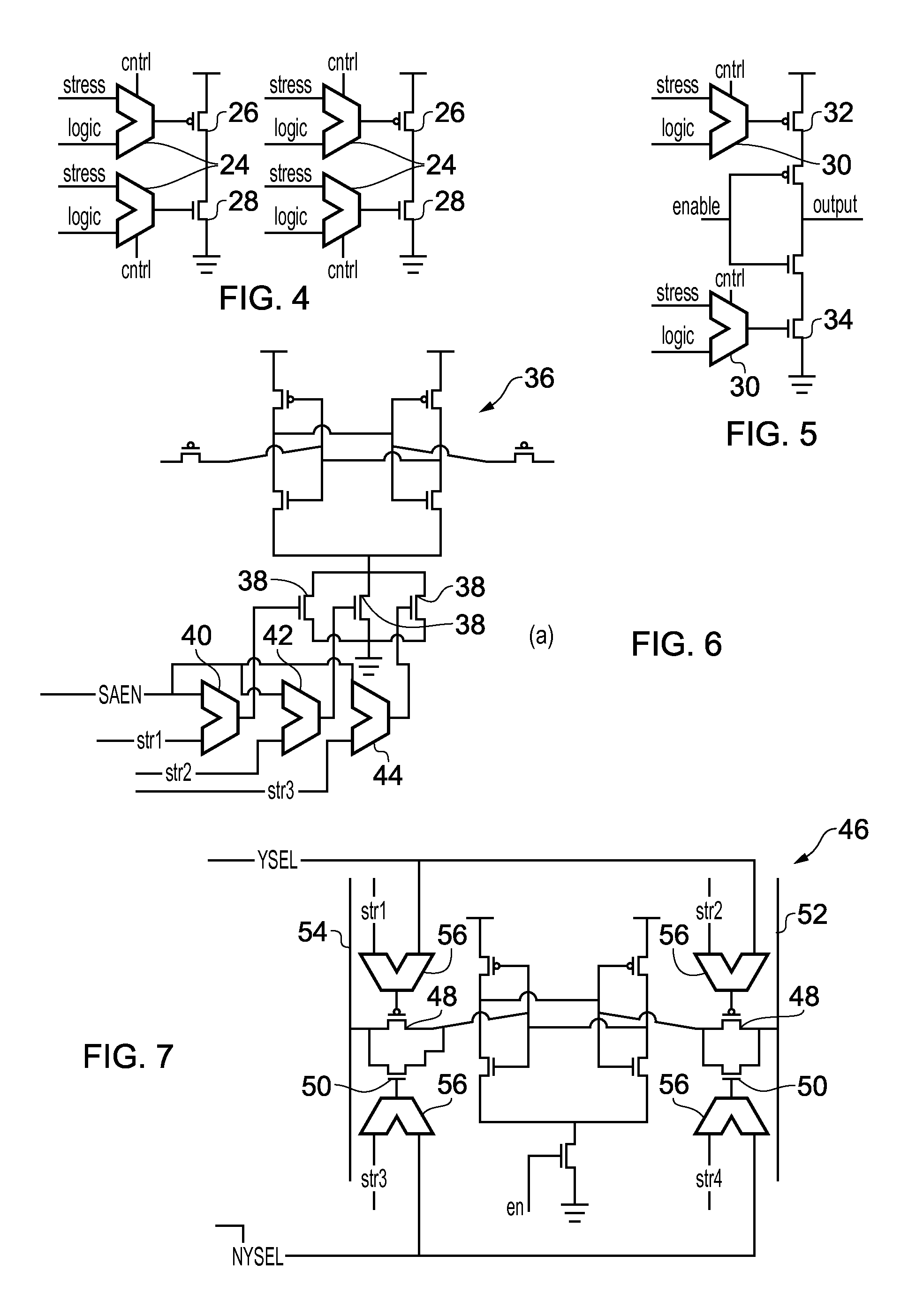

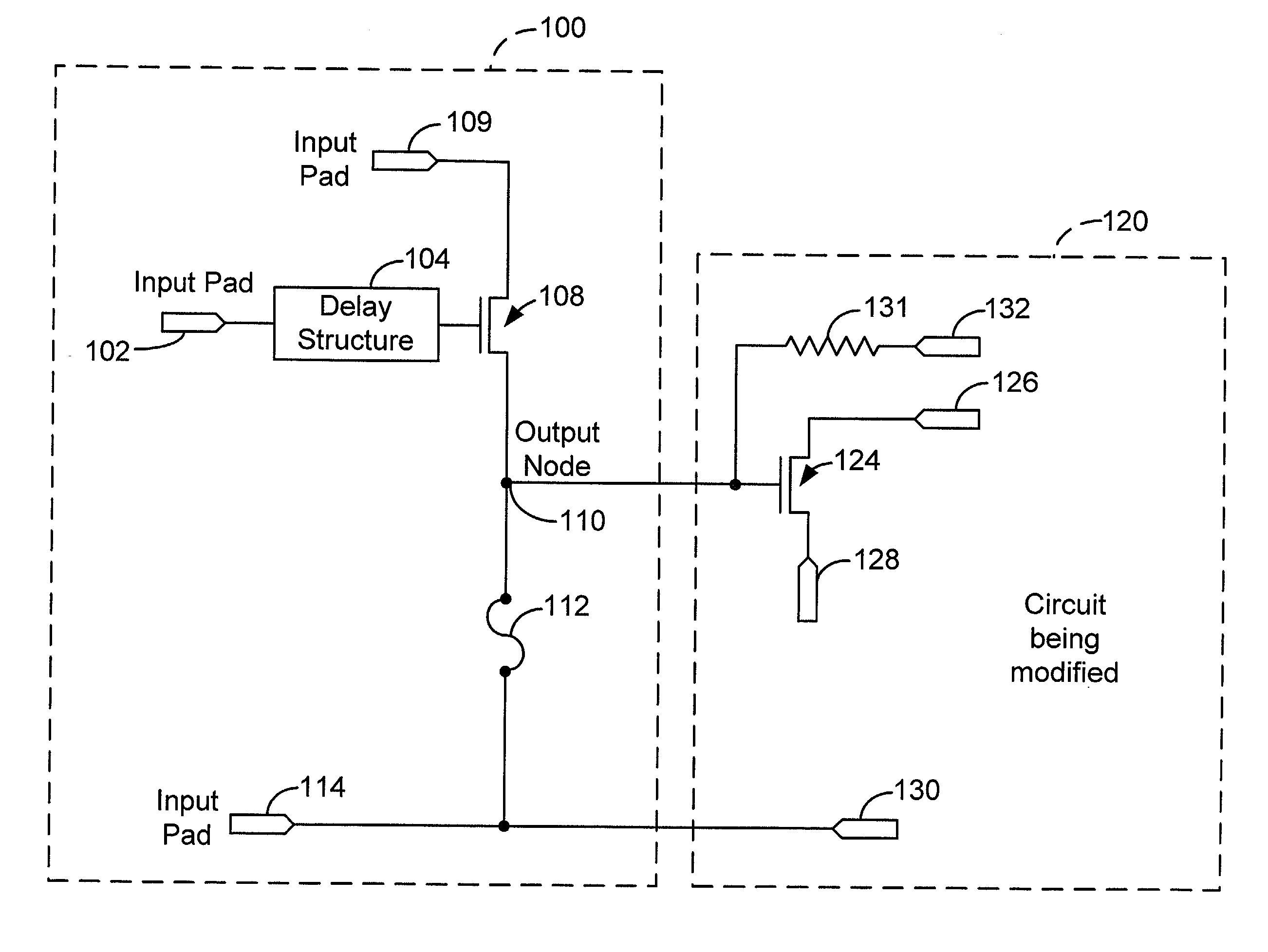

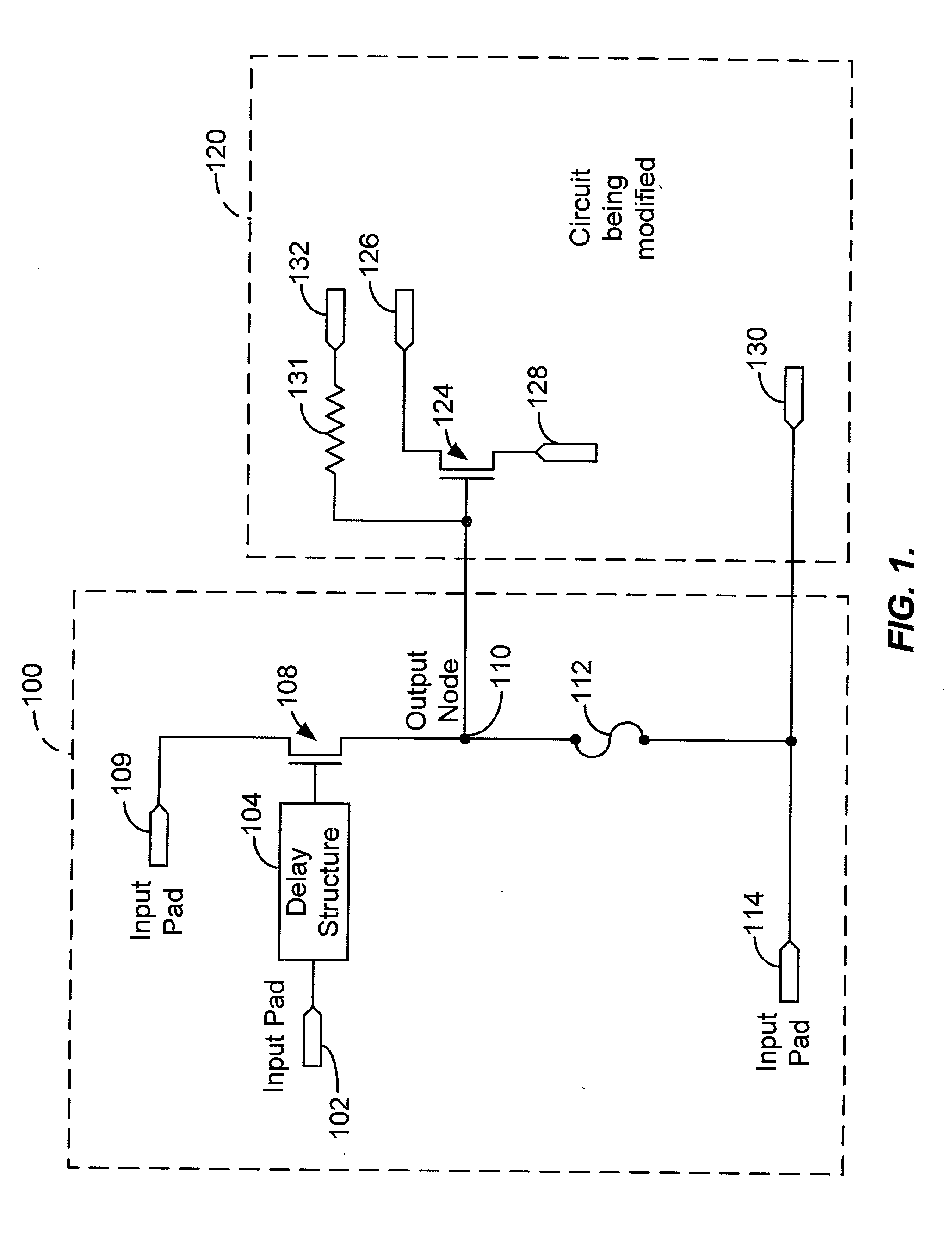

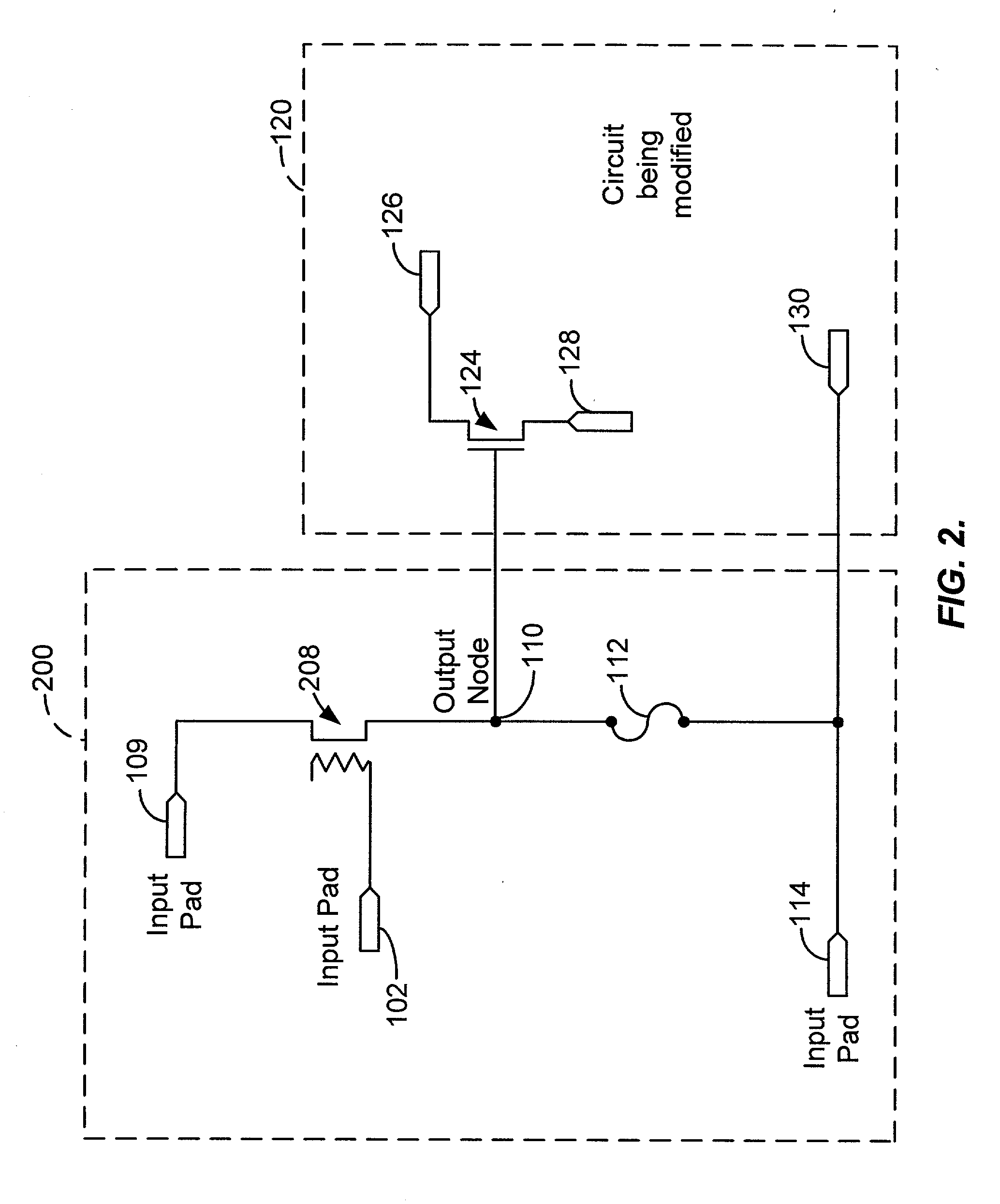

Post fabrication tuning of an integrated circuit

ActiveUS9374072B2Shorten speedReduce switching speedSingle output arrangementsVoltage rangeNormal range

An integrated circuit 2 includes a transistor 26 which has a normal switching speed arising during normal operations of that transistor that apply electrical signals within normal ranges. If it is desired to change the speed of operation of the transistor, then speed tuning circuitry 12 applies a tuning electrical signal with a tuning characteristic outside of the normal range of characteristics to the transistor concerned. The tuning electrical signal induces a change in at least one of the physical properties of that transistor such that when it resumes its modified normal operations the switching speed of that transistor will have changed. The tuning electrical signal may be a voltage (or current) outside of the normal range of voltages applied to the gate of a transistor so as to induce a permanent increase in the threshold of that transistor and so slow its speed of switching. Temperature of a transistor may also be controlled to induce a permanent change in performance / speed.

Owner:ARM LTD

Bounce tolerant fuse trimming circuit with controlled timing

InactiveUS20030197996A1Switch speed decreaseEnhanced yieldRead-only memoriesEmergency protective arrangements for automatic disconnectionElectricityElectrical connection

A method and apparatus for implementing trimming circuits. More particularly, embodiments of the present invention provide a transistor that supplies sufficient current to trim a trimming fuse when the transistor is powered up and after it receives a select signal at its gate. When the trimming fuse is trimmed, it decouples undesired electrical connections in a circuit. Also provided is a delay structure that adds an RC delay to the select signal. The RC delay is of a sufficiently long duration so as to decrease the switching speed of the transistor. The delay structure also provides a pass filter to filter power and voltage spikes in the select signal.

Owner:EXAR CORP

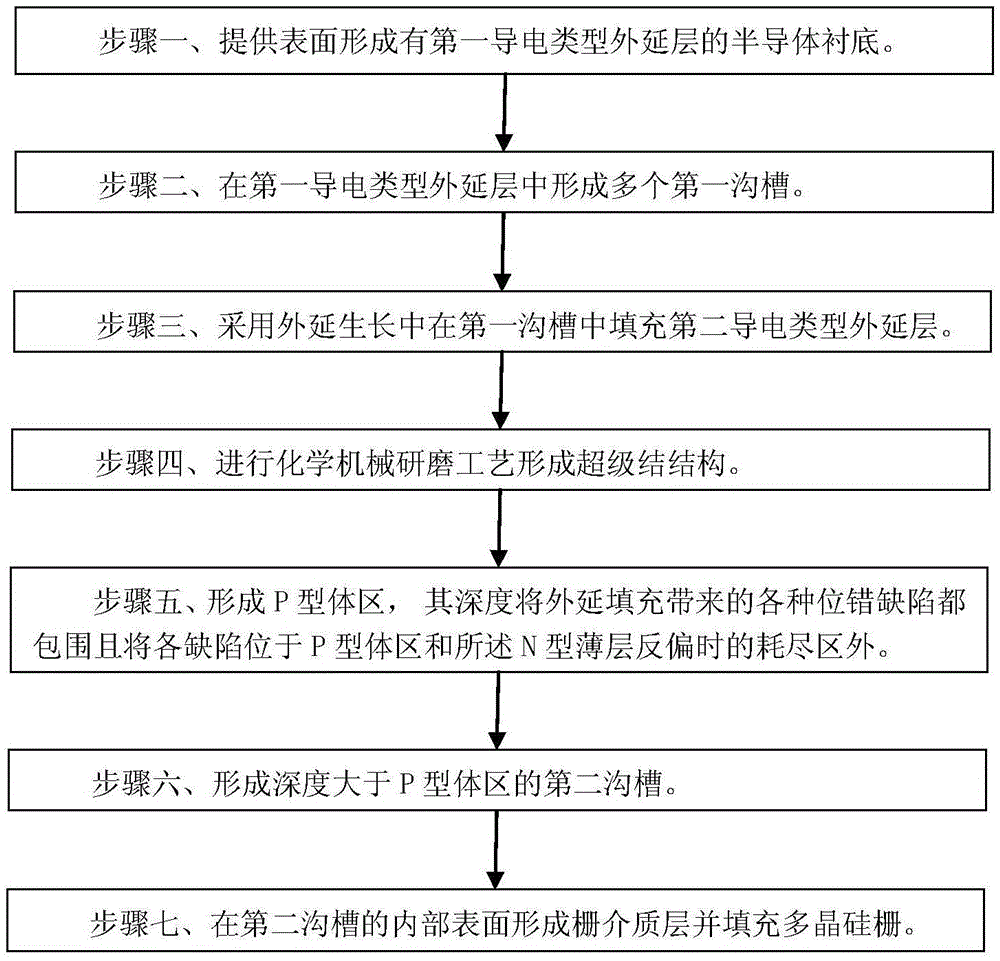

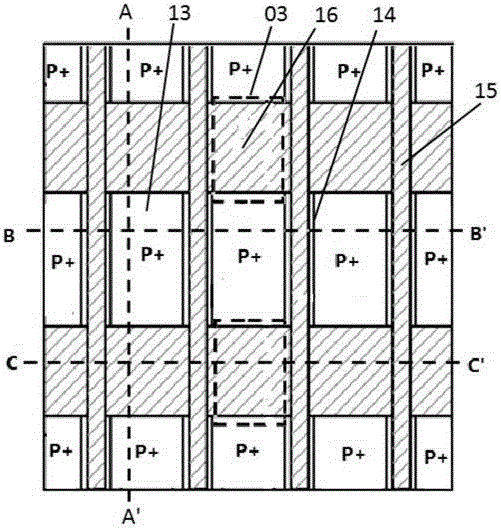

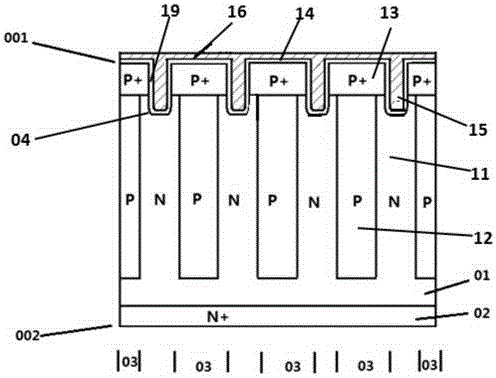

Manufacturing method of groove-type super junction device

ActiveCN105655385AIncrease parasitic capacitanceReduce switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesLattice defectsParasitic capacitance

The invention discloses a manufacturing method of a groove-type super junction device. The method comprises the steps of: providing a semiconductor substrate, wherein a first conductive type epitaxial layer is formed on the surface; forming a plurality of first grooves in the first conductive type epitaxial layer; filling the first grooves with a second conductive type epitaxial layer in an epitaxial growth process; carrying out a chemical and mechanical grinding process to form a super junction; forming a P type body area on the surface of the super junction, wherein the depth of the P type body area meets the requirements that all kinds of crystal lattice defects caused by epitaxial filling are surrounded, and each defect is arranged outside a depletion area of the reverse bias process of the P type body and an N type film layer; forming a second groove whose depth is larger than the P type body area; and forming a gate medium layer on the bottom surface and the side surface of the second groove, and filling the second groove with polysilicon grids. According to the invention, the negative influences caused by the epitaxial filling process on the super junction device are avoided, the reverse leakage current of the super junction device is reduced, and the production yield rate of the super junction device is improved; in addition, parasitic capacitance is reduced, and the electromagnetic interference performance of the circuit and the system is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Super junction semiconductor device with optimized switching characteristic and manufacturing method

ActiveCN106158927AAdding input capacitanceReduce the value of dV/dtSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceBody area

The invention relates to a super junction semiconductor device with the optimized switching characteristic and a manufacturing method. The super junction semiconductor device is characterized that integrated capacitor areas are introduced into the surface of a trench gate type super junction semiconductor device, and each integrated capacitor comprises a gate capacitor plate, a first insulating medium layer and a second conduction type body area, wherein the areas, adjacent to a semiconductor substrate, of the first insulating medium layers in the section direction of the semiconductor are the second conduction type body areas, the first insulating medium layers are provided with the gate capacitor plates which are adjacent to one another, and the gate capacitor plates are electrically communicated with gate electrodes. According to the device, by introducing the integrated capacitor areas, the input capacitance Ciss of the device can be effectively increased, but the feeback capacitance Crss and the output capacitance Coss of the device are invariable, therefore, the ratio of the feedback capacitance Crss to the input capacitance Ciss is decreased, then the switching characteristic of the device is improved, and the ratio of dV to dt in the switching process is decreased; in addition, the manufacturing method of the device is compatible with an existing semiconductor technology, preparation of the integrated capacitor areas can be completed on the premise that no technological step is added, and therefore cost is not increased.

Owner:WUXI NCE POWER

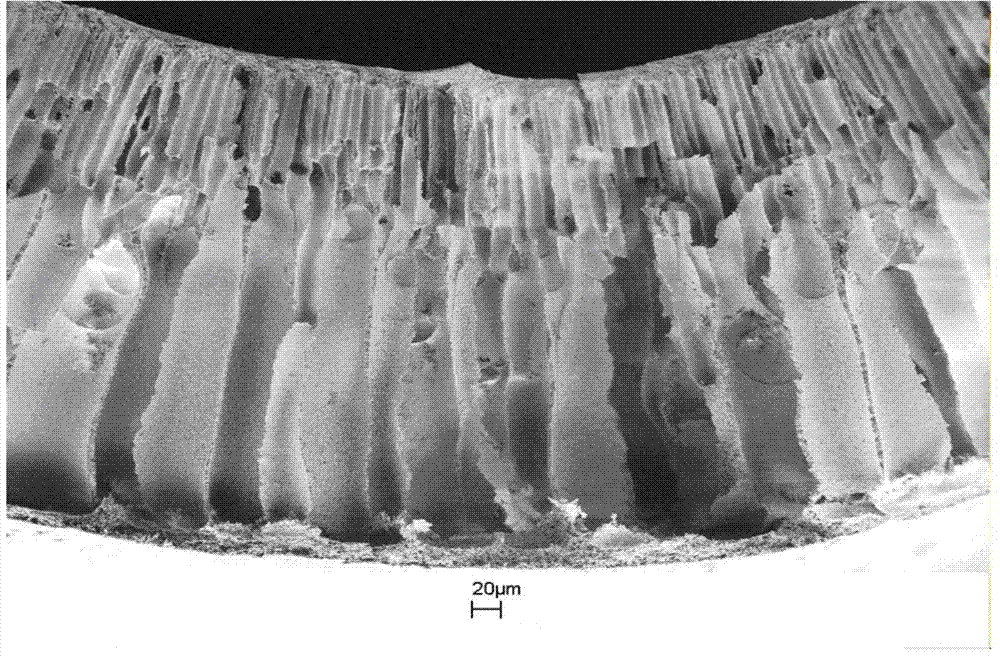

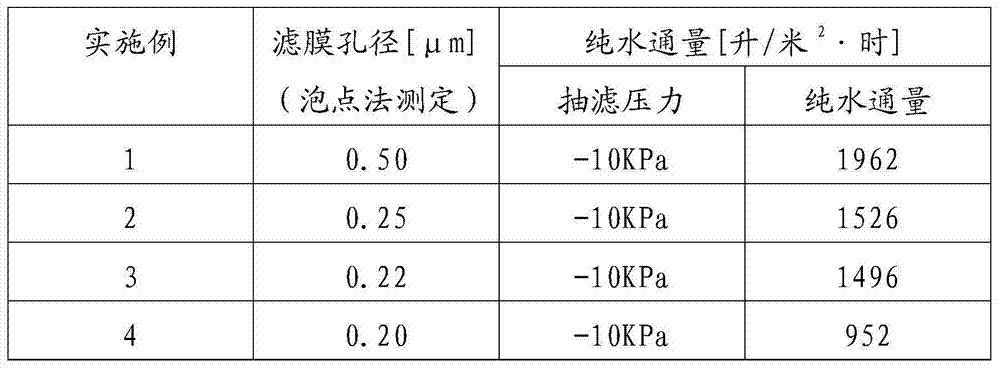

Hollow internal-pressing fiber film and preparation method thereof

ActiveCN103495354ALarge apertureImprove hydrophilicitySemi-permeable membranesPolymer scienceDissolution

The invention discloses a hollow internal-pressing fiber film and a preparation method thereof, and provides a hollow internal-pressing fiber film with uniform large hole diameter and a through hole structure and a preparation method of the hollow internal-pressing fiber film. The preparation method includes stirring 5-15% of polyether sulfone resin, 1-5% of ultra-high molecular weight polyacrylonitrile resin, 75-80% of solvent, 1-5% of micromolecule additives, 1-5% of polymeric additives and liquid pore-forming agents at the temperature of 50-80 DEG C for dissolution, evenly mixing, and obtaining film casting liquor after removing of bubbles; extruding the film casting liquor by a spinneret plate, subjecting the film casting liquor to a coagulating bath at the temperature of 10-70 DEG C, and obtaining raw silks of the hollow internal-pressing fiber film after completion of gelling. Through determination of polyether sulfone resin / polyacrylonitrile resin blending ratio, solid content, additive types and concentration, the polyether sulfone hollow internal-pressing fiber film with the through hole structure and the uniform large hole diameter can be obtained.

Owner:TIANJIN MOTIMO MEMBRANE TECH