Super junction semiconductor device with optimized switching characteristic and manufacturing method

A technology of super-junction semiconductor and switching characteristics, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as large dV/dt, aggravated dV/dt increase, directional voltage spikes, etc., to reduce dV /dt, the effect of reducing system EMI and increasing input capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described below in conjunction with specific drawings and embodiments.

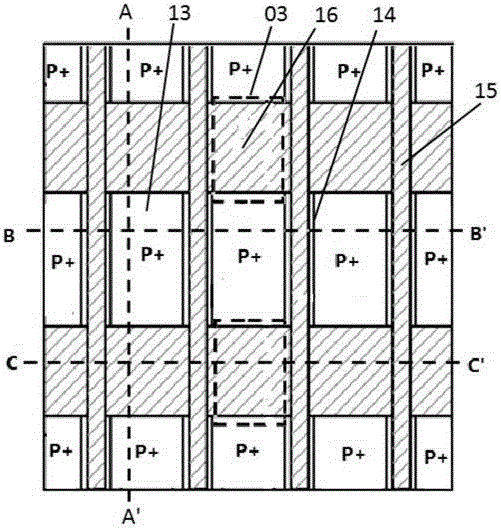

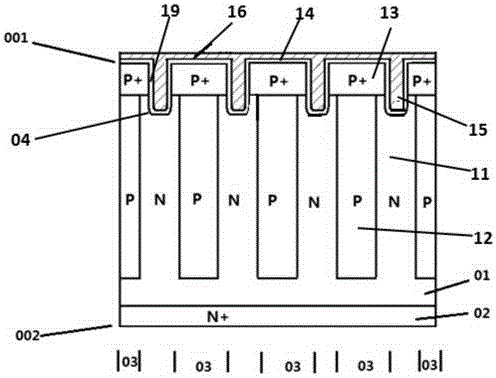

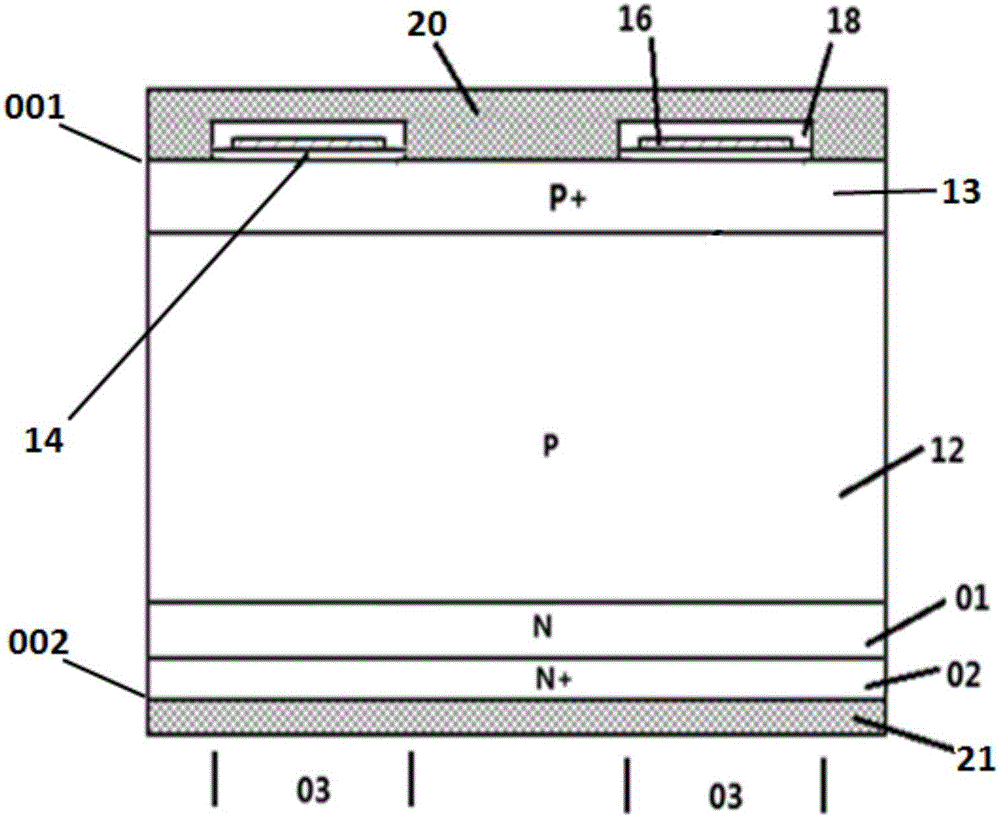

[0043] as attached figure 1 As shown in ~ 4, a super junction semiconductor device with optimized switching characteristics, taking an N-type trench gate super junction semiconductor device as an example, includes a cell area and a terminal protection area, the cell area is located in the central area of the device, The terminal protection area surrounds the cell region, and the cell region includes a semiconductor substrate, and the semiconductor substrate includes a first conductivity type substrate 02 and a first conductivity type substrate 02 located on and adjacent to the first conductivity type substrate. A conductivity type drift region 01, the upper surface of the first conductivity type drift region 01 is the first main surface 001 of the semiconductor substrate, and the lower surface of the first conductivity type substrate 02 is the second main sur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More