SPICE (Simulation Program for Integrated Circuit Emphasis) macro model molding method for SOIMOS (Silicon on Insulator Metal Oxide Semiconductor) transistor dose rate radiation

A dose rate and macro model technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as sag and peak current sag, and achieve the effects of improving simulation accuracy, improving efficiency, and speeding up the research and development cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

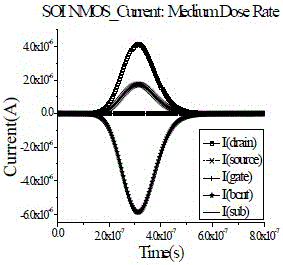

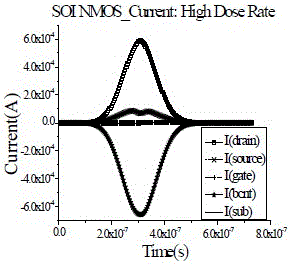

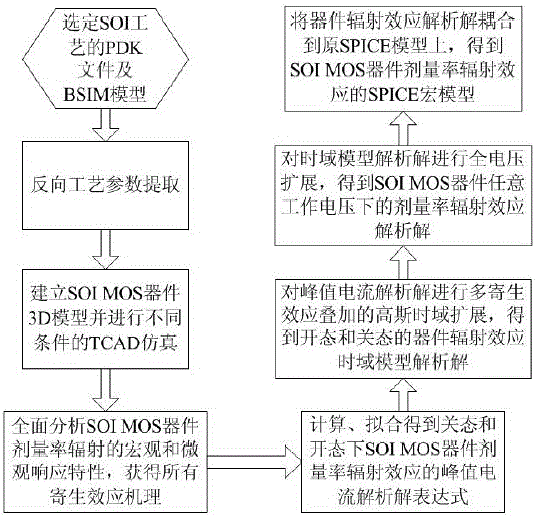

[0030] The method of the invention is suitable for MOS devices of deep submicron SOI technology, mainly including SOI technology of 0.5um, 0.35um, 0.18um, 0.15um, 0.13um and other sizes. Take the 0.5um process as an example below, combined with image 3 The flow chart shown illustrates the specific implementation process of the present invention.

[0031] First, select a 0.5um SOI process line of a process manufacturer and obtain its PDK file and BSIM model, and then use Hspice (a circuit SPICE model simulator under the American Synopsys company) to simulate and obtain the required parameters for reverse process parameter extraction. standard control I D -V G curve. Then based on the known device structure, some existing process parameters (such as substrate thickness, silicon film thickness, buried oxide layer thickness, substrate uniform doping concentration, N / P well region doping depth, etc.) and various unknown parameters Establish a 3D model of the SOIMOS device and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More