Instruction scheduling method and device

An instruction scheduling and instruction technology, applied in the direction of machine execution devices, concurrent instruction execution, etc., can solve the problems of ME performance degradation, large degree of disorder, idle kernel pipeline, etc., to improve overall performance, reduce degree of disorder, and avoid instructions empty shot effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

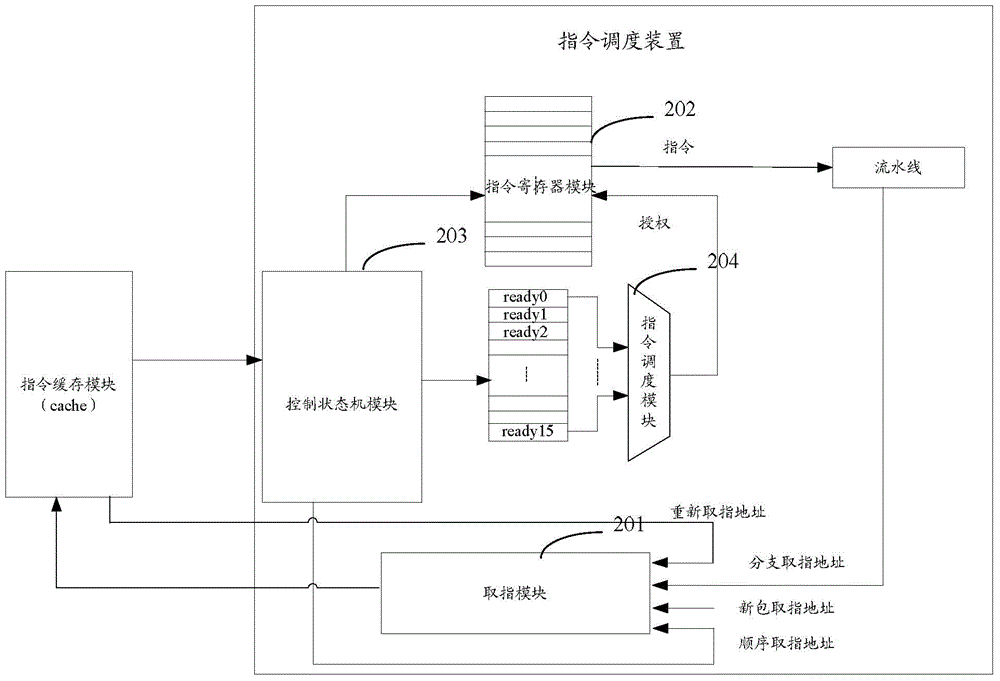

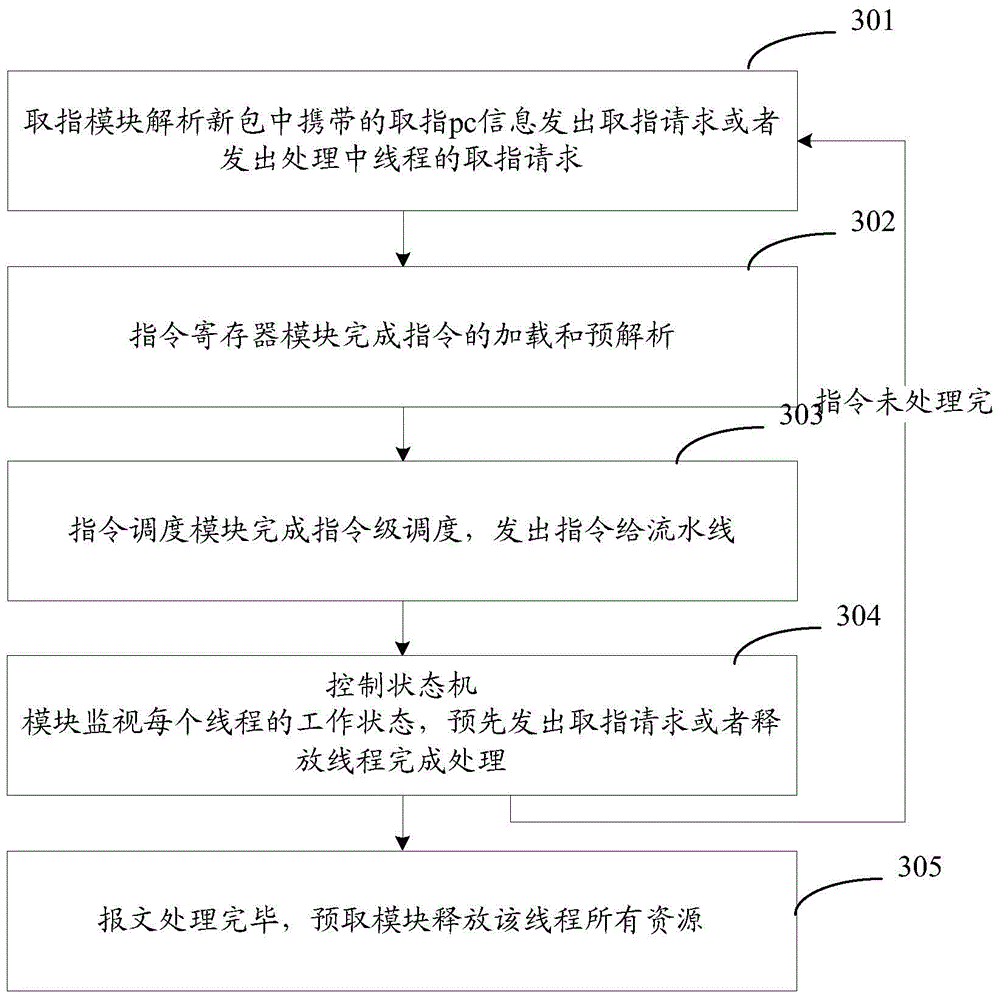

[0068] image 3 It is a schematic diagram of the ME command scheduling process described in Embodiment 1 of the present invention, as image 3 As shown, the method includes the following steps:

[0069] Step 301, the fetching module parses the fetching pc information carried in the new package, and issues a fetching request;

[0070] Here, the instruction fetch module is composed of four queues plus an arbitration module, the queue caches the corresponding instruction fetch request, and sends an instruction fetch request to the cache after 4 to 1 arbitration. Considering the actual processing of packet instruction fetch requests, the four queues correspond to four instruction fetch pc requests respectively, new packet instruction fetch pkt_pc, message sequential instruction fetch, jump instruction fetch, and repeated instruction fetch after cache miss.

[0071] In actual packet processing, for a new packet, parse the packet information, extract the instruction fetch pc, and ...

Embodiment 2

[0084] In this embodiment, the instruction scheduling device completes the prefetching of instructions through the instruction fetch module and the control state machine module, Figure 4 It is a schematic diagram of the instruction prefetching flow chart of the ME described in Embodiment 2 of the present invention, as shown in Figure 4 As shown, the method includes the following steps:

[0085] Step 401, the new packet enters the ME, the instruction scheduling device parses and extracts the instruction fetch pc, and sends an instruction fetch request to the instruction fetch module;

[0086] Step 402, the instruction fetch module sends an instruction fetch request to the cache through arbitration scheduling;

[0087] In step 403, the instruction is returned and loaded into the instruction register module, and is scheduled to be sent to the pipeline. During execution, the control state machine module monitors the instruction issuance of each thread. When there is only one ...

Embodiment 3

[0097] In this embodiment, the instruction scheduling device manages the instruction scheduling of each thread through the instruction scheduling module. The instruction scheduling module completes thread-level instruction scheduling according to the LRU algorithm (LeastRecentlyUsed), and transmits instructions from the cache to the pipeline to ensure that the packets that enter the ME first are executed first.

[0098] Figure 6 It is a schematic flow diagram of ME thread-level instruction scheduling described in Embodiment 3 of the present invention, as shown in Figure 6 As shown, the method includes the following steps:

[0099] Step 601, extracting the thread number of the new package, and writing it into the base queue;

[0100] The essence of the thread-level instruction scheduling strategy of the present invention is to dynamically update the RR round-robin scheduling of the base. When the value of the base is set as the value of the corresponding thread, the thread ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More