DRAM (dynamic random access memory)-NVM (non-volatile memory) hierarchical heterogeneous memory access method and system adopting software and hardware collaborative management

一种DRAM-NVM、软硬件协同的技术,应用在内存架构访问/分配、存储器系统、内存地址/分配/重定位等方向,能够解决应用局部性差、读写时延长、访存时延长等问题,达到提升DRAM缓存利用率、消除硬件开销、降低访存时延的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to more clearly illustrate the purpose, technical solutions and advantages of the present invention, the present invention will be further described in detail in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

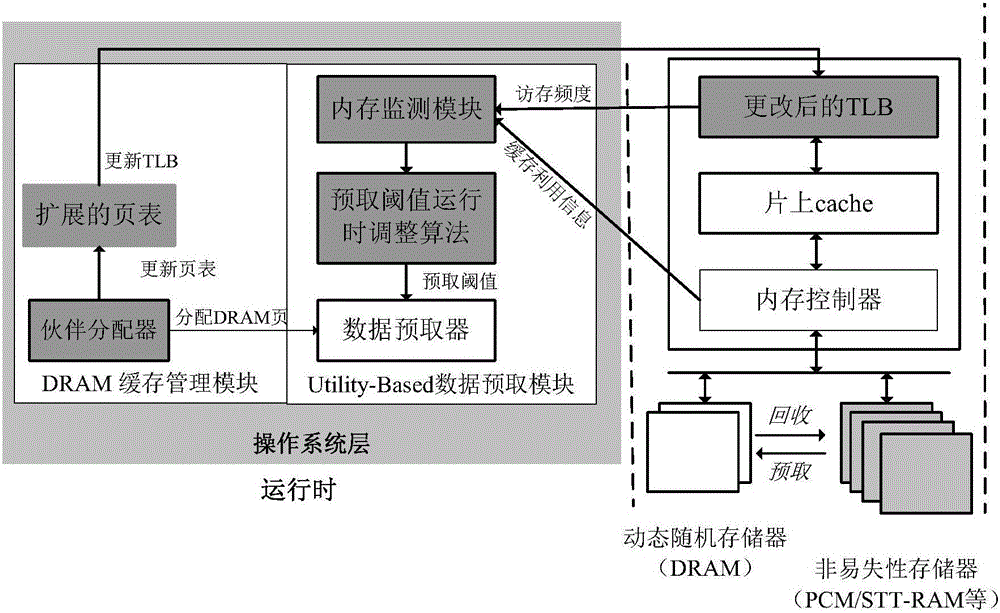

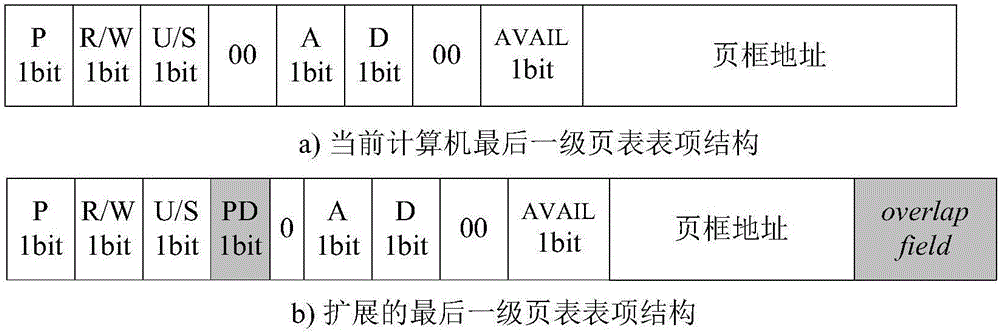

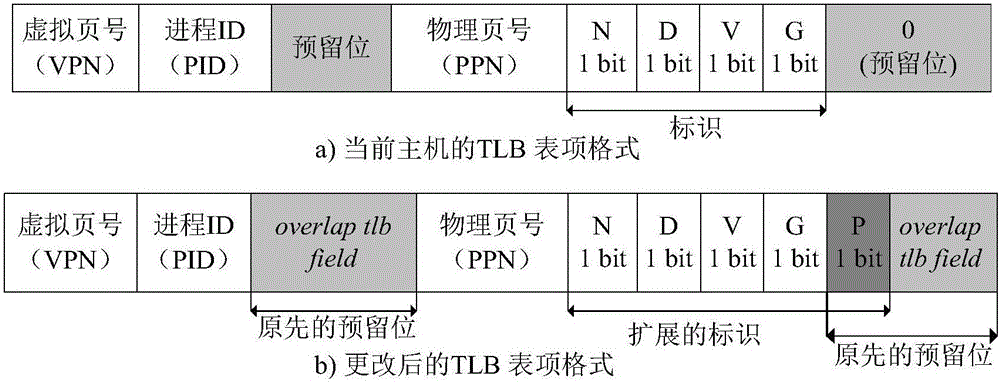

[0031] figure 1Shown is the DRAM-NVM hierarchical heterogeneous memory system structure diagram of the software and hardware cooperative management proposed by the present invention, the hardware layer includes the modified TLB, and the software layer includes: extended page table, Utility-Based data prefetch module and DRAM Cache management module. The extended page table is mainly used to manage the mapping between virtual pages to physical pages and NVM memory pages to DRAM cache pages. The modified TLB caches frequently accessed page table entries in the extended page table, thereby im...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com