Semiconductor structure and formation method thereof

A semiconductor and plasma technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of unstable performance, poor transistor morphology, and increased process difficulty of high-K metal gate transistors. Reliable performance, good appearance, dense interior

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] As mentioned in the background art, the high-K metal gate transistors formed in the prior art have poor morphology and unstable performance.

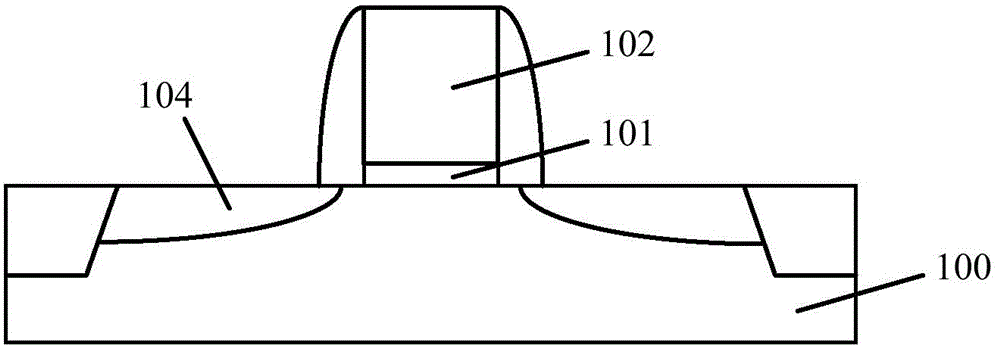

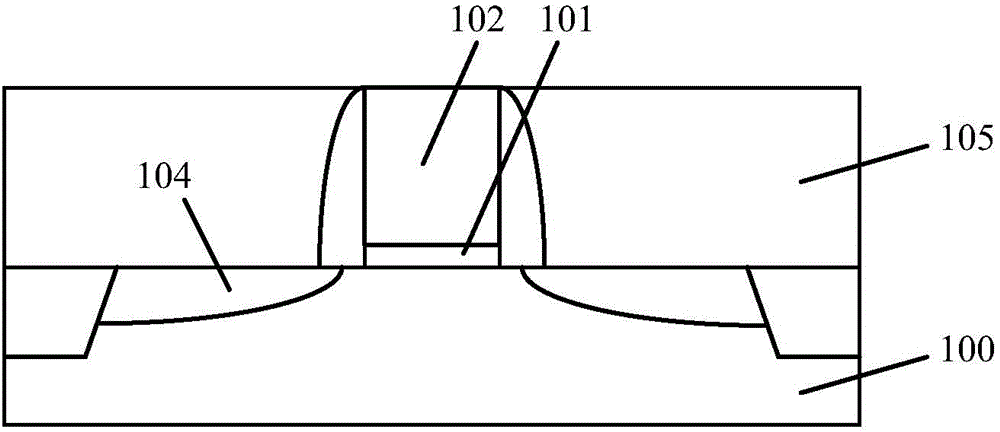

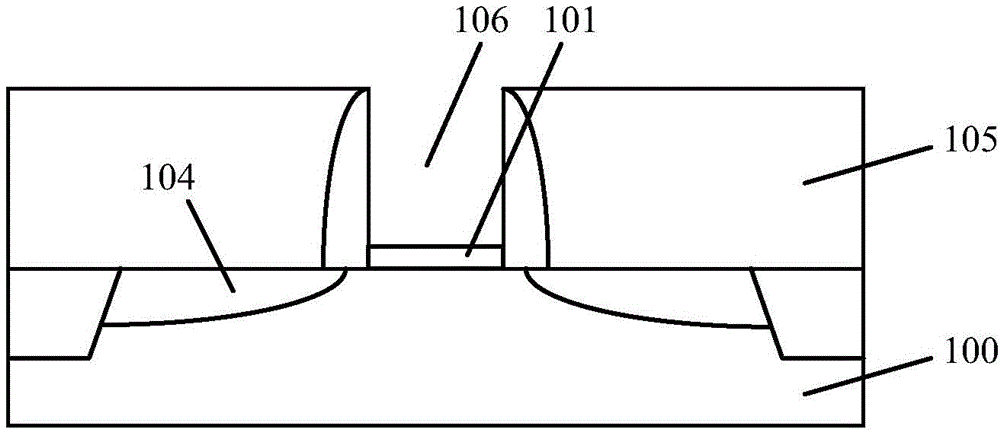

[0033] After research, it is found that the high-K metal gate transistor needs to be formed by a gate last process. Figure 1 to Figure 4 It is a schematic cross-sectional structure diagram of a process of forming a high-K metal gate transistor by using a gate-last process according to an embodiment of the present invention.

[0034] Please refer to figure 1 , providing a substrate 100; forming a gate dielectric layer 101 on the surface of the substrate 100, and a dummy gate layer 102 located on the surface of the gate dielectric layer 101; wall; forming a source region and a drain region 104 in the substrate 100 on both sides of the sidewall and the dummy gate layer 102 .

[0035] Please refer to figure 2 , forming a dielectric layer 105 on the surface of the substrate 100 , the surface of the dielectric layer 105 is flush w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More