Fin-type field effect transistor and forming method therefor

A fin field effect and transistor technology, applied in semiconductor devices, semiconductor/solid state device manufacturing, electrical components, etc., can solve problems such as poor performance of fin field effect transistors, and achieve improved performance, increased mobility, and improved operation. effect of speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

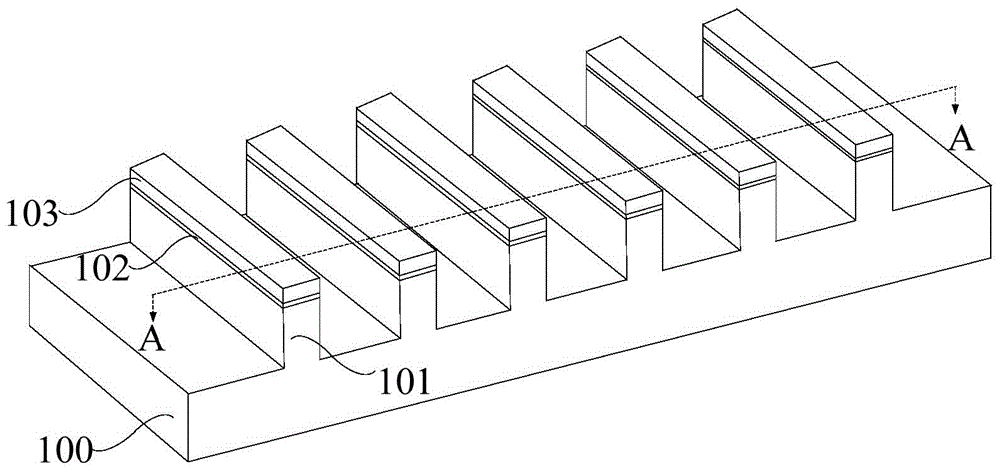

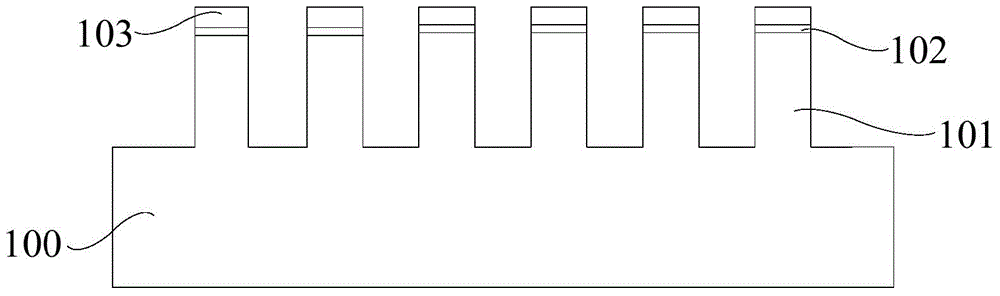

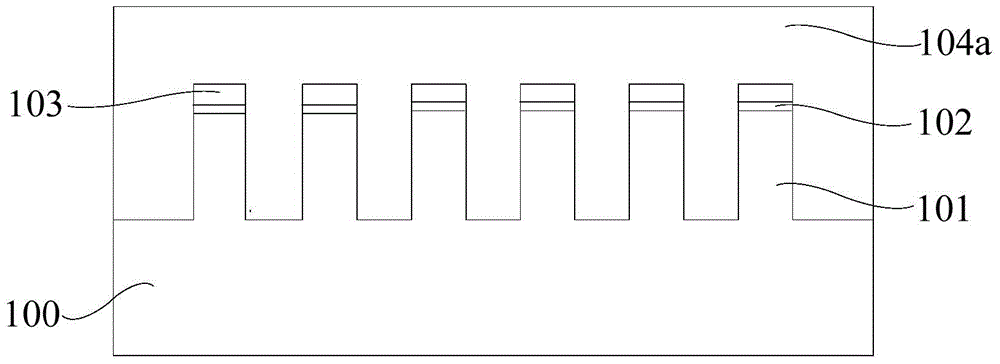

[0049] The reasons for the poor performance of the FinFETs formed by the methods of the prior art are as follows:

[0050] refer to Figure 5 , the material of the insulating material layer is silicon oxide. Wet etching is isotropic etching, and in the process of etching back the insulating material layer 104 a by wet etching, the pad oxide layer 102 made of the same material will also be corroded and broken. In this way, the mask layer 103 located on the pad oxide layer 102 will drop onto the insulating material layer 104a being wet-etched to form particles, which affect the formation quality of the insulating layer 104, for example, Holes appear in the insulating layer 104 , thereby affecting the isolation effect of the insulating layer 104 , and further affecting the performance of the subsequently formed FinFET.

[0051] Also, refer to Figure 6 to Figure 8 , because the mask layer 103 on the top of the fin 105 falls off, the channel stop ion implantation will be perfor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More