Inter-chip interconnection structure, manufacturing method of inter-chip interconnection structure and packaging structure

An interconnection structure and packaging structure technology, applied in the semiconductor field, can solve the problems of reducing interconnection pitch, damage to electronic devices, damage to sensitive devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

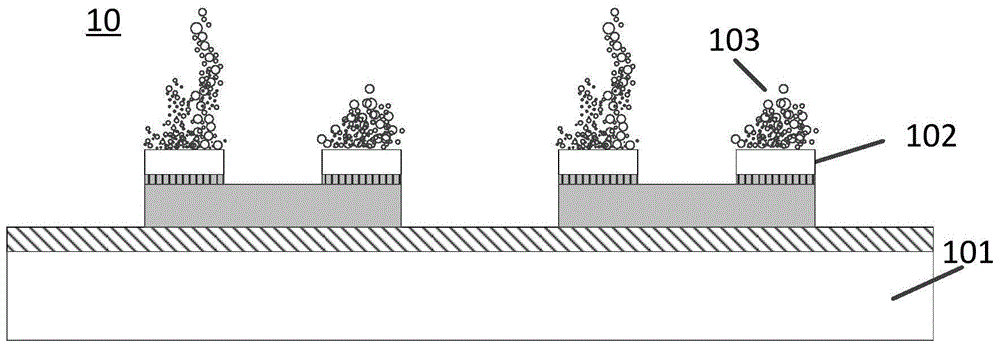

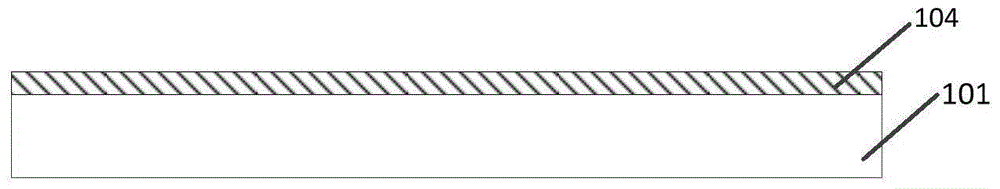

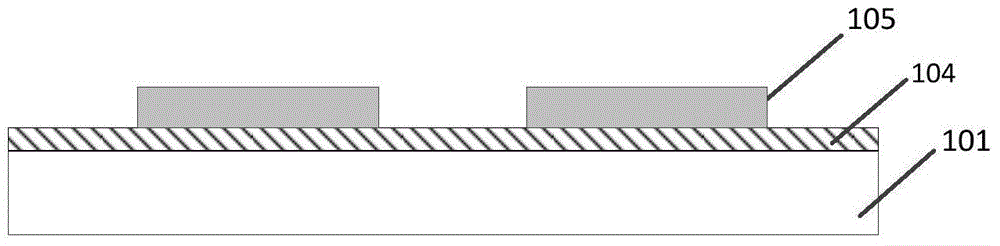

[0041] figure 1 A schematic diagram of an inter-chip interconnect structure 10 according to an embodiment of the present invention is shown. Such as figure 1 As shown, the interchip interconnection structure 10 may include a substrate 101 and first bonding bumps 102 formed on the substrate 101 . The material forming the substrate 101 may include, but not limited to, one of the following: silicon, glass, gallium nitride (GaN), or gallium arsenide (GaAs). The first bonding bump 102 can be any metal suitable for bonding, such as copper (Cu), gold (Au), tin (Sn), aluminum (Al), silver (Ag) and the like. The first bonding bump 102 may be, for example, a film bump...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More