Method of forming a fin field effect transistor

A fin field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid state device manufacturing, electrical components, etc., can solve the problems of poor performance of N-type fin field effect transistors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

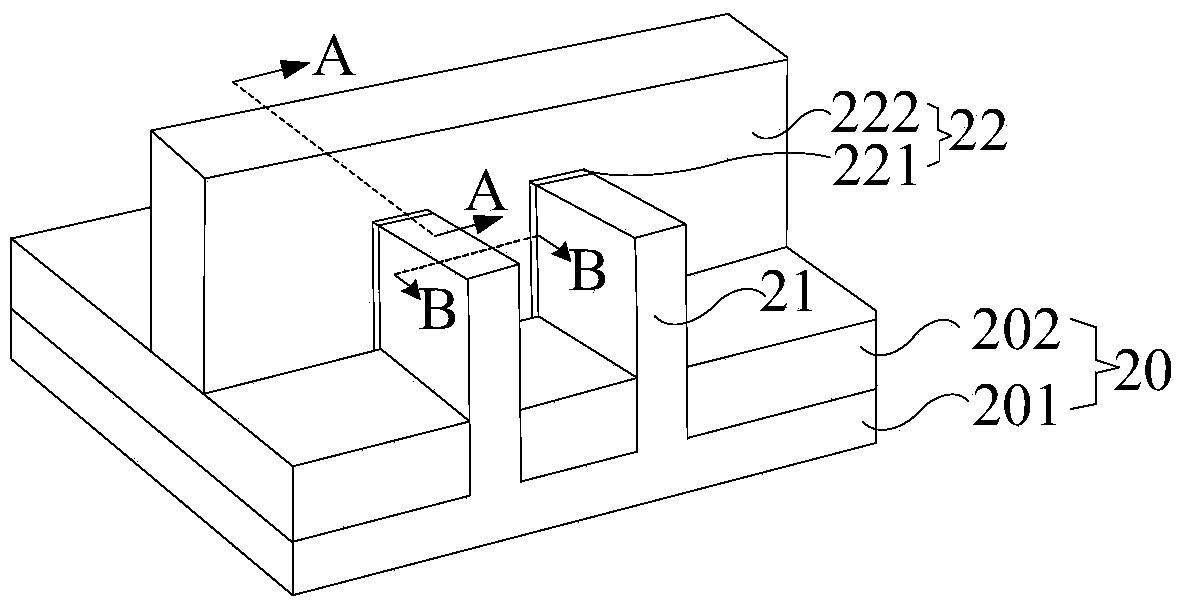

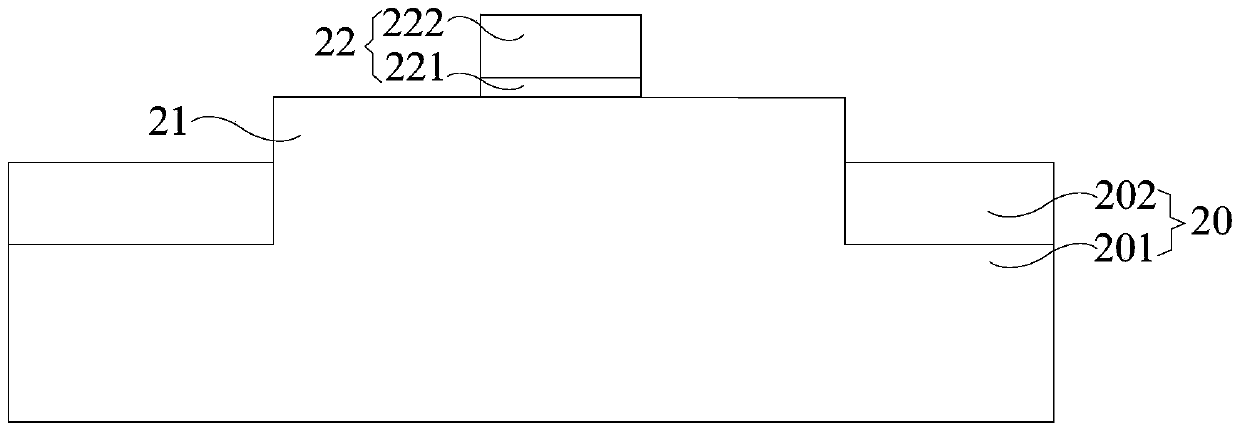

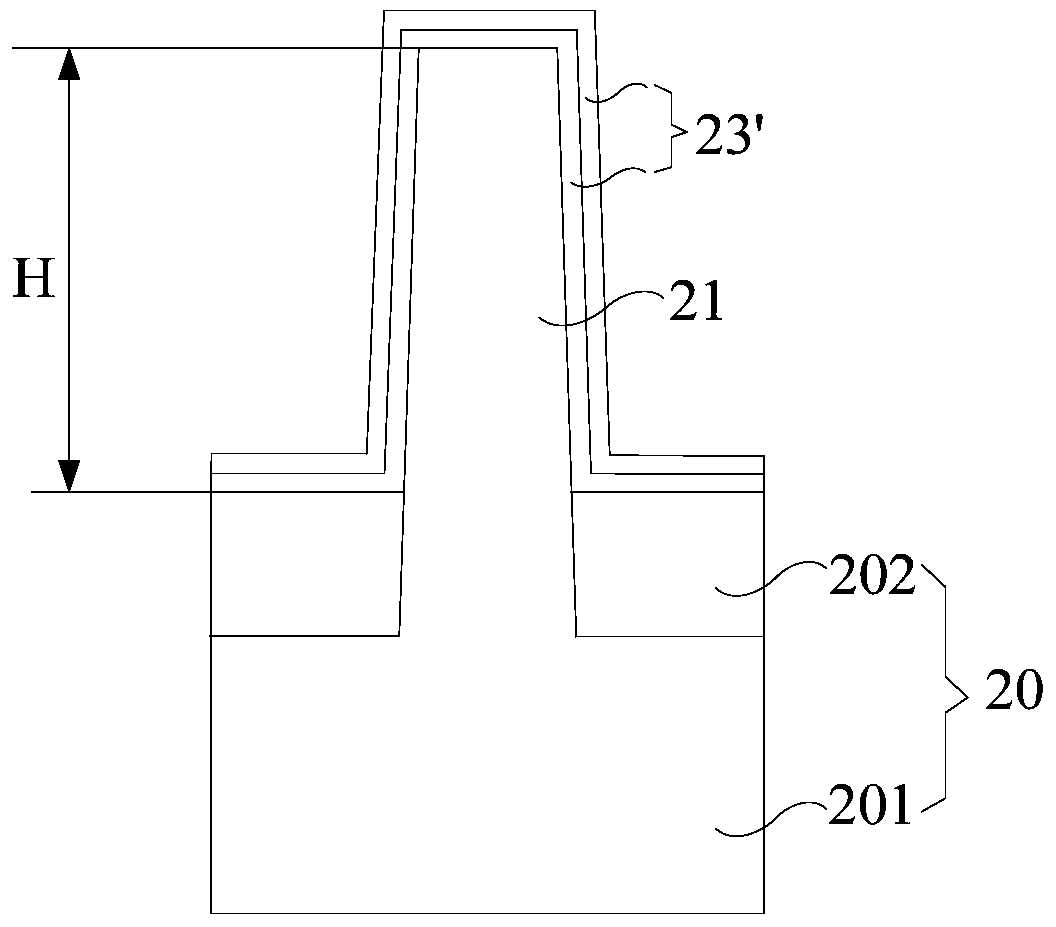

Image

Examples

Embodiment 2

[0120] The difference between the second embodiment and the first embodiment is as follows:

[0121] This embodiment further includes a second region adjacent to the first region, the first region is used to form an N-type fin field effect transistor, and the second region is used to form a P-type field effect transistor. The second region has a second fin. For the method of forming the second fin, please refer to the method of forming the first fin.

[0122] In this embodiment, the second fin is formed simultaneously with the first fin.

[0123] A second polysilicon gate structure is formed across the second fin, the second polysilicon gate structure covers the top and sidewalls of the second fin. The second polysilicon gate structure includes a second gate oxide layer and a second polysilicon layer on the second gate oxide layer.

[0124] In this embodiment, the second polysilicon gate structure is formed simultaneously with the first polysilicon gate structure.

[0125]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More