Low-voltage trench DMOS device of high integrated level and manufacture method of device

A technology with high integration and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reducing cell size, reducing on-resistance, and insufficient registration accuracy of contact holes, etc., to achieve reduction Chip cost, increase the on-resistance per unit area, and increase the effect of cell design size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

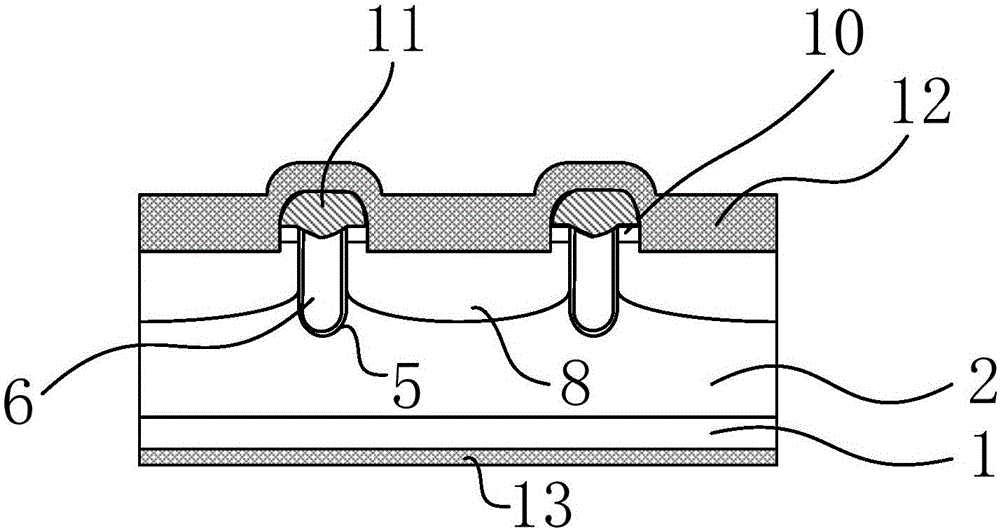

[0052] Embodiment 1. In this embodiment, the first conductivity type is N type, and the second conductivity type is P type;

[0053] This embodiment provides a method for manufacturing a highly integrated low-voltage trench gate DMOS device, through the first insulating dielectric layer remaining above it when the gate electrode is etched, and the second insulating dielectric layer remaining on the sidewall of the gate electrode after etching back The parts together form the electrical insulation between the source metal and the gate electrode, thereby reducing the cell size and increasing the integration degree per unit area.

[0054] This method is implemented through the following steps:

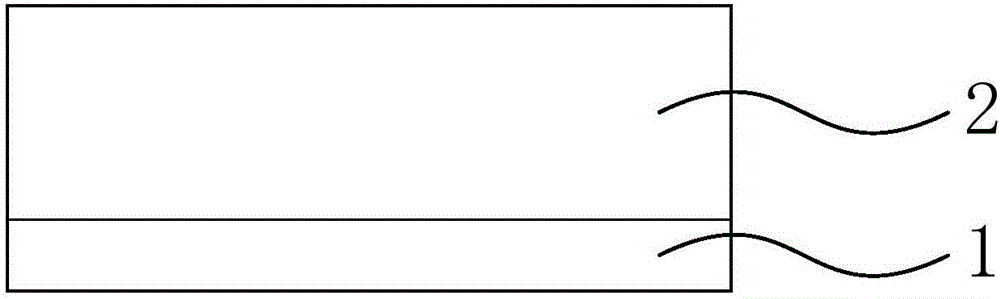

[0055] Step 1: If figure 2 As shown, an N+ type substrate 1 is provided, and an N type epitaxial layer 2 is formed on the front surface of the N+ type substrate 1;

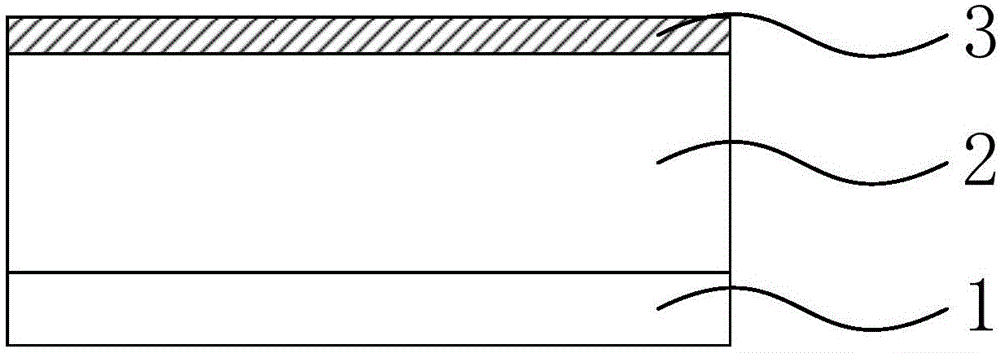

[0056] Step 2: If image 3 As shown, a trench etch barrier layer 3 is deposited on the N-type epitaxial layer 2; the ma...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More