Stack type single base island SIP (System in Package) packaging process

A packaging technology and stacking technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of MOS chip size that cannot be attached, overheating damage, and poor heat dissipation in the packaging form, so as to avoid the formation of creeping Electric phenomena, enlarging the package size, and taking up less space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

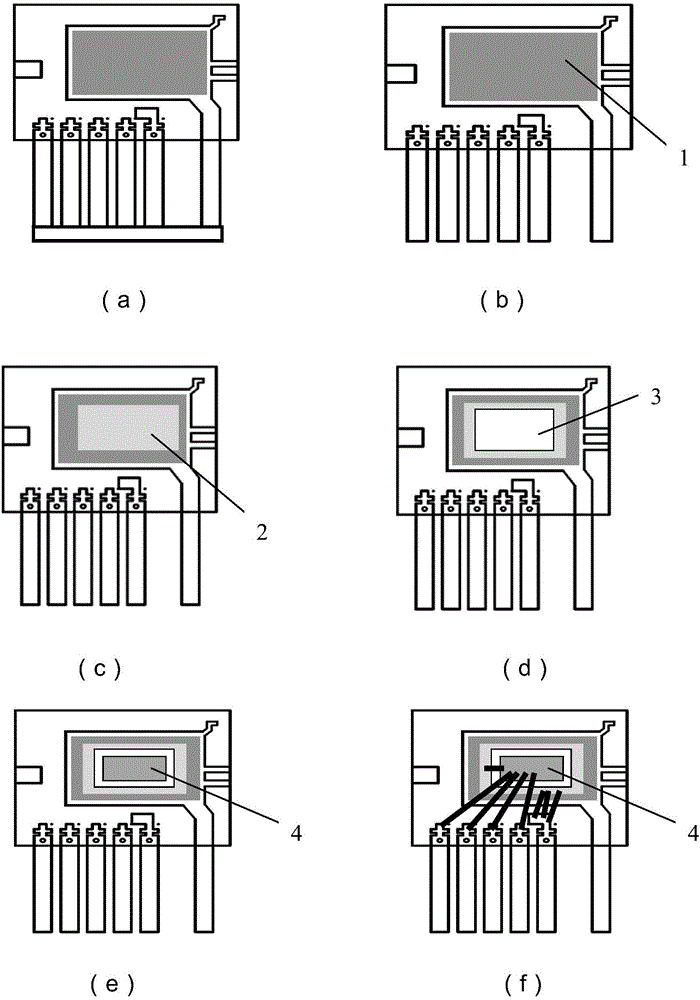

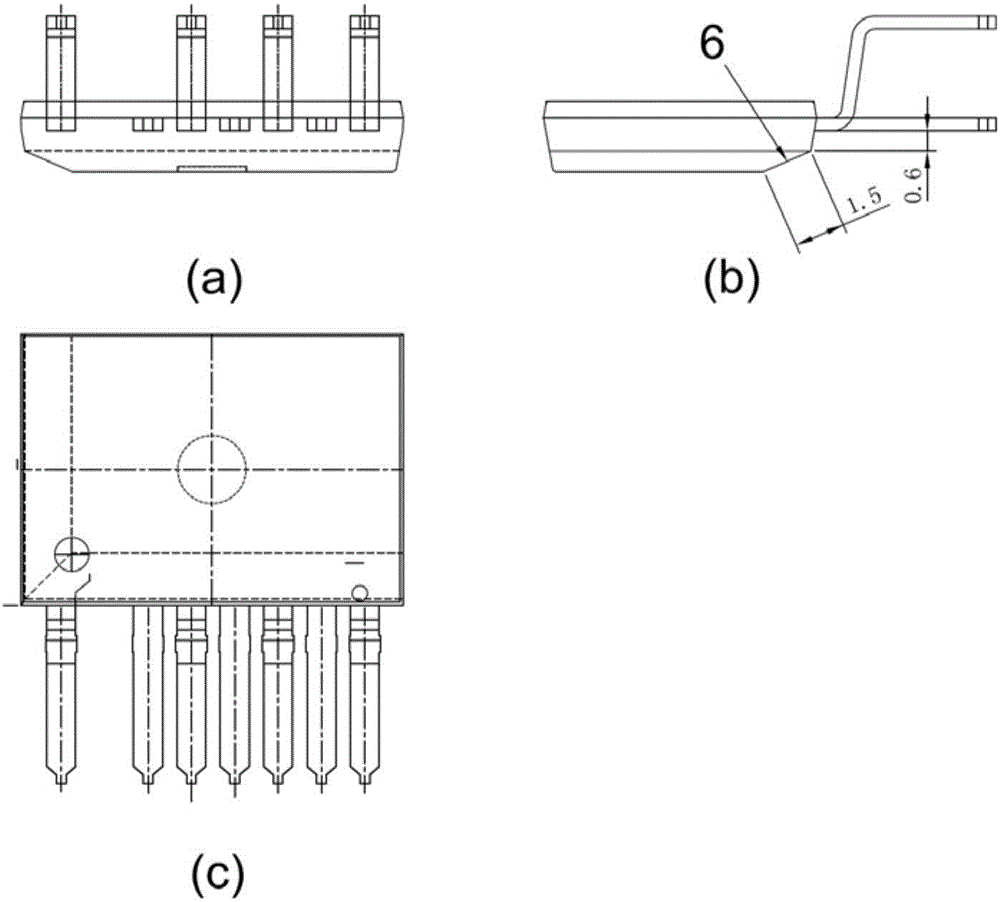

[0028] refer to Figure 1-3 , a stacked single-substrate island SIP packaging process of the present invention, comprising the following steps:

[0029] Step 1, take a frame with a single base island;

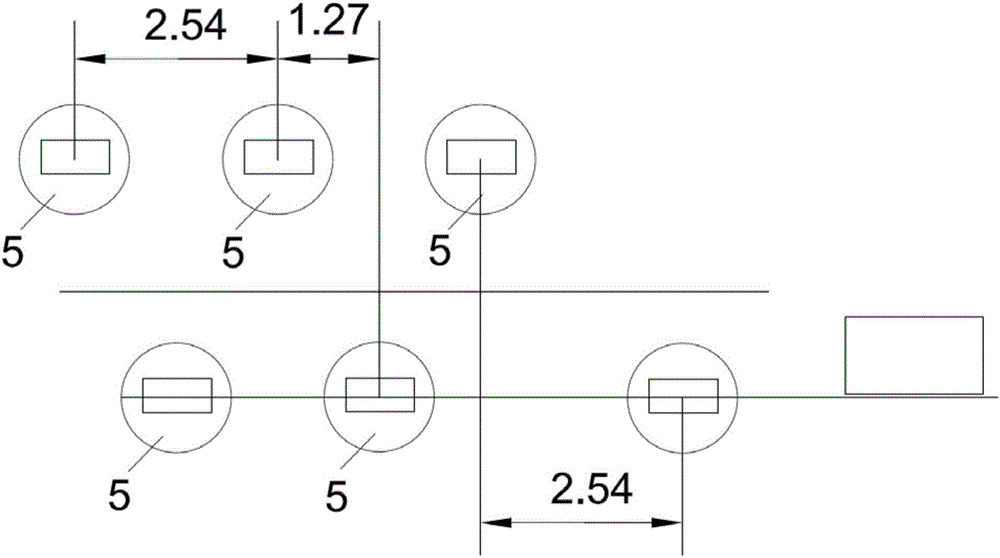

[0030] Step 2, step 2, weld the pin group on the frame, the pin group includes several chip pin groups for connecting the chip, the chip pin group includes several chip pin groups with an interval of 1.27mm and is arranged side by side Chip pin 5, cut off the pin connection end, and then bend the chip pins 5 in odd or even rows in the chip pin group horizontally to form two columns of pins with an interval of 2.54mm to form a lead frame;

[0031] Step 3, spot soft solder 1 on the single base island of the lead frame;

[0032] Step 4: Paste the first chip 2 on the single base island with soft solder 1 on it, and then heat to 260-300°C to melt the soft solder 1 to weld the first chip 2 and the lead frame together;

[0033] Step five, point insulating glue 3 on the surface of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com