SiC-based groove-type field effect transistor and preparation method thereof

A field-effect transistor, trench-type technology, applied in the field of SiC-based UMOSFET fabrication, can solve problems such as unfavorable breakdown voltage, device breakdown, and low channel mobility, and achieve improved on-state conductivity and dynamic switching loss. The effect of reducing and avoiding JFET resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

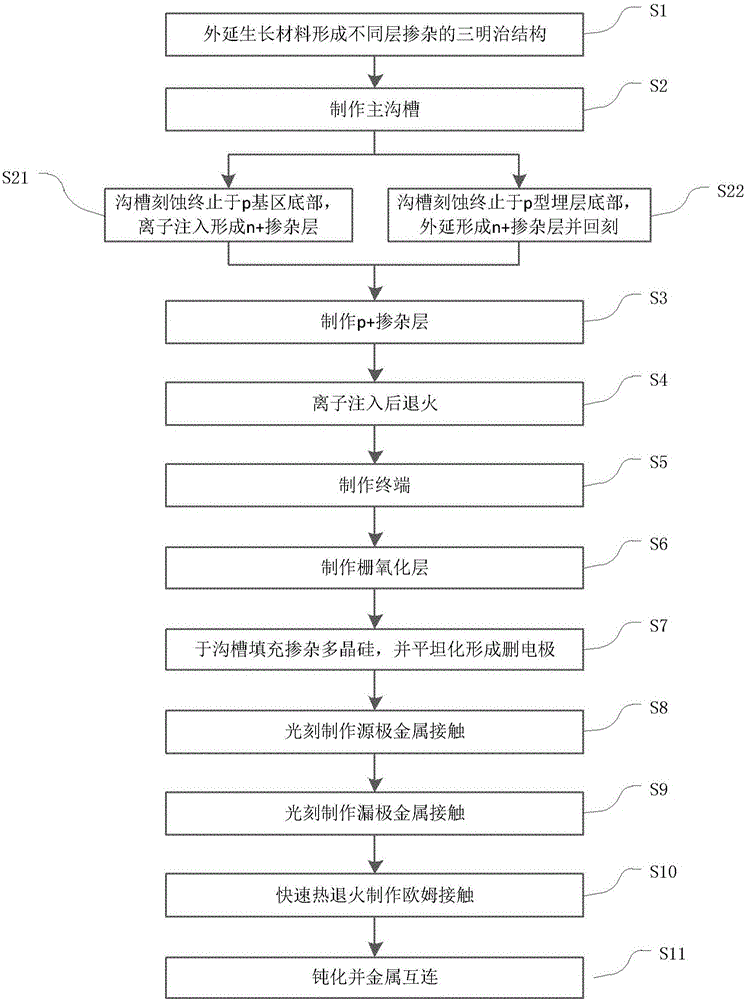

[0034] figure 1 A process flow for preparing a SiC-based UMOSFET according to an embodiment of the present invention is shown, including the following steps:

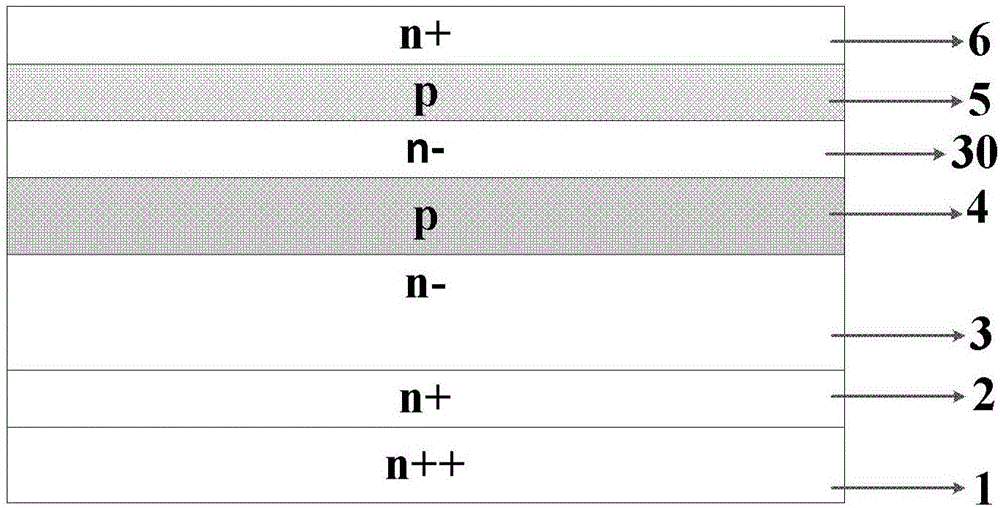

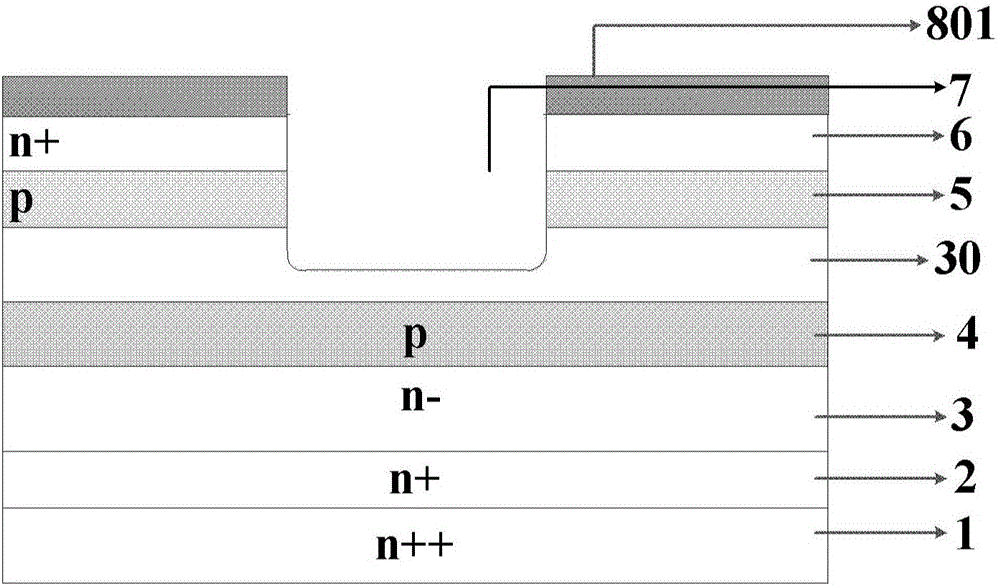

[0035] In step S1, the epitaxial growth material forms a sandwich structure doped in different layers. According to an embodiment of the present invention, such as figure 2 As shown, using chemical vapor deposition or other methods of epitaxial growth materials to epitaxially grow multiple layers of SiC epitaxial layers of different doping types on the SiC n++ type substrate substrate 1, forming a sandwich structure, from bottom to top in order: : n+ type buffer layer 2, n-drift layer 3, p-type buried layer 4, n-drift layer 30, p-type base region layer 5, n+ sou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com