Multilevel folding-interpolation type analog-digital converter and decoding method thereof

An analog-to-digital converter, folding and interpolation technology, applied in the direction of analog-to-digital converter, analog-to-digital conversion, code conversion, etc., can solve the problem of complex decoding algorithm, and achieve the effect of simplifying the complexity and shortening the clock cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

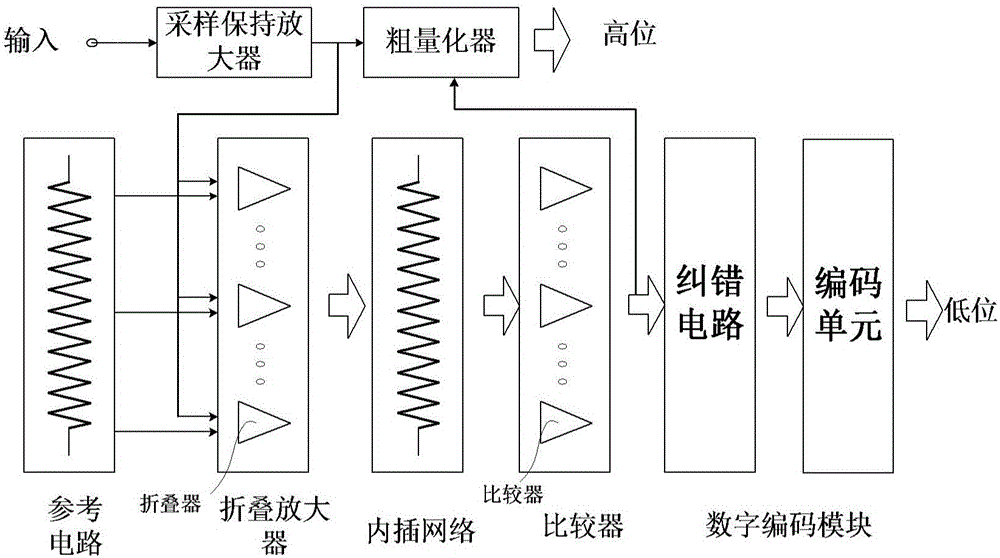

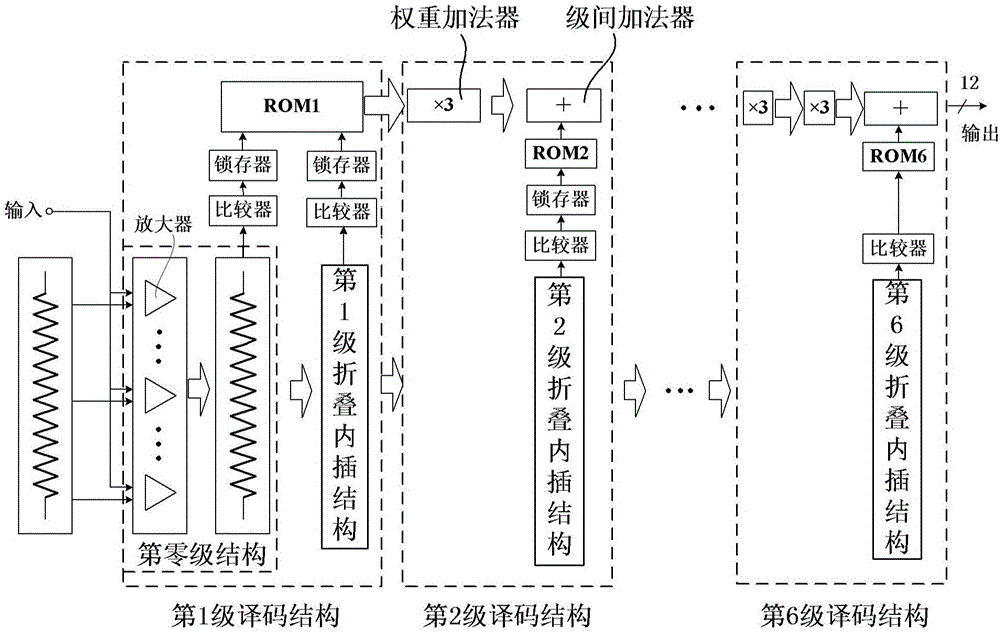

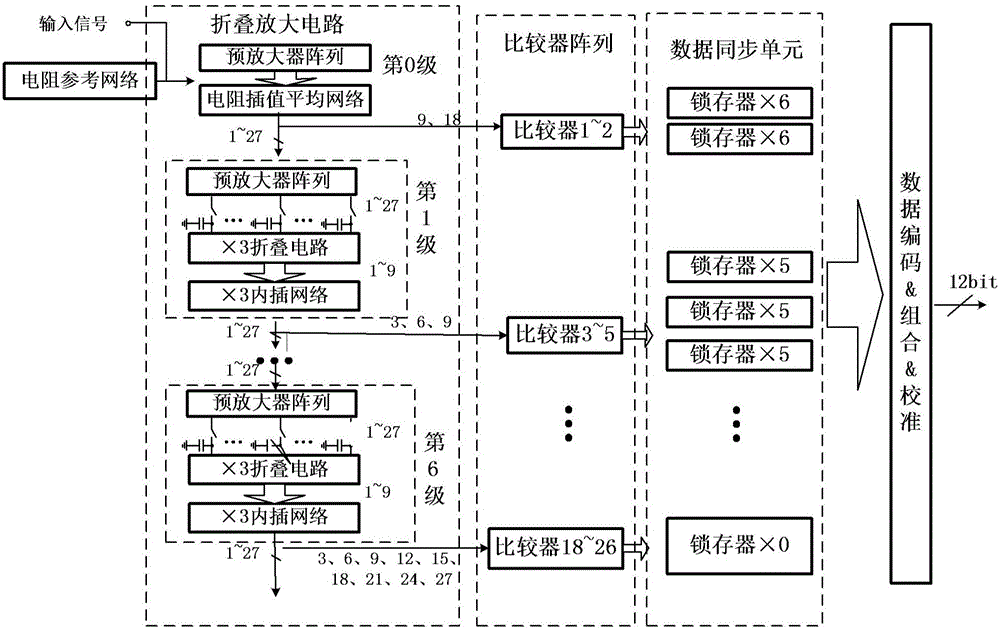

[0039] Such as figure 2 Shown is a system architecture diagram of a multi-level folding interpolation ADC with a folding rate of 3, including: a reference circuit, and a six-level decoding structure connected in sequence, the first level decoding structure, the second level decoding structure, The third-level decoding structure, the fourth-level decoding structure, the fifth-level decoding structure, and the sixth-level decoding structure.

[0040] Please also refer to image 3 , the first-level decoding structure is connected to the resistance reference network and the signal input terminal, including the zero-level structure and the first-level folding interpolation structure.

[0041] The zero-level structure includes: a pre-amplifier array and a resistance interpolation averaging network; the first-level folded interpolation structure includes: a pre-amplifier array, a folding circuit and an interpolation network.

[0042] The zero-level structure is connected to the fi...

Embodiment 2

[0060] Such as Figure 4 As shown, it is a schematic flow chart of the decoding method of the analog-to-digital converter in the embodiment of the present invention, including the following steps:

[0061] S1: The decoding structure of this level performs folding and interpolation on the folding curve of the decoding structure of the upper level, and weights the decoding output value of the decoding structure of the upper level;

[0062] S2: Decoding and adding the weighted result to the decoding result of the decoding structure at the current level;

[0063] S3: output the added result as the output value of the decoding structure of the current level to the decoding structure of the next level, and output the folding curve after folding and interpolation to the decoding structure of the next level;

[0064] S4: Steps S1-S3 are repeated until the output value of the last decoding structure is used as the output result of the analog-to-digital converter.

[0065] The specifi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More