Optimization method designed with integrated circuit mask design and storage medium accessible to computer

A mask design and integrated circuit technology, applied in the field of optimization methods and computer-readable storage media, can solve the problems of long mask optimization time and high optimization cost, achieve fast mask optimization, accelerate optimization speed, and reduce design defects graphic effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to make the purpose, technical solutions and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the accompanying drawings and implementation examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

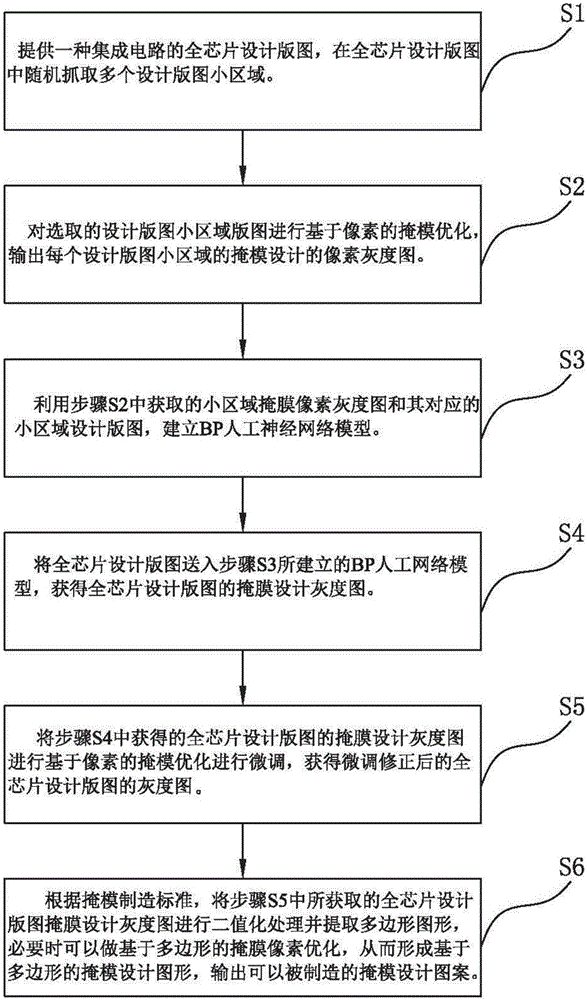

[0042] see figure 1 , The invention provides an optimization method for mask design of an integrated circuit. This embodiment is an example of the layout design of the via layer (VIA) of the 14nm node logic circuit, which can be divided into the following steps S1-S6:

[0043] Step S1: Provide a full-chip design layout of an integrated circuit, and randomly capture multiple small areas of the design layout in the full-chip design layout.

[0044] Specifically, the current large-scale integrated circuits are generally manufactured using a photolithography system. The lithography ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More