Transistor and method of forming the same

A technology of transistors and doped layers, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems affecting device performance, transistor junction leakage, etc., to improve reliability, increase distance, and avoid gate electrodes. Effects of Current and Substrate Current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] It can be seen from the background art that the transistors in the prior art have the problem of junction leakage. Now combine the structure of the transistor to analyze the cause of the junction leakage problem:

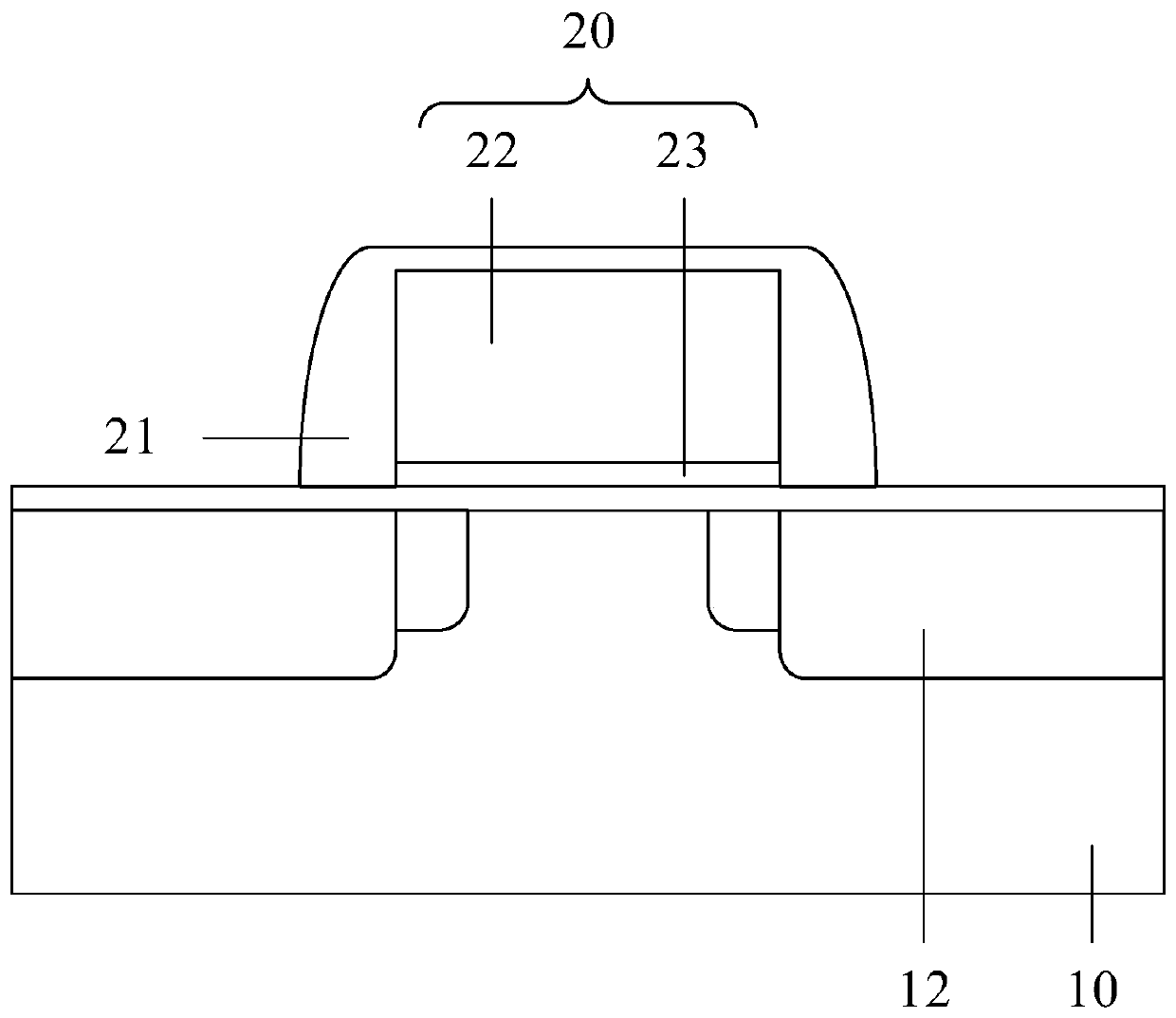

[0041] refer to figure 1 , shows a schematic structural diagram of a transistor in the prior art.

[0042] The step of forming an ultra-shallow junction transistor includes: forming a gate structure 20 on the semiconductor substrate 10, the gate structure 20 including a gate electrode 22 and a gate dielectric layer 23; doping implantation, and diffuse the implanted ions in the semiconductor substrate 10 through an annealing process; form gate spacers 21 located on the sidewalls of the gate structure 20; conduct high-energy The heavily doped is implanted to form a source region or a drain region 12 .

[0043] Due to the blocking effect of the gate spacer 21 , the region of the semiconductor substrate 10 below the gate spacer 21 is still a lightly doped regi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More