Countertop type semiconductor device and manufacturing method thereof

A manufacturing method, N-type semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reducing device reliability, affecting chips, failure, etc., achieve uniform passivation layer and achieve high performance, the effect of reducing the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the content of the present invention more clearly understood, the present invention will be further described in detail below based on specific embodiments and in conjunction with the accompanying drawings.

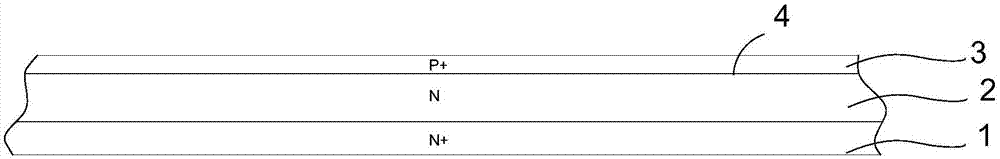

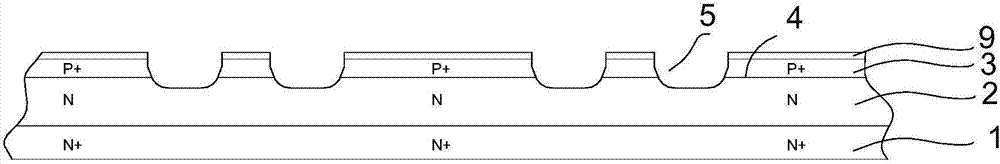

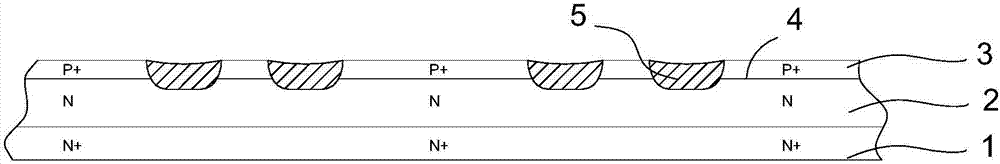

[0031] Such as Figure 5 A mesa-type semiconductor device shown includes an N+ type semiconductor substrate 1; an N type semiconductor layer 2 is bonded to the surface of the N+ type semiconductor substrate 1; a P+ type semiconductor layer 3 is bonded to the N type semiconductor The surface of the layer 2 forms a PN junction 4 together with the N-type semiconductor layer 2; the first trench 5 reaches from the surface of the P+ type semiconductor layer 3 into the N-type semiconductor layer 2; a passivation layer, Filled in the first groove 5; the second groove 6 is located between two adjacent first grooves 5; the passivation film 7 is arranged on the surface of the second groove 6; the metal layer 8. Formed on the surface of the P+ type semiconduc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More