Delta modulator and analog-to-digital converter thereof

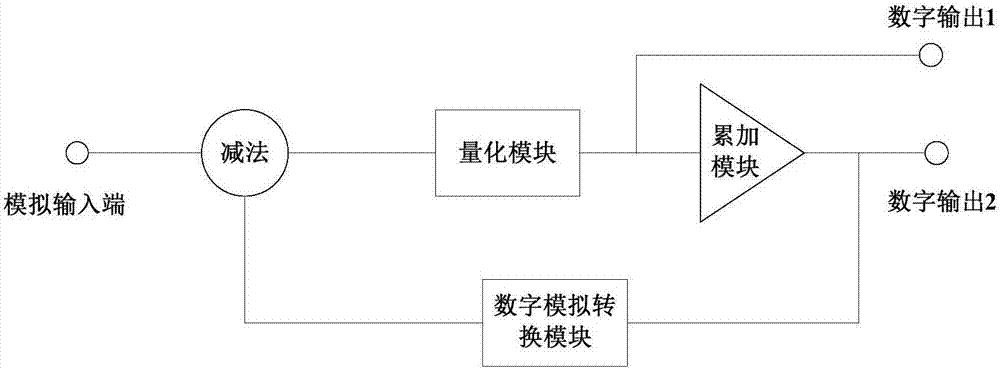

A technology of delta modulator and analog-to-digital converter, which is applied in the field of delta modulator based on successive approximation analog-to-digital converter, can solve the problems of high amplifier consumption, high total power consumption, and limitation of the use of delta modulator, etc., to achieve Effects of area reduction and power consumption reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

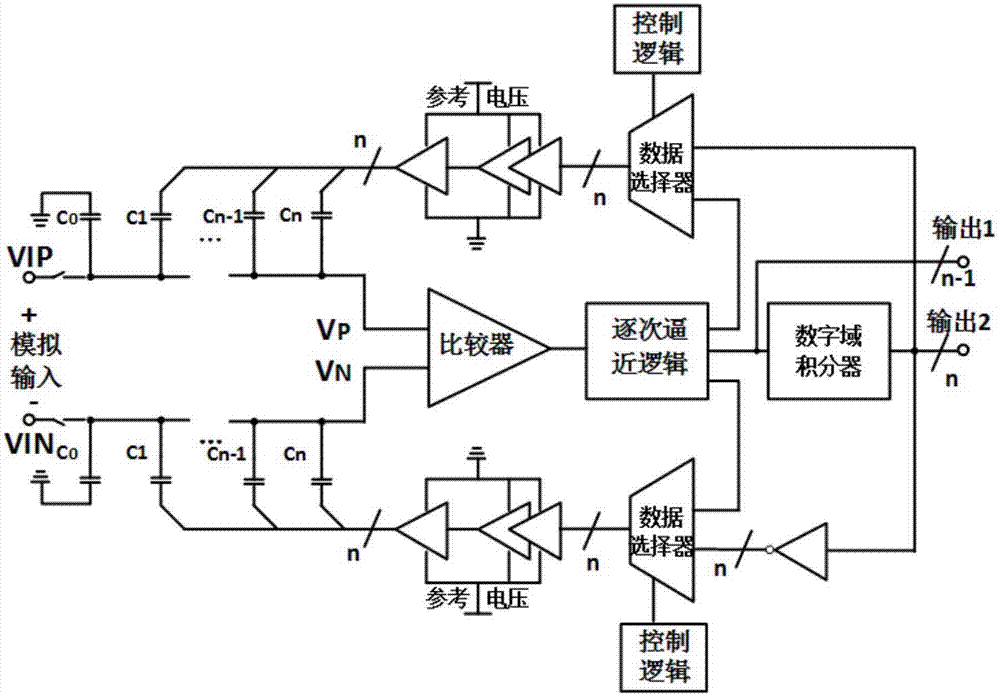

[0040] This embodiment provides a Δ modulator, including an input terminal, a conversion module, a control module, an accumulation module and an output terminal, wherein the conversion module is a monotonic capacitive switching successive approximation analog-to-digital converter (SAR ADC), and its structural diagram is as follows Figure 3a As shown, it includes: two sets of capacitor arrays with n+1 capacitors, two sets of n reverse switches, comparators and successive approximation logic control units. The control module includes: two sets of data selectors and two sets of control logic units; the control module is set on the path from the successive approximation analog-to-digital converter to the output terminal, and the data selector selects the successive approximation logic control under the control of a certain control logic unit A set of data from the unit output and the digital integrator output is sent to the inverting switch. The accumulation module is a digital d...

example 2

[0050] Such as Figure 4a shown in Figure 3a On the basis of the shown Δ modulator, a decoding circuit is added, and the number of capacitor array capacitors and the number of reverse switches in the converter are reduced by one, so that the area of the capacitor array is reduced by 50%, and the power consumption is also reduced by 50%. Its working process is still as Figure 5 As shown, it takes n+3 cycles to complete a conversion. The difference from mode 1 is that in period n+3, when the high bit L[n] of output signal 2 is '1', Figure 5 The implementation method (hereinafter referred to as mode 2), the upper group of data selectors selects L[n:1], and the lower group of data selectors selects logic signal '1'; when L[n] is '0' , the upper group of data selectors selects the logic signal '1', and the lower group of data selectors selects the complement of the output signal 2 (set as LC[n:1]). The upper plate of the cycle 1 capacitor array is connected to the analog i...

Embodiment 1

[0055] The working process of the delta modulators in Embodiment 1 and Embodiment 2 is divided into a sampling stage, a subtraction (subtraction) stage, a conversion (quantization) stage and an accumulation stage. There are two ways of working in the conversion stage: one is that under Nyquist sampling, SARADC starts to convert from the corresponding high-level capacitor; the other is that under a certain oversampling rate, SAR ADC can skip the high-level capacitor according to the oversampling rate . For example, when there is 8 times oversampling, it can be obtained from Figure 3a , Figure 3b with Figure 3c Cn-1 starts converting from Figure 4a , Figure 4b with Figure 4c Cn-2 starts conversion, which reduces a cycle and improves the conversion speed.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More