Latch circuit and semiconductor memory device

A latch circuit, oxide semiconductor technology, applied in static memory, read-only memory, information storage and other directions, can solve the problems of large circuit size, large current consumption, inability to achieve high-speed operation, etc., to achieve small circuit size and current consumption. small effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0106] Hereinafter, embodiments of the present invention will be described with reference to the drawings. In addition, in each of the following embodiments, the same reference numerals are attached to the same components.

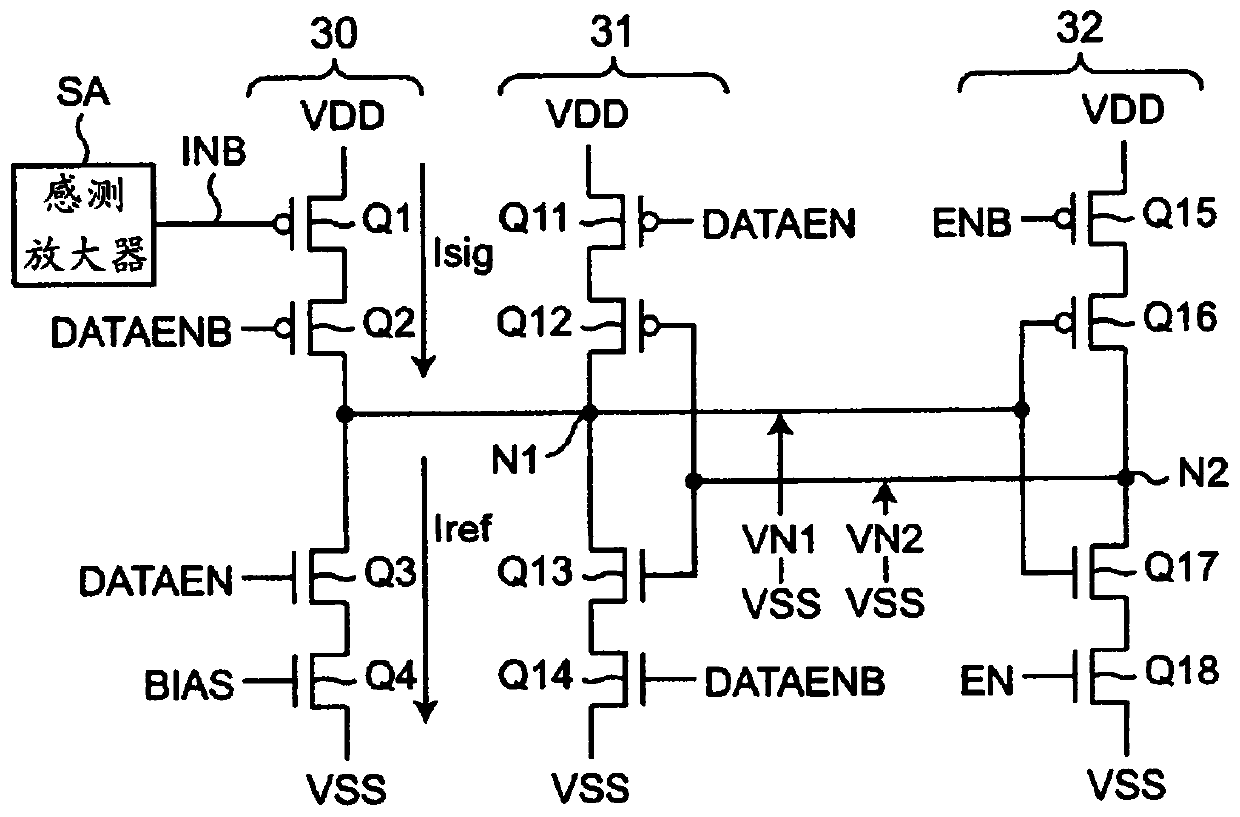

[0107] Figure 5 It is a circuit diagram showing a circuit configuration of a latch circuit of a flash EEPROM according to an embodiment of the present invention. Figure 5 The latch circuit compared to image 3 The latch circuit is different in the following respects.

[0108] (1) The reset signal RST is applied to the gate of the NMOS transistor Q3 instead of the data enable signal DATAEN.

[0109] (2) An NMOS transistor Q15 is connected in parallel with the NMOS transistor Q14 instead of the NMOS transistor Q4 , and the NMOS transistor Q15 controls the reference current corresponding to the bias voltage BIAS.

[0110] (3) The reset signal RST is applied to the gate of the PMOS transistor Q11 instead of the data enable signal DATAEN.

[0111] (4) Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More