Gold wire bonding capacitance compensation in three-dimensional encapsulated circuit and design method of capacitance compensation

A capacitance compensation and gold wire bonding technology, applied in circuits, including printed capacitors, electrical components, etc., can solve the problems of limited improvement of microwave transmission performance, occupation of design space, etc., to reduce area and insertion loss. , the effect of increased return loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The embodiments of the present invention are described in detail below. This embodiment is implemented on the premise of the technical solution of the present invention, and detailed implementation methods and specific operating procedures are provided, but the protection scope of the present invention is not limited to the following implementation example.

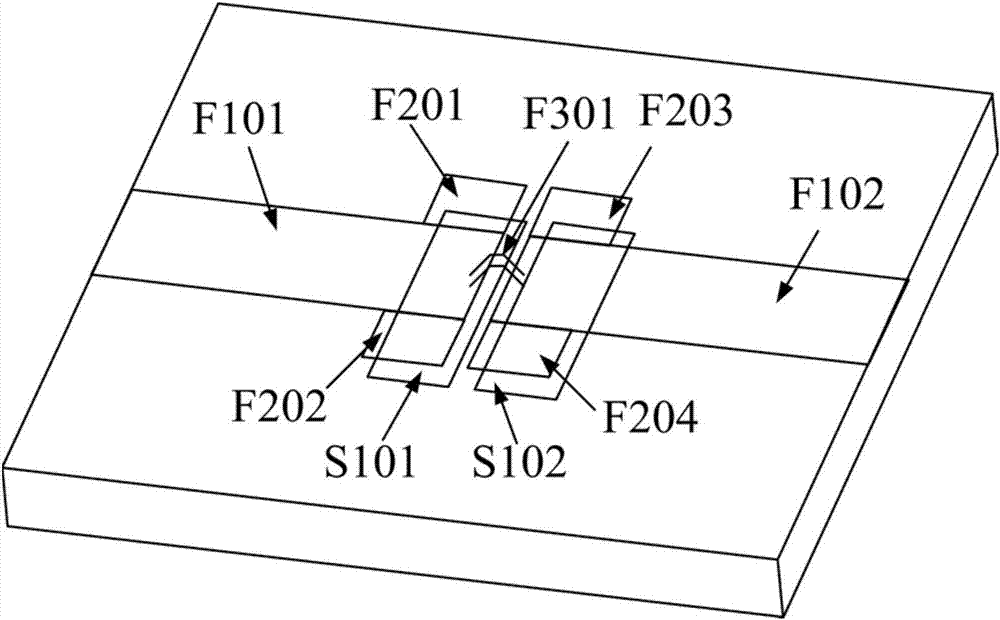

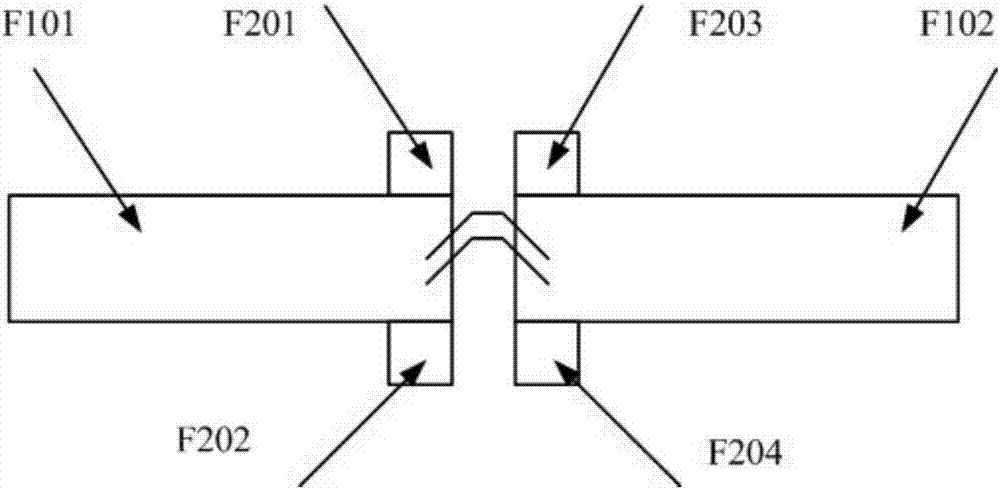

[0032] Such as figure 1 As shown, it is a three-dimensional diagram of the multilayer circuit gold wire bonding capacitance compensation design method according to the present invention, the gold wire bonding wire (F301) is connected to two 50 ohm first transmission lines (F101) and the second transmission line (F102) between. Wherein, the 50 ohm first transmission line (F101) can be an input port or an output port, correspondingly, the 50 ohm second transmission line (F102) is an output port or an input port, and the two 50 ohm first transmission lines Both (F101) and the second transmission line (F102) are in t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More