Wafer level chip scale package (WLCSP) structure with through-silicon via continuous state and manufacturing method thereof

A technology of size packaging and TSV, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, electrical components, etc., to reduce wafer size, save costs, and avoid cracking and damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

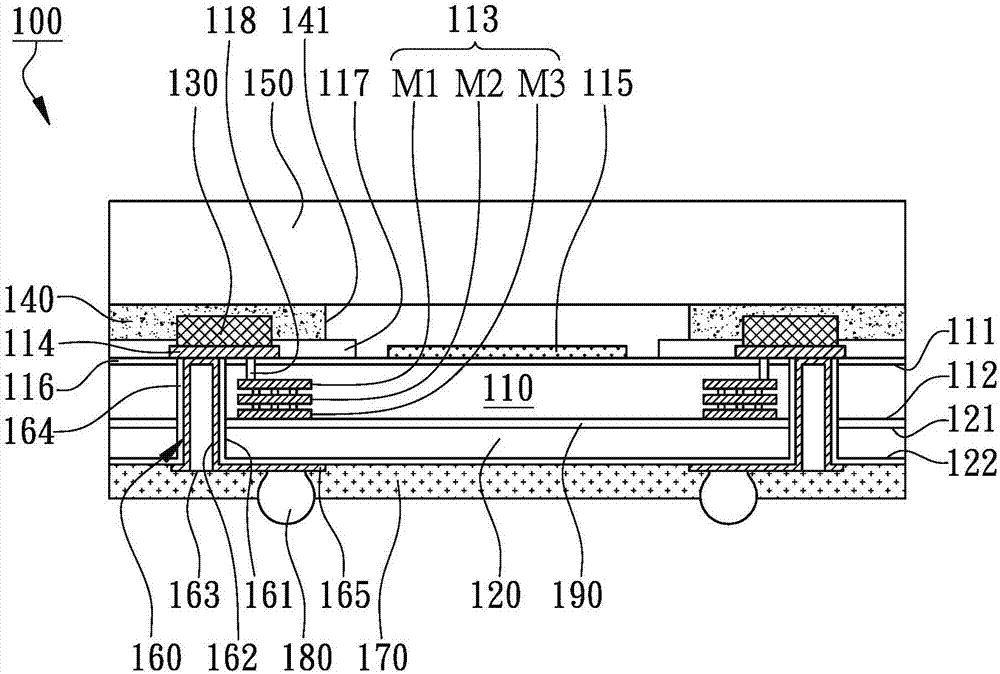

[0064] According to the first embodiment of the present invention, a TSV continuous wafer-level chip-scale packaging structure 100 is illustrated in figure 1 cross-sectional schematic diagram. The WLCSP structure 100 includes a device chip 110, a carrier chip 120, at least one spacer conductor bump 130, a spacer adhesive layer 140, a protective cover sheet 150, at least one TSV structure 160, and a protective layer. 170 and a plurality of external terminals 180.

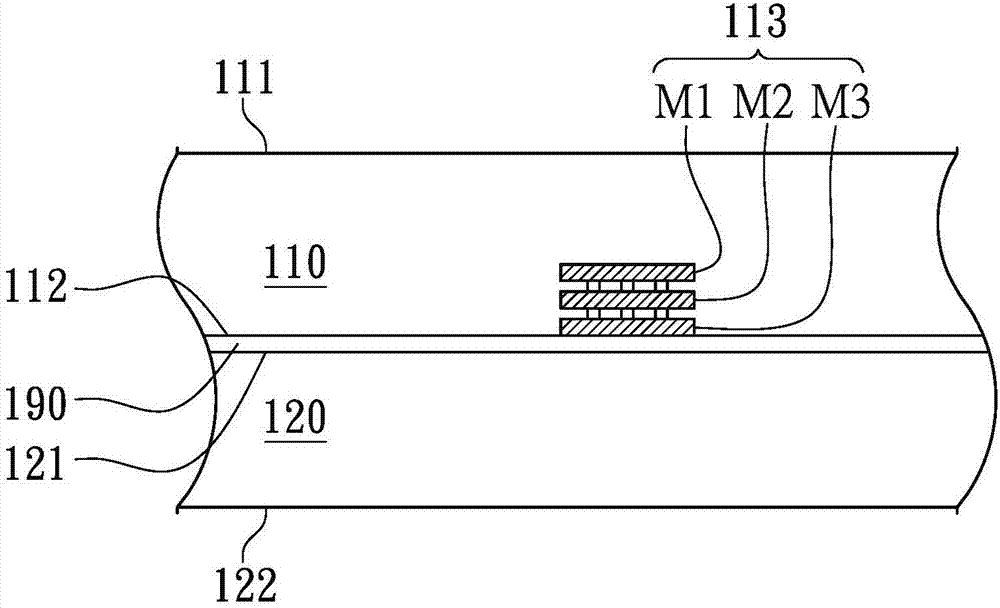

[0065] see figure 1 , the main body of the device chip 110 has a first surface 111 and a second surface 112; usually the main body of the device chip 110 is a semiconductor material layer, such as monocrystalline silicon, on the first surface 111 of the device chip 110 can be An insulating layer 116 is formed. A metal interconnect parallel pad assembly 113 is embedded in the device wafer 110, at least one offset pad 114 is disposed on the first surface 111 and connected to the metal interconnect parallel pad assem...

no. 2 Embodiment

[0085] According to the second embodiment of the present invention, another WLCSP structure 200 with TSV continuous type is described in image 3 A cross-sectional schematic diagram of , wherein the components corresponding to the same names and functions of the first specific embodiment are represented by the same component figure numbers of the first specific embodiment, and the same detailed features will not be repeated. The WLCSP structure 200 includes a device chip 110, a carrier chip 120, at least one spacer conductor bump 230, a spacer adhesive layer 140, a protective cover sheet 150, at least one TSV structure 160, and a protective layer. 170 and a plurality of external terminals 180.

[0086] see image 3 The main body of the device chip 110 has a first surface 111 and a second surface 112 , wherein a metal interconnect parallel pad assembly 113 is embedded in the device chip 110 . At least one offset pad 114 is disposed on the first surface 111 and connected to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com