ESD protection circuit structure of silicon-gate MOS integrated circuit

An ESD protection, integrated circuit technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of high electrostatic voltage and energy of chips, large secondary protection area, and high resistance requirements, and achieve good electrostatic discharge effect and protection. circuit, the effect of reducing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

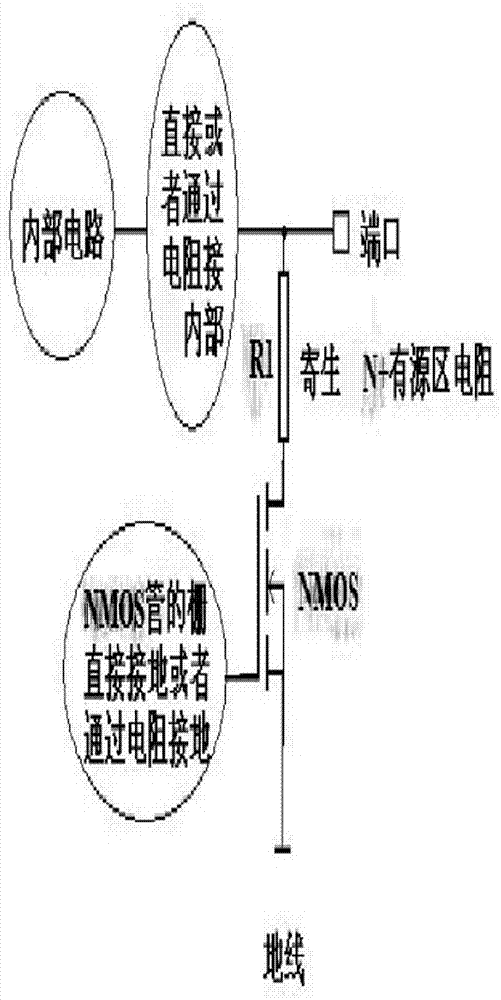

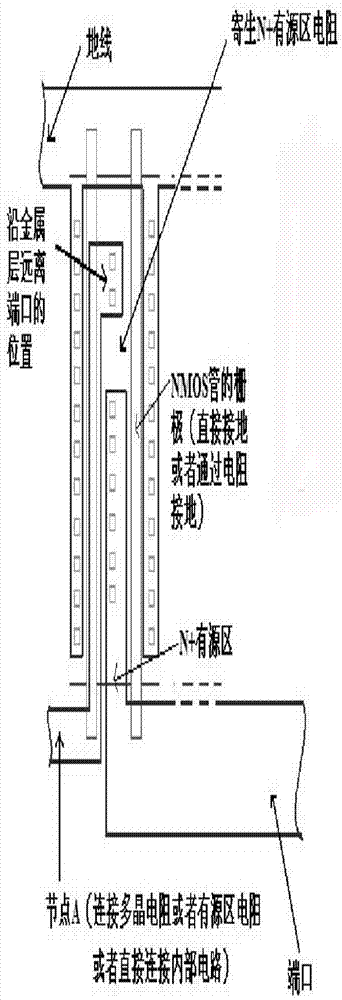

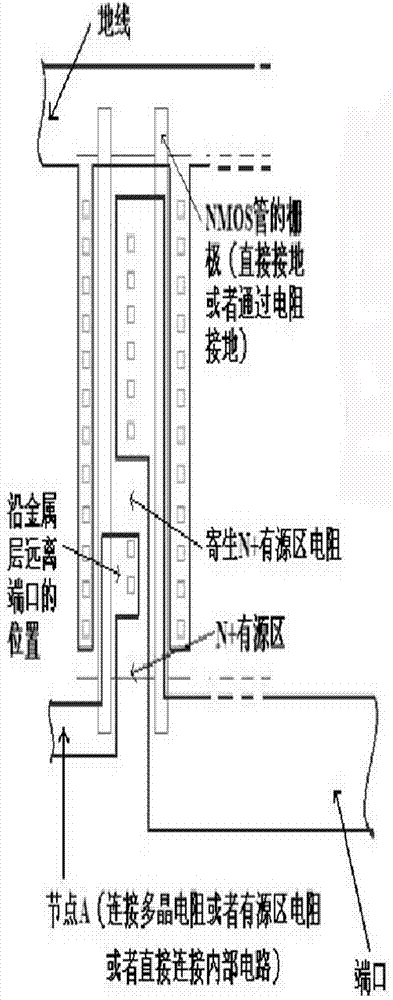

[0021] Such as figure 2 , image 3 , Figure 4 As shown, take a multi-fingered NMOS transistor with a common drain (drain connected to the port) and two NMOS transistors, along the metal layer, use the N+N type active area injection resistance parasitic in the NMOS at a position away from the port , to ensure that most of the static electricity is first discharged through the multi-fingered NMOS tube, and then directly connected to the internal circuit through the parasitic N-type active area injection resistor in the NMOS or through the polycrystalline resistor or the active area resistor.

[0022] The invention not only reduces the area of the integrated circuit layout by setting the N-type active area injection resistor on the NMOS tube, but also ensures that most of the static electricity is first discharged through the NMOS tube, and then injected into the resistor through the N-type active area. Connected to the internal circuit, the electrostatic discharge effect i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More